HMC-C062 50 Gbps, 1:2 Fanout Buffer Module

The HMC-C062 is a double edge triggered D-type Flip- Flop (DETDFF) designed to support data transmission rates of up to 50 Gbps. The device operates at half the sampling frequency of the applied data rate. The maximum clock rate is 25 GHz for 50 Gbps input data. The clock input is broadband from DC to 25 GHz. During normal operation, data is transferred to the outputs on both the positive edge and the negative edge of the clock. All input signals to the HMC-C062 are terminated with 50 Ohms to ground on-chip, and may be either AC or DC coupled. The differential outputs of the HMC-C062 may be either AC or DC coupled. Outputs can be connected directly to a 50 Ohm to ground terminated system, while DC blocking capacitors may be used if the terminating system is 50 Ohms to a non-ground DC voltage. The HMC-C062 operates from a single -3.3V DC supply, and is housed in a hermetically sealed module with 1.85mm connectors.

技术特性

- Supports Data Rates up to 50 Gbps

- Supports Clock Frequencies up to 30 GHz

- Inputs Terminated Internally in 50 ohms

- Supports Single-Ended or Differential Operation

- Very Low Power Consumption: 455 mW

- Less than 200 fs Additive RMS Jitter

- Fast Rise and Fall Times: <11ps

- Single -3.3V Power Supply

- Hermetically Sealed Module:

1.85mm connectors

- -40 to +70 °C Operating Temperature

HMC-C062 产品实物图

订购信息 Ordering Information

|

技术指标

Data/

Clock Rate (Gbps/GHz) |

Function |

Rise/Fall Time

(ps) |

Diff. Output Swing (Vp-p) |

DC Power Consumption (mW) |

DC Power Supply (Vdc) |

Package |

| 50 / 30 |

1:2 Fanout Buffer |

9.5 / 11 |

0.5 |

455 |

-3.3 |

C-13 |

应用领域 APPLICATION

- OC-768 and SDH STM-256 Equipment

- Serial Data Transmission

up to 50 Gbps

- Short, intermediate, and long haul fiber optic applications

- Broadband Test and Measurement

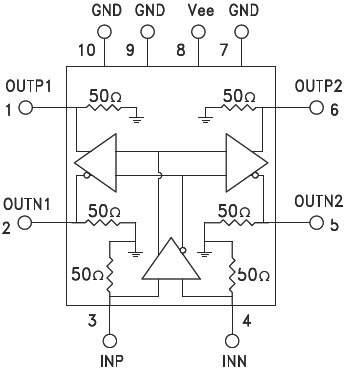

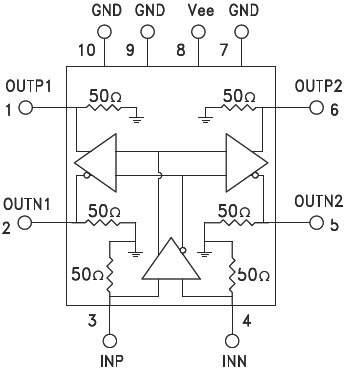

功能框图 Functional Block Diagram

|