## Advanced Monolithic Systems

### **AMS2027**

#### SINGLE POWER DISTRIBUTION SWITCH

# RoHS compliant PRELIMINARY INFORMATION

#### **FEATURES**

- 110mΩ Typical (5V Input) High Side MOSFET Switch

- Short Circuit Protection

- Logic Overcurrent Output Error Flag

- Logic Undervoltage Output Error Flag

- Logic Overheat Output Error Flag

- Enable Input Compatible With 3V and 5V Logic

- Controlled Rise and Fall Times Limit Current Surges and Minimize EMI

- Undervoltage Lock-Out Guarantees the Switch is Off At Start-up

- 100µA Maximum On-State Supply Current

- Available Active-High or Active-Low Enable

- Available in Space Saving 8 lead SOIC and 8 Lead PDIP

#### APPLICATIONS

- USB Power Management

- Hot Plug-In Power Supplies

- Battery-Charger Circuits

#### PRODUCT DESCRIPTION

The AMS2027 is a power distribution switch intended for application where heavy capacitive loads and short-circuits are likely to be encountered. The high-side switch is a  $110 \text{m}\Omega$  N-channel MOSFET. The switch is controlled by a logic enable input compatible with 3V and 5V logic and is available in active-high or active-low enable. The internal charge pump, designed to control the power switch rise and fall time to minimize current surges during switching, also provides the gate drive. Requiring no external components the charge pump allows operation from supplies as low as 3.3V. When an overload or a short circuit is encountered the AMS2027 limits the output current to a safe level by switching into a constant-current mode and the overcurrent logic output error flag is set to a low. The power dissipation in the switch will be increased by continuous heavy overloads and short circuits; this will cause the junction temperature to rise. The thermal protection circuit shuts the power switch off to prevent damage. Once the device has cooled sufficiently, it will turn on automatic. An under voltage lock-out is provided to insure that the power switch is in the Off state at start-up.

The AMS2027 is offered in the 8 lead SOIC package and the 8 lead PDIP package and is rated operational over a -40°C to 85°C temperature range.

#### ORDERING INFORMATION

| PACKA       | OPER. TEMP  |               |

|-------------|-------------|---------------|

| 8 LEAD SOIC | 8 LEAD PDIP | RANGE         |

| AMS2027S    | AMS2027P    | -40°C to 85°C |

#### PIN CONNECTIONS

8 LEAD SOIC/ 8LEAD PDIP

**ABSOLUTE MAXIMUM RATINGS** (Note 1)

Input Voltage Range, V<sub>I</sub> -0.3V to 7V Internal Power Dissipation (Note 3) Internally Limited Output Voltage Range, Vo -0.3V to  $V_{\text{I(IN)}}$ Maximum Junction Temperature +125°C

+0.3V

Input Voltage Range, V<sub>I</sub> at /EN -0.3V to 7V Storage Temperature -65°C to +150°C 265°C

Continuos Output Current, Io Lead Temperature (Soldering 25 sec)

#### **ELECTRICAL CHARACTERISTICS**

Electrical Characteristics at  $T_J=25$ °C,  $V_{I(IN)}=5.5V$ ,  $I_O=$ rated current, /EN=0V unless otherwise specified.

| PARAMETER                                         | CONDITIONS (Note 2)                                                                                     | AMS2027<br>Min. Typ. Max. |       |     | Units |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------|-------|-----|-------|

| Switch On-State Resistance                        | $V_{I(IN)} = 5.5V$                                                                                      |                           | 75    | 95  | mΩ    |

|                                                   | $V_{I(IN)} = 5.0V$                                                                                      |                           | 80    | 95  | mΩ    |

|                                                   | $V_{I(IN)} = 4.5V$                                                                                      |                           | 90    | 110 | mΩ    |

|                                                   | $V_{I(IN)} = 4.0V$                                                                                      |                           | 96    | 110 | mΩ    |

| Switch Output Leakage Current                     | $/EN = V_I$                                                                                             |                           | 0.01  | 5   | μΑ    |

|                                                   | $/EN = V_I$ , $-40$ °C $\le T_J \le 85$ °C                                                              |                           |       | 10  | μΑ    |

| Switch Output Rise Time                           | $V_{I(IN)} = 5.5V, C_L = 1 \mu F$                                                                       |                           | 4.0   |     | ms    |

|                                                   | $V_{I(IN)} = 2.7V, C_L = 1 \mu F$                                                                       |                           | 3.8   |     | ms    |

| Switch Output Fall Time                           | $V_{I(IN)} = 5.5V, C_L = 1 \mu F$                                                                       |                           | 3.9   |     | ms    |

|                                                   | $V_{I(IN)} = 2.7V, C_L = 1 \mu F$                                                                       |                           | 3.5   |     | ms    |

| Enable High-Level Input<br>Voltage                | $4.0V \le V_I \le 5.5V$                                                                                 | 2.4                       |       |     | V     |

| Enable Low-Level Input Voltage                    | $4.0V \le V_1 \le 5.5V$                                                                                 |                           |       | .06 | V     |

| Enable Input Current                              | $/EN = 0V$ or $/EN = V_I$                                                                               | -1.0                      |       | 1.0 | μА    |

| Enable Delay Time, Low-to-                        | $C_L = 1 \mu F$                                                                                         |                           |       | 20  | ms    |

| High Output                                       | $C_L = 1 \mu F$                                                                                         |                           |       | 40  | ms    |

| Short Circuit Current                             | V <sub>I(IN)</sub> = 5.5V, T <sub>J</sub> =25°C  OUT Connected to GND, device enable into short circuit | 0.66                      | 1.2   | 1.8 | A     |

| Supply Current, Low-Level                         | $/EN = V_I, T_J=25^{\circ}C$                                                                            |                           | 0.015 | 10  | μΑ    |

| Output                                            | $/EN = V_I$ , $-40$ °C $\le T_J \le 85$ °C                                                              |                           |       | 10  | μΑ    |

| Supply Current, High-Level                        | $/EN = 0V$ , $T_J=25$ °C                                                                                |                           | 73    | 100 | μΑ    |

| Output                                            | $/EN = 0V$ , $-40$ °C $\leq T_J \leq 85$ °C                                                             |                           |       | 100 | μΑ    |

| Undervoltage lock-out Low-<br>Level Input Voltage |                                                                                                         | 2.0                       | 3.0   | 3.2 | V     |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: To ensure constant junction temperature, low duty cycle pulse testing is used; thermal effects must be taken in consideration separately.

Note 3: The Power Dissipation for the SO-8 package is 725mW at T<sub>A</sub> = 25 °C. Above T<sub>A</sub> = 25 °C the Power Dissipation must be derated at 5.8mW/ °C (for T<sub>A</sub> = 70 °C  $P_D$  = 464mW; for  $T_A$  = 125 °C  $P_D$  = 145mW)

#### RECOMENDED OPERATING CONDITIONS:

|                                           | Min   | Max    |

|-------------------------------------------|-------|--------|

| Input Voltage, V <sub>I</sub>             | 4.0V  | 5.5V   |

| Input Voltage, V <sub>I</sub> at /EN      | 0V    | 5.5V   |

| Continuous Output Current, I <sub>O</sub> | 0A    | 0.6A   |

| Operating Junction Temp. Range            | -40°C | +125°C |

Advanced Monolithic Systems, Inc.

#### PIN FUNCTIONS

| Pin        | Name  | Pin No. | I/O | Description                                                |

|------------|-------|---------|-----|------------------------------------------------------------|

| Enable     | /EN   | 1       | I   | Enable Input, Logic turns power switch on.                 |

| Ground     | GND   | 3       | I   | Ground.                                                    |

| Input      | IN    | 7       | I   | Power switch input, also supplies IC's internal circuitry. |

| Error Flag | ERROR | 2       | О   | Overcurrent, Over temperature, Logic output.               |

| Output     | OUT   | 6,8     | О   | Power switch output.                                       |

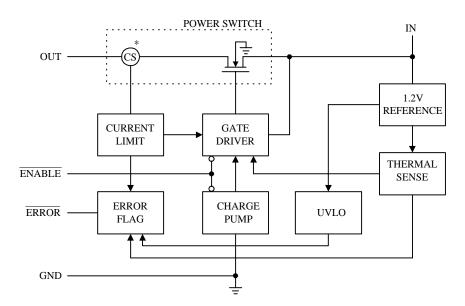

#### **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

#### **Power Switch**

The power switch is an N-channel MOSFET with a maximum on-state resistance of  $140m\Omega$  ( $V_{\rm I(IN)}=5.0V,$  configured as a high-side switch.

#### **Charge Pump**

An internal 100kHz charge pump supplies the power to the driver circuit and provides the required voltage to pull the gate of the MOSFET above the source. The charge pump requires very little supply current and operates from input voltages as low as 3.3V.

#### **Gate Driver**

The driver controls the gate voltage of the power switch. The driver incorporates circuitry that controls the rise and fall times of the output voltage, as a result it limits large current surges and reduces the associated electromagnetic interference (EMI) produced. The rise and fall times of the output voltage are typically in the 2ms to 4ms range instead of the microsecond or nanosecond range for a standard FET.

#### Enable

A logic high on the /EN input turns off the power switch and the bias for the charge pump, driver, and other circuitry to reduce the supply current to less than  $10\mu A$ . A logic zero input restore bias to the drive and control circuits and turns the power on. The enable input is compatible with both TTL and CMOS logic levels.

#### **Error Flag**

The error flag output, is an open drain logic output that is active low when output current exceeds current limit. Until the fault condition is removed the output will remain active low.

#### **Current Limit**

A sense FET monitors the current supplied to the load. In case of an overload or short circuit, the current limit circuitry sends a signal to the driver. The driver will then reduce the gate voltage and drive the power FET into its linear region, which switches the output into a constant current mode and holds the current constant while varying the voltage on the load.

#### Thermal Shutdown

The internal thermal shutdown circuit will shut the power switch off when the junction temperature rises to approx. 180°C. Hysterisis is build into the thermal sense circuitry, and after the junction temperature has dropped about 20°C, the switch turns back on. Until the fault is removed the switch will continue to cycle off and on.

#### **Undervoltage Lock-out**

An internal voltage sense monitors the input voltage. When the input voltage is below 3.2V nominal, the switch is turned off by a control signal. The typical fall time range due to the sense of a low voltage is  $250\mu s$  to  $750\mu s$ .

<sup>\*</sup>Current Sense

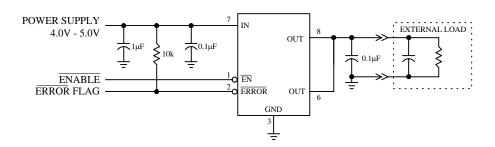

#### **APPLICATION HINTS**

#### **Power Supply Considerations**

A  $0.047\mu F$  ceramic bypass capacitor close to the device, between input and ground is recommended. When the output load is heavy or has large paralleled capacitors, a high value electrolytic capacitor should be used. To improve the immunity of the device to ESD, use a  $0.1\mu F$  ceramic capacitor to bypass the output.

#### **Current Limit**

A sense FET monitors overcurrent conditions. When an overcurrent condition is detected the device maintains a constant output current and decreases the voltage accordingly. If the condition is present long enough to activate the thermal limiting the result is the shutdown of the device.

There are three situation in which overload can occur. In the first case, the output has been shorted before the device is enabled or before  $V_{\rm I}$  has been applied. The device senses the short and switches into a constant-current output.

In the second case, the short occurs while the device is enabled. When this happens, very high currents flow for a short time before the current-limit circuit can react. After the current-limit circuit has tripped, the device limits normally.

In the third case, the load has been gradually increased beyond the recommended operating current. The current will rise until the current-limit threshold is reached. The AMS2027 is able to deliver current up to the current-limit threshold without damage. When the threshold has been reached the device switches into the constant current mode. When over current condition is detected the error flag logic output remains low until the condition is removed.

#### **Power Dissipation and Junction Temperature**

The thermal resistance of the surface-mount packages such as SOIC is high compared to that of power packages. The use of the N-cannel MOSFET which has low on-resistance, makes it possible for small surface-mount packages to pass large currents. To determine the power dissipation and junction temperature the first step is to find  $r_{\rm ON}$  at the input voltage and operating temperature.

As an initial estimate use the highest operating ambient temperature of interest and read  $r_{ON}$  from Figure 1. Power dissipation is equal to:

$$P_D = r_{ON} \times I^2$$

Calculate the junction temperature:

$$T_J = P_D \; X \; R_{\theta JA} + T_A$$

Where  $R_{\theta JA}$  is the thermal resistance and is 172°C/W for the SOIC package. Compare the calculated junction temperature with the initial estimate and if they don't mach within a few degrees, repeat the calculations using the calculated value as the new estimate. A few repetitions will be sufficient to give a reasonable answer.

#### **Thermal Protection**

Thermal protection prevents damage to the device when over load or short circuits conditions are present for extended periods of time. These conditions force the AMS2027 into the constant current mode. As a result the voltage across the high-side switch will increase. Under short-circuit conditions the voltage across the switch is equal to the input voltage. Continuous heavy over loads and short circuits increase the power dissipation in the switch and causes the junction temperature to rise to dangerously high levels. The protection circuit shuts off the switch when it senses the high junction temperature. The switch remains off until the device has cooled about 20°C. The switch continues to cycle off and on until the fault is removed.

#### **Undervoltage Lock-out**

An undervoltage lock-out is provided to insure that the switch is in the off state at start-up. When the input voltage falls below 3.2V the switch will be turned off immediately. This will make it easy for designers of hot plug-in systems that may not be able to turn the switch off before removing the input power. In such cases when the device is reinserted, the turn on will have a controlled rise time to reduce EMI and voltage overshoots.

TYPICAL APPLICATIONS

Figure 1

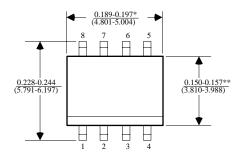

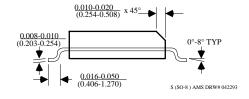

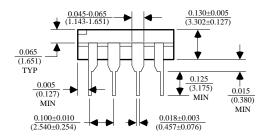

#### PACKAGE DIMENSIONS inches (millimeters) unless otherwise noted.

#### 8 LEAD SOIC PLASTIC PACKAGE (S)

\*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

\*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED  $0.010^\circ\ (0.254\text{mm})$  PER SIDE

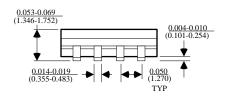

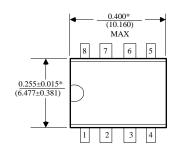

#### 8 LEAD PLASTIC DIP PACKAGE (P)

P (8L PDIP) AMS DRW# 042294