# 50mA Low-Noise Ultra Low-Dropout CMOS Regulator with Fault Indicator

#### DESCRIPTION

The EUP7182 low-noise, low-dropout, linear regulator operates from a 2.5V to 5.5V input and is guaranteed to deliver 50mA.

The EUP7182 is stable with small  $1\mu F$  ceramic capacitor. Its performance suits battery powered applications because of its shutdown mode (60 nA typ), low quiescent current (110 $\mu A$  typ), and LDO voltage (110mV typ). The low dropout voltage allows for more utilization of a battery's available energy by operating closer to its end-of-life voltage. An output fault-detection circuit indicates loss of regulation.

The EUP7182 is available in SOT23-6 package with 1.8V, 2.5v, 2.8V, 3V and 3.3V versions.

#### **FEATURE**

- 2.5V to 5.5V Input Range

- 50mA Guaranteed Output Current

- 60dB PSRR at 1kHz

- 50μV RMS Output Voltage Noise (10Hz to 100kHz)

- 110mV Dropout at 50mA

- Low 110μA No-Load Supply Current

- ≤1µA Shutdown Current

- Fast Start-up Time

- Stable With 1μF Ceramic Output Capacitors

- Thermal Shutdown and Short-Circuit Protection

- Fault Indicator

- RoHS Compliant and 100% Lead (Pb)-Free

#### **APPLICATIONS**

- Wireless Handsets

- Battery Powered Electronics

- Portable Information Appliances

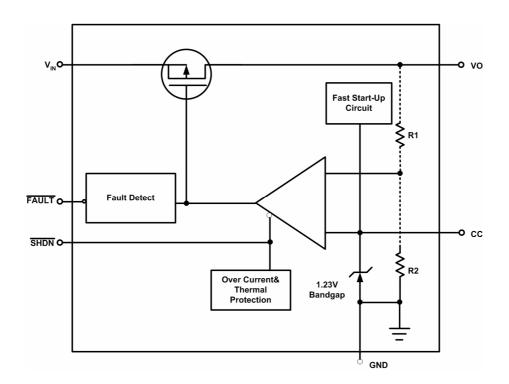

#### **Block Diagram**

Figure 1.

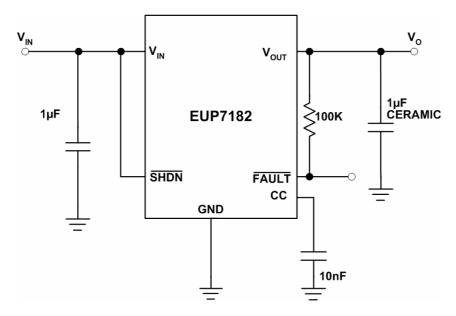

## **Typical Application Circuit**

Figure 2. Fixed Voltage LDO Regulator

## **Pin Configurations**

| Package Type | Pin Configurations                        |  |  |

|--------------|-------------------------------------------|--|--|

| SOT23-6      | VOUT CC FAULT  6 5 4  1 2 3  VIN GND SHDN |  |  |

### **Pin Description**

| PIN   | PIN                                                                                                                                                                    | DESCRIPTION                                                   |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| VIN   | 1                                                                                                                                                                      | Input voltage of the LDO                                      |  |  |  |

| GND   | 2                                                                                                                                                                      | Common Ground                                                 |  |  |  |

| SHDN  | 3                                                                                                                                                                      | SHDN places the entire device in shutdown mode when held low. |  |  |  |

| FAULT | FAULT  Fault output. A high-impedance, open-drain output. If the circuit regulation, FAULT goes low. In shutdown, this pin is high Impedance. Connect to GND if unused |                                                               |  |  |  |

| CC    | 5                                                                                                                                                                      | Compensation capacitor for noise reduction                    |  |  |  |

| VOUT  | 6                                                                                                                                                                      | Output voltage of the LDO                                     |  |  |  |

EUTECH

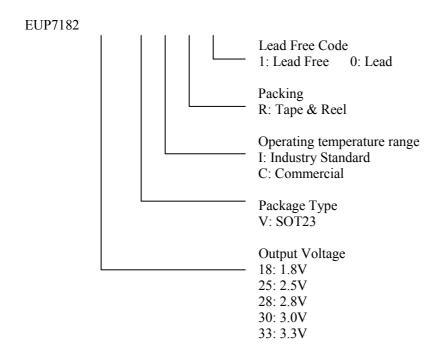

## **Ordering Information**

| Order Number   | Package Type | Marking | Operating Temperature range |

|----------------|--------------|---------|-----------------------------|

| EUP7182-18VIR1 | SOT23-6      | mDxxxx  | -40°C to 85°C               |

| EUP7182-25VIR1 | SOT23-6      | mBxxxx  | -40°C to 85°C               |

| EUP7182-28VIR1 | SOT23-6      | mExxxx  | -40°C to 85°C               |

| EUP7182-30VIR1 | SOT23-6      | mGxxxx  | -40°C to 85°C               |

| EUP7182-33VIR1 | SOT23-6      | mHxxxx  | -40°C to 85°C               |

## **Absolute Maximum Ratings**

| • | $V_{IN}, V_{OUT}, V_{\overline{SHDN}}, V_{CC}, V_{\overline{FAULT}}$ | V to 6V |

|---|----------------------------------------------------------------------|---------|

| • | Fault Sink Current                                                   | 20mA    |

| • | Storage Temperature Range                                            | o 160°C |

|   | Junction Temperature (TJ)                                            | 150°C   |

| • | Lead Temperature (10 sec.)                                           | 260°C   |

#### **Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $V_{IN} = V_O + 0.5V$ ,  $V_{SHDN} = V_{IN}$ ,  $C_{IN} = C_{OUT} = 1 \mu F$ ,  $C_{CC} = 10 n F$ ,  $T_J = 25 ^{\circ}C$ . (Boldface limits apply for the operating temperature extremes: -40  $^{\circ}C$  and 85  $^{\circ}C$ )

| Crumbal            | Danamatan                                                                                                                                                            | Conditions                                                                  | EUP7182 |                      |                   | T I 24                |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|----------------------|-------------------|-----------------------|--|

| Symbol             | Parameter                                                                                                                                                            | Conditions                                                                  | Min     | Тур                  | Max.              | Unit                  |  |

| $V_{\rm IN}$       | Input Voltage                                                                                                                                                        |                                                                             | 2.5     |                      | 5.5               | V                     |  |

| $\Delta V_{\rm O}$ | Output Voltage Tolerance                                                                                                                                             | $100\mu\text{A} \le I_{\text{OUT}} \le 50\text{mA}$                         | -2      |                      | +2                | % of                  |  |

|                    |                                                                                                                                                                      | $V_{IN} = V_O + 0.5V$ ,                                                     | -3      |                      | +3                | V <sub>OUT(NOM)</sub> |  |

| I <sub>O</sub>     | Maximum Output Current                                                                                                                                               | Average DC Current Rating                                                   | 50      | 7.5                  | 100               | mA                    |  |

| $I_{LIMIT}$        | Output Current Limit Supply Current                                                                                                                                  | I <sub>OUT</sub> =0mA                                                       |         | 75<br>110            | 100<br><b>200</b> | mA<br>                |  |

| $I_{Q}$            | ***                                                                                                                                                                  |                                                                             |         | 1                    |                   | μA                    |  |

|                    | Shutdown Supply Current                                                                                                                                              | $V_O = 0V$ , SHDN = GND                                                     |         | 0.06                 | 1                 | μΑ                    |  |

| $V_{DO}$           | Dropout Voltage                                                                                                                                                      | I <sub>OUT</sub> =1mA                                                       |         | 1                    |                   | - mV                  |  |

| <b>V</b> DO        | Diopout voltage                                                                                                                                                      | I <sub>OUT</sub> =50mA                                                      |         | 110                  | 160               |                       |  |

| $\Delta V_{0}$     | Line Regulation                                                                                                                                                      | $I_{OUT} = 1 \text{mA}, (V_0 + 0.5 \text{V}) \le V_1$<br>$\le 5.5 \text{V}$ | -0.1    | 0.05                 | 0.1               | %/V                   |  |

|                    | Load Regulation                                                                                                                                                      | $100\mu A \leq I_{OUT} \leq 50mA$                                           |         | 0.002                |                   | %/mA                  |  |

| e <sub>n</sub>     | Output Voltage Noise                                                                                                                                                 | $I_{OUT}$ =10mA, 10Hz $\leq$ f $\leq$ 100kHz                                |         | 50                   |                   | $\mu V_{RMS}$         |  |

|                    | SHDN Input Threshold                                                                                                                                                 | $V_{IH}$ , $(VO+0.5V) \le V_I \le 5.5V$                                     | 2       |                      |                   | - V                   |  |

| VSHDN              |                                                                                                                                                                      | $V_{IL}$ , $(VO+0.5V) \le V_I \le 5.5V$                                     |         |                      | 0.4               |                       |  |

| ISHDN              | SHDN Input Bias Current                                                                                                                                              | SHDN =GND or IN                                                             |         | 0.1                  | 100               | nA                    |  |

| VFAULT             | FAULT Detection Voltage of the $V_{\text{IN}}$ -to- $V_{\text{OUT}}$ Difference (Apply for $V_{\text{OUT}} \ge 2.5 \text{V}$ and $I_{\text{OUT}} \le 15 \text{mA}$ ) | I <sub>OUT</sub> =10mA                                                      |         | 25                   | 40                | mV                    |  |

| VIAULI             | FAULT Detection Threshold of the Output Voltgae                                                                                                                      |                                                                             |         | $0.8 \times V_{OUT}$ |                   | V                     |  |

|                    | FAULT Output Low Voltage                                                                                                                                             | I <sub>SINK</sub> =2mA                                                      |         | 0.13                 | 0.25              | V                     |  |

| IFAULT             | FAULT Off-Leakage Current                                                                                                                                            | FAULT =3.6V, SHDN=0V                                                        |         | 0.1                  | 100               | nA                    |  |

| $T_{SD}$           | Thermal Shutdown Temperature                                                                                                                                         |                                                                             |         | 160                  |                   | 0.0                   |  |

|                    | Thermal Shutdown Hysteresis                                                                                                                                          |                                                                             |         | 20                   |                   | °C                    |  |

| T <sub>ON</sub>    | Start-Up Time                                                                                                                                                        | V <sub>O</sub> at 90% of Final Value                                        |         | 80                   |                   | μs                    |  |

#### **Application Information**

#### **External Capacitors**

Like any low-dropout regulator, the EUP7182 requires external capacitors for regulator stability. The EUP7182 is specifically designed for portable applications requiring minimum board space and smallest components. These capacitors must be correctly selected for good performance.

#### **Input Capacitor**

A minimum input capacitance of  $1\mu F$  is required between the EUP7182 input pin and ground (the amount of the capacitance may be increased without limit). This capacitor must be located a distance of not more than 1cm from the input pin and returned to a clean analog ground.

$1\mu F$  ceramic capacitor are fine for most end use applications. If a tantalum capacitor is used at the input, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

#### **No-Load Stability**

The EUP7182 will remain stable and in regulation with no external load. This is specially important in CMOS RAM keep-alive applications.

#### **Output Capacitance**

The EUP7182 is specifically designed to employ ceramic output capacitors as low as  $2.2\mu F$ . Ceramic capacitors below  $10\mu F$  offer significant cost and space savings, along with high frequency noise filtering. Higher values and other types and of capacitor may be used, but their equivalent series resistance (ESR) should be maintained below  $0.5\Omega$ . Ceramic capacitor of the value required by the EUP7182 are available in the following dielectric types: Z5U, Y5V, X5R, and X7R. The Z5U and Y5V types exhibit a 50% or more drop in capacitance value as their temperature increase from 25°C, an important consideration. The X5R generally maintain their capacitance value within  $\pm$  20%. The X7R type are desirable for their tighter tolerance of 10% over temperature.

#### **Noise Bypass Capacitor**

Connecting a 33nF capacitor between the  $C_{BYPASS}$  pin and ground significantly reduces noise on the regulator output. This cap is connected directly to a high impedance node in the bandgap reference circuit. Any significant loading on this node will cause a change on the regulated output voltage. For this reason, DC leakage current through this pin must be kept as low as possible for best output voltage accuracy. The types of capacitors best suited for the noise bypass capacitor are ceramic and film.

Unlike many other LDO's, addition of a noise reduction capacitor does not effect the load transient response of the device. However, it does affect start-up time. The smaller the capacitance value, the quicker the start-up time.

#### **Power Dissipation and Junction Temperature**

Specified regulator operation is assured to a junction temperature of 125°C; the maximum junction temperature should be restricted to 125°C under normal operating conditions. This restriction limits the power dissipation the regulator can handle in any given application. To ensure the junction temperature is within acceptable limits, calculate the maximum allowable dissipation,  $P_{D(max)}$ , and the actual dissipation,  $P_D$ , which must be less than or equal to  $P_{D(max)}$

The maximum-power-dissipation limit is determined using the following equation:

$$P_{D(max)} = \frac{T_{J}max - T_{A}}{R_{\theta JA}}$$

Where

$T_J max$  is the maximum allowable junction temperature.  $R_{\theta JA}$  is the thermal resistance junction-to-ambient for the package

T<sub>A</sub> is the ambient temperature.

The regulator dissipation is calculated using:

$$P_D = (V_I - V_O) \times I_O$$

Power dissipation resulting from quiescent current is negligible. Excessive power dissipation triggers the thermal protection circuit.

#### **Fault Detection**

The EUP7182 provides a FAULT pin that goes low during out of regulation conditions like current limit and thermal shutdown, or when it approaches dropout. The latter monitors the input-to-output voltage differential and compares it against a threshold that is slightly above the dropout voltage. This threshold also tracks the dropout voltage as it varies with load current. Refer to Fault Detect vs. Load Current curve in the typical characteristics section.

The FAULT pin requires a pull-up resistor since it is an open-drain output. This resistor should be large in value to reduce energy drain. A100k $\Omega$  pull-up resistor works well for most applications.

#### Shutdown

The EUP7182 goes into sleep mode when the SHDN pin is in a logic low condition. During this condition, the pass transistor, error amplifier, and bandgap are turned off, reducing the supply current to 60nA typical. The SHDN pin may be directly tied to  $V_{\rm IN}$  to keep the part on.

#### **Fast Start-up**

The EUP7182 provides fast start-up time for better system efficiency. The start-up speed is maintained when using the optional noise bypass capacitor.

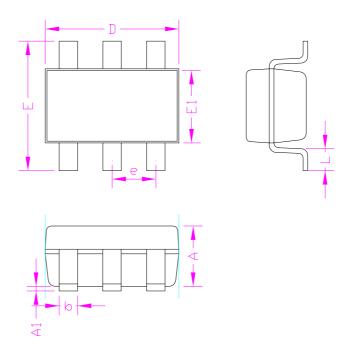

## **Packaging Information**

SOT23-6

| SYMBOLS | MILLIMETERS |      | INCHES      |       |

|---------|-------------|------|-------------|-------|

|         | MIN.        | MAX. | MIN.        | MAX.  |

| A       | -           | 1.45 | -           | 0.057 |

| A1      | 0.00        | 0.15 | 0.000 0.006 |       |

| b       | 0.30        | 0.50 | 0.012       | 0.020 |

| D       | 2.90        |      | 0.114       |       |

| E1      | 1.60        |      | 0.0         | 063   |

| e       | 0.95        |      | 0.0         | 37    |

| Е       | 2.60        | 3.00 | 0.102       | 0.118 |

| L       | 0.30        | 0.60 | 0.012       | 0.024 |