# DDR SDRAM Specification Version 1.31

### **Revision History**

Version 0 (May, 1998)

- First version for internal review

Version 0.1(June, 1998)

- Added x4 organization

#### Version 0.2(Sep,1998)

- 1. Added "Issue prcharge command for all banks of the device" as the fourth step of power-up squence.

- 2. In power down mode timing diagram, NOP condition is added to precharge power down exit.

#### Version 0.3(Dec,1998)

- Added QFC Function.

- Added DC current value

- Reduce I/O capacitance values

#### Version 0.4(Feb,1999)

- -Added DDR SDRAM history for reference(refer to the following page)

- -Added low power version DC spec

#### Version 0.5(Apr,1999)

- -Revised following first showing for JEDEC standard

- -Added DC target current based on new DC test condition

#### Version 0.6(July 1,1999)

1.Modified binning policy

From To

-Z (133Mhz) -Z (133Mhz/266Mbps@CL=2) -8 (125Mhz) -Y (133Mhz/266Mbps@CL=2.5) -0 (100Mhz) -0 (100Mhz/200Mbps@CL=2)

2. Modified the following AC spec values

|                     | Fro              | m.            | To.         |             |             |

|---------------------|------------------|---------------|-------------|-------------|-------------|

|                     | -Z               | -0            | -Z          | -Y          | -0          |

| tAC                 | +/- 0.75ns       | +/- 1ns       | +/- 0.75ns  | +/- 0.75ns  | +/- 0.8ns   |

| tDQSCK              | +/- 0.75ns       | +/- 1ns       | +/- 0.75ns  | +/- 0.75ns  | +/- 0.8ns   |

| tDQSQ               | +/- 0.5ns        | +/- 0.75ns    | +/- 0.5ns   | +/- 0.5ns   | +/- 0.6ns   |

| tDS/tDH             | 0.5 ns           | 0.75 ns       | 0.5 ns      | 0.5 ns      | 0.6 ns      |

| tCDLR <sup>*1</sup> | 2.5tCK-tDQSS     | 2.5tCK-tDQSS  | 1tCK        | 1tCK        | 1tCK        |

| tPRE*1              | 1tCK +/- 0.75ns  | 1tCK +/- 1ns  | 0.9/1.1 tCK | 0.9/1.1 tCK | 0.9/1.1 tCK |

| tRPST*1             | tCK/2 +/- 0.75ns | tCK/2 +/- 1ns | 0.4/0.6 tCK | 0.4/0.6 tCK | 0.4/0.6 tCK |

| tHZQ <sup>*1</sup>  | tCK/2 +/- 0.75ns | tCK/2 +/- 1ns | +/- 0.75ns  | +/- 0.75ns  | +/-0.8ns    |

<sup>&</sup>lt;sup>\*1</sup>: Changed description method for the same functionality. This means no difference from the previous version.

3. Changed the following AC parameter symbol

From. To.

Output data access time from CK/CK

tDQCK tAC

#### Version 0.61(August 9,1999)

- Changed the some values of "write with auto precharge" table for different bank in page 31.

| Asserted    |       | For Differ | rent Bank |         |   |   |

|-------------|-------|------------|-----------|---------|---|---|

| command     | 3     |            | and 3     |         | 4 | 1 |

|             | Old   | New        | Old       | New     |   |   |

| Read        | Legal | Illegal    | Legal     | Illegal |   |   |

| Read + AP*1 | Legal | Illegal    | Legal     | Illegal |   |   |

## **Revision History(continued)**

### Version 0.7 (March, 2000)

- Changed 128Mb spec from target to Preliminary version.

- Changed partnames as follows.

| from                   | to                       |

|------------------------|--------------------------|

| KM44L32031BT-G(L)Z/Y/0 | K4H280438B-TC(L)A2/B0/A0 |

| KM48L16031BT-G(L)Z/Y/0 | K4H280838B-TC(L)A2/B0/A0 |

| KM416L8031BT-G(L)Z/Y/0 | K4H281638B-TC(L)A2/B0/A0 |

- Changed input cap. spec.

|           | from          | to                                   |

|-----------|---------------|--------------------------------------|

| CK/CK     | 2.5pF ~ 3.5pF | 2.0pF ~ 3.0pF w/ Delta Cin = 0.25pF  |

| DQ/DQS/DM | 4.0pF ~ 5.5pF | 4.0pF ~ 5.0pF w/ Delta Cin = 0.5pF   |

| CMD/Addr  | 2.5pF ~ 3.5pF | 2.0pF ~ 3.0pF with Delta Cin = 0.5pF |

- Changed operating condition.

|                                       | from           | to             |

|---------------------------------------|----------------|----------------|

| Vil/Vih(ac)                           | Vref +/- 0.35V | Vref +/- 0.31V |

| V <sub>IL</sub> /V <sub>IH</sub> (dc) | Vref +/- 0.18V | Vref +/- 0.15V |

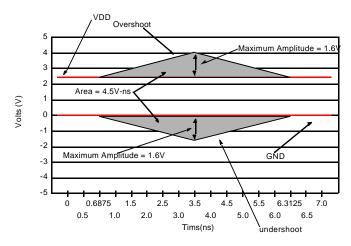

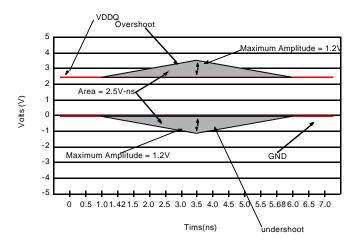

- Added Overshoot/Undershoot spec

- . Vih(max) = 4.2V, the overshoot voltage duration is  $\leq$  3ns at VDD.

- . Vil(min) =- 1.5V, the overshoot voltage duration is  $\leq$  3ns at VSS.

- Changed AC parameters as follows.

|       | from                           | to                       | Comments        |

|-------|--------------------------------|--------------------------|-----------------|

| tDQSQ | +/- 0.5(PC266), +/- 0.6(PC200) | +0.5(PC266), +0.6(PC200) |                 |

| tDV   | +/- 0.35tCK                    | -                        | Removed         |

| tQH   | _                              | tHPmin - 0.75ns(PC266)   | New Definition  |

| iQH   | -                              | tHPmin - 1.0ns(PC200)    | New Delillition |

| tHP   | -                              | tCLmin or tCHmin         | New Definition  |

- Added DC spec values.

#### Version 0.71 (April, 2000)

- Corrected a typo for tRAS at 133Mhz/CL2.5 from 48ns t0 45ns.

- Corrected a typo in "General Information" table from 64Mx4 to 8Mx16.

### Version 0.72(May,2000)

- Changed DC spec item & test condition

#### Version 0.73(June,2000)

- Added updated DC spec values

- Deleted tDAL in AC parameter

#### Version 1.0(July,2000)

- Eliminate "preliminary"

#### Version 1.1(February,2001)

- Updated DC current value.

- Changed  $V_{ID}(DC)$ , Input differential voltage, CK and  $\overline{CK}$  inputs min. from 0.3V to 0.36V.

- Added V<sub>IX</sub>(DC), Input crossing point voltage, CK and CK inputs to 1.15V ~1.35V.

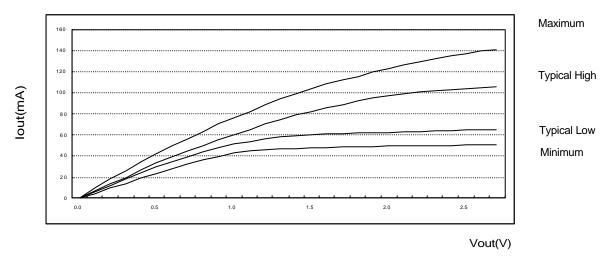

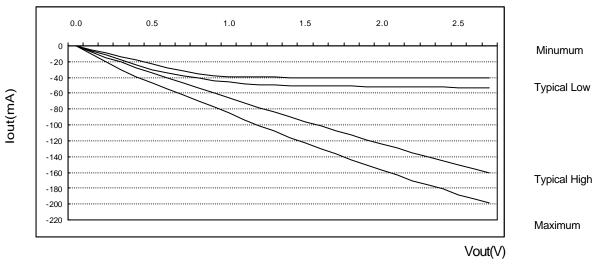

- Added Output high/low current( $I_{OH}$ , $I_{OL}$ ) for half strength driver.

- Added Pullup current to pulldown current ratio to 0.71 ~ 1.4.

- Changed  $V_{ID}(AC)$ , Input differential voltage, CK and  $\overline{CK}$  inputs min. from 0.62V to 0.7V.

- Changed tCK max from 15ns to 12ns for all speed binning.

- Changed tDQSH/tDQSL min. from 0.4tCK to 0.35tCK.

- Added tHZ/tLZ(Data-out high/Low impedence time from CK/CK)

- Added tQHS(Data hold skew factor)

#### Version 1.2(February,2001)

- Added tDSS/tDSH(DQS falling edge to/from CK rising setup/hold time)

- Added overshoot/undershoot spec

#### Version 1.21(March,2001)

- Added tSL(I), tSL(IO), tSL(O)

| Parameter | Definition                      | Valu | Unit |       |

|-----------|---------------------------------|------|------|-------|

| Tarameter | Deminion                        | Min. | Max. | Offic |

| tSL(I)    | Input Slew Rate(for input only) | 0.5  |      | V/ns  |

| tSL(IO)   | Input Slew Rate(for I/O pins)   | 0.5  |      | V/ns  |

| tSL(O)    | Output Slew Rate(x4,x8)         | 1.0  | 4.5  | V/ns  |

| tSL(O)    | Output Slew Rate(x16)           | 0.7  | 5    | V/ns  |

#### Version 1.22(March, 2001)

- Changed from supporting QFC function to not supporting QFC function(Deleted all QFC function supported)

- Changed name and specification from IDD7 to IDD7A

| Description                             | from                                      | to                                         |

|-----------------------------------------|-------------------------------------------|--------------------------------------------|

| Orerating current - Four bank operation | IDD7(50% of data changing at every burst) | IDD7(100% of data changing at every burst) |

#### Version 1.23(July,2001)

- Add derating values for the specifications if the single-ended clock skew rate is less than 1.0V/ns in page 49.

#### Version 1.24(August,2001)

-Fixed incorrect value of table in page 31, ' write with auto precharge' .

#### Version 1.3(October,2001)

- Modificated typo.

- Changed pin # 17 from NC to A13 in Package pinout.

- Revised "Write with autoprecharge" table in page 29.

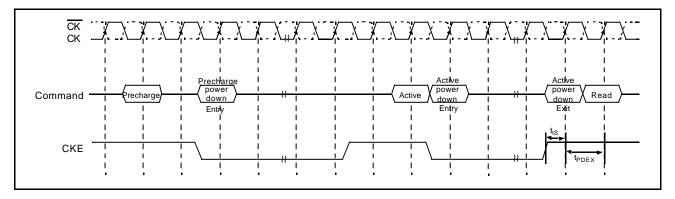

- Added tIS and tPDEX parameters in "power down" timing of page 31.

- Revised "Absolute maximum rating" table in page 38.

- . Changed "Voltage on VDDQ supply relative to VSS" value from -0.5~3.6V to -1~3.6V

- . Changed "power dissipation" value from 1.0W to 1.5W.

- Revised AC parameter table

|                |                  | From             |                  |                  |                  |                  |       | Т     | 0     | •     |      |      |

|----------------|------------------|------------------|------------------|------------------|------------------|------------------|-------|-------|-------|-------|------|------|

|                | DDR              | 266A             | DDR              | 266B             | DDF              | R200             | DDR   | 266A  | DDR:  | 266B  | DDF  | R200 |

|                | Min.             | Max.             | Min.             | Max.             | Min.             | Max.             | Min.  | Max.  | Min.  | Max.  | Min. | Max. |

| tHZ(DQ)        | tACmin<br>-400ps | tACmax<br>-400ps | tACmin<br>-400ps | tACmax<br>-400ps | tACmin<br>-400ps | tACmax<br>-400ps | -0.75 | +0.75 | -0.75 | +0.75 | -0.8 | +0.8 |

| tLZ(DQ)        | tACmin<br>-400ps | tACmax<br>-400ps | tACmin<br>-400ps | tACmax<br>-400ps | tACmin<br>-400ps | tACmax<br>-400ps | -0.75 | +0.75 | -0.75 | +0.75 | -0.8 | +0.8 |

| tHZ(DQS)       |                  |                  |                  |                  |                  |                  | -0.75 | +0.75 | -0.75 | +0.75 | -0.8 | +0.8 |

| tLZ(DQS)       |                  |                  |                  |                  |                  |                  | -0.75 | +0.75 | -0.75 | +0.75 | -1.1 | -0.8 |

| tWPST<br>(tCK) | 0.25             |                  | 0.25             |                  | 0.25             |                  | 0.4   | 0.6   | 0.4   | 0.6   | 0.4  | 0.6  |

| tPDEX          | 10ns             |                  | 10ns             |                  | 10ns             |                  | 7.5ns |       | 7.5ns |       | 10ns |      |

#### Version 1.31(November,2001)

- Deleted tHZ/tLZ of DQS

### **Contents**

**Revision History**

General Information

- 1. Key Features

- 1.1 Features

- 1.2 Operating Frequencies

- 2. Package Pinout & Dimension

- 2.1 Package Pintout

- 2.2 Input/Output Function Description

- 2.3 66 Pin TSOP(II)/MS-024FC Package Physical Dimension

- 3. Functional Description

- 3.1 Simplified State Diagram

- 3.2 Basic Functionality

- 3.2.1 Power-Up Sequence

- 3.2.2 Mode Register Definition

- 3.2.2.1 Mode Register Set(MRS)

- 3.2.2.2 Extended Mode Register Set(EMRS)

- 3.2.3 Precharge

- 3.2.4 No Operation(NOP) & Device Deselect

- 3.2.5 Row Active

- 3.2.6 Read Bank

- 3.2.7 Write Bank

- 3.3 Essential Functionality for DDR SDRAM

- 3.3.1 Burst Read Operation

- 3.3.2 Burst Write Operation

- 3.3.3 Read Interrupted by a Read

- 3.3.4 Read Interrupted by a Write & Burst Stop

- 3.3.5 Read Interrupted by a Precharge

- 3.3.6 Write Interrupted by a Write

- 3.3.7 Write Interrupted by a Read & DM

- 3.3.8 Write Interrupted by a Precharge & DM

- 3.3.9 Burst Stop

- 3.3.10 DM masking

- 3.3.11 Read With Auto Precharge

- 3.3.12 Write With Auto Precharge

- 3.3.13 Auto Refresh & Self Refresh

- 3.3.14 Power Down

- 4. Command Truth Table

- 5. Functional Truth Table

- 6. Absolute Maximum Rating

- 7. DC Operating Conditions & Specifications

- 7.1 DC Operating Conditions

- 7.2 DC Specifications

- 8. AC Operating Conditions & Timming Specification

- 8.1 AC Operating Conditions

- 8.2 AC Overshoot/Undershoot specification

- 8.1.1 Overshoot/Undershoot specification for Address and Control Pins

- 8.1.2 Overshoot/Undershoot specification for Data Pins

- 8.3 AC Timming Parameters & Specification

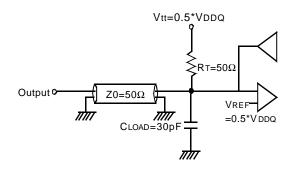

- 9. AC Operating Test Conditions

- 10. Input/Output Capacitance

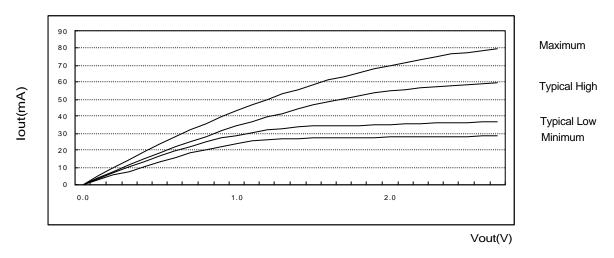

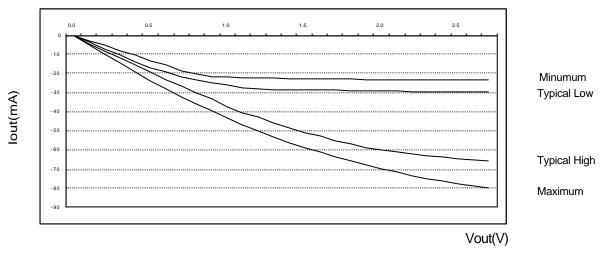

- 11. IBIS: I/V Characteristics for Input and Output Buffers

- 11.1 Normal strength driver

- 11.2 Half strength driver

**Timing Diagram**

### List of tables

Table 1 : Operating frequency and DLL jitter Table 2. : Column address configurtion

Table 3: Input/Output function description

Table 4: Burst address ordering for burst length

Table 5: Bank selection for precharge by bank address bits

Table 6 : Operating description when new command asserted while

read with auto precharge is issued

Table 7 : Operating description when new command asserted while write with auto precharge is issued

Table 8 : Command truth table Table 9-1 : Functional truth table

Table 9-2 : Functional truth table (contined)

Table 9-3: Functional truth table (contined)

Table 9-4: Functional truth table (contiued)

Table 9-5: Functional truth table (cotinued)

Table 10: Absolute maximum raings

Table 11: DC operating condtion

Table 12 : DC specification

Table 13: AC operating condition

Table 14: Overshoot/Undershoot specification for Address and Control Pins

Table 15: Overshoot/Undershoot specification for Data Pins

Table 16: AC timing parameters and specifications

Table 17: AC operating test conditions

Table 18: Input/Output capacitance

Table 19: Pull down and pull up current values(For normal strength driver)

Table 20 : Pull down and pull up current values(For half strength driver)

## List of figures

Figure 1 : 128Mb Package Pinout Figure 2 : Package dimension

Figure 3: State digram

Figure 4: Power up and initialization sequence

Figure 5: Mode register set

Figure 6 : Mode register set sequence Figure 7 : Extend mode register set

Figure 8: Bank activation command cycle timing

Figure 9: Burst read operation timing Figure 10: Burst write operation timing

Figure 11: Read interrupted by a read timing

Figure 12: Read interrupted by a write and burst stop timing

Figure 13: Read interrupted by a precharge timing

Figure 14: Write interrupted by a write timing

Figure 15: Write interrupted by a read and DM timing

Figure 16: Write interrupted by a precharge and DM timing

Figure 17 : Burst stop timing Figure 18 : DM masking timing

Figure 19: Read with auto precharge timing Figure 20: Write with auto precharge timing

Figure 21 : Auto refresh timing Figure 22 : Self refresh timing

Figure 23 : Power down entry and exit timing Figure 24 : AC overshoot/Undershoot Definition Figure 25 : AC overshoot/Undershoot Definition

Figure 28: I / V characteristics for input/output buffers(For half strength driver): pull-up(above) and pull-down(below)

### **General Information**

| Organization | 133Mhz w/ CL=2  | 133Mhz w/ CL=2.5 | 100Mhz w/ CL=2  |

|--------------|-----------------|------------------|-----------------|

| 32Mx4        | K4H280438B-TCA2 | K4H280438B-TCB0  | K4H280438B-TCA0 |

| OZIVIX4      | K4H280438B-TLA2 | K4H280438B-TLB0  | K4H280438B-TLA0 |

| 16Mx8        | K4H280838B-TCA2 | K4H280838B-TCB0  | K4H280838B-TCA0 |

| TOMXO        | K4H280838B-TLA2 | K4H280838B-TLB0  | K4H280838B-TLA0 |

| 8Mx16        | K4H281638B-TCA2 | K4H281638B-TCB0  | K4H281638B-TCA0 |

| OIVIX 10     | K4H281638B-TLA2 | K4H281638B-TLB0  | K4H281638B-TLA0 |

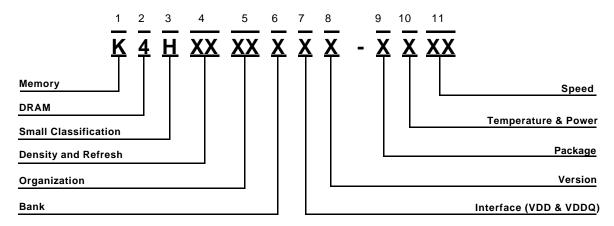

1. SAMSUNG Memory: K

2. DRAM: 4

3. Small Classification H:DDR SDRAM

#### 4. Density & Refresh

64 : 64M 4K/64ms 28 : 128M 4K/64ms 56 : 256M 8K/64ms 51 : 512M 8K/64ms 1G : 1G 16K/32ms

#### 5. Organization

04 : x4 08 : x8 16 : x16 32 : x32

### 6. Bank

3:4 Bank

#### 7. Interface (VDD & VDDQ)

8: SSTL-2(2.5V, 2.5V)

#### 8. Version

M: 1st Generation

A: 2nd Generation

B: 3rd Generation

C: 4th Generation

D: 5th Generation

E: 6th Generation

#### 9. Package

T: TSOP2 (400mil x 875mil)

#### 10. Temperature & Power

C: (Commercial, Normal)L: (Commercial, Low)

#### 11. Speed

A0:10ns@CL2 A2:7.5ns@CL2 B0:7.5ns@CL2.5

### 1. Key Features

#### 1.1 Features

- Double-data-rate architecture; two data transfers per clock cycle

- Bidirectional data strobe(DQS)

- Four banks operation

- Differential clock inputs(CK and CK)

- DLL aligns DQ and DQS transition with CK transition

- MRS cycle with address key programs

- -. Read latency 2, 2.5 (clock)

- -. Burst length (2, 4, 8)

- -. Burst type (sequential & interleave)

- All inputs except data & DM are sampled at the positive going edge of the system clock(CK)

- Data I/O transactions on both edges of data strobe

- · Edge aligned data output, center aligned data input

- LDM,UDM/DM for write masking only

- · Auto & Self refresh

- 15.6us refresh interval(4K/64ms refresh)

- Maximum burst refresh cycle: 8

- 66pin TSOP II package

### 1.2 Operating Frequencies

|              | - A2(DDR266A) | - B0(DDR266B) | - A0(DDR200) |

|--------------|---------------|---------------|--------------|

| Speed @CL2   | 133MHz        | 100MHz        | 100MHz       |

| Speed @CL2.5 | 133MHz        | 133MHz        | -            |

| DLL jitter   | ±0.75ns       | ±0.75ns       | ±0.8ns       |

\*CL: Cas Latency

Table 1. Operating frequency and DLL jitter

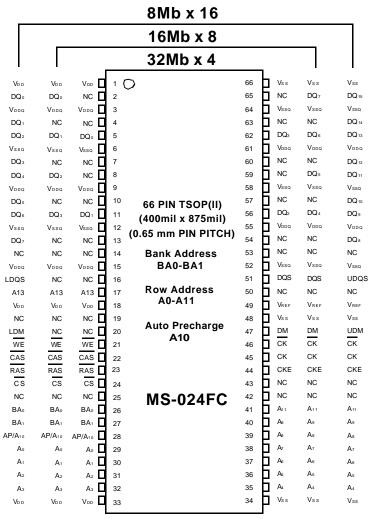

- 2. Package Pinout & Dimension

- 2.1 Package Pinout

Flgure 1. 128Mb package Pinout

| Organization | Column Address |

|--------------|----------------|

| 32Mx4        | A0-A9, A11     |

| 16Mx8        | A0-A9          |

| 8Mx16        | A0-A8          |

DM is internally loaded to match DQ and DQS identically.

Table 2. Column address configuration

### 2.2 Input/Output Function Description

| SYMBOL        | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK        | Input  | Clock : CK and $\overline{\text{CK}}$ are differential clock inputs. All address and control input signals are sampled on the positive edge of CK and negative edge of $\overline{\text{CK}}$ . Output (read) data is referenced to both edges of CK. Internal clock signals are derived from $\overline{\text{CK}}/\overline{\text{CK}}$ .                                                                                                                                                                                                                                                                 |

| CKE           | Input  | Clock Enable: CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and output drivers. Deactivating the clock provides PRECHARGE POWER-DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER-DOWN (row ACTIVE in any bank). CKE is synchronous for all functions except for disabling outputs, which is achieved asynchronously. Input buffers, excluding CK, CK and CKE are disabled during power-down and self refresh modes, providing low standby power. CKE will recognize an LVCMOS LOW level prior to VREF being stable on power-up.             |

| CS            | Input  | Chip Select: $\overline{CS}$ enables(registered LOW) and disables(registered HIGH) the command decoder. All commands are masked when $\overline{CS}$ is registered HIGH. $\overline{CS}$ provides for external bank selection on systems with multiple banks. $\overline{CS}$ is considered part of the command code.                                                                                                                                                                                                                                                                                       |

| RAS, CAS, WE  | Input  | Command Inputs : RAS, CAS and WE (along with CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *1LDM,(U)DM   | Input  | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. DM pins include dummy loading internally, to matches the DQ and DQS loading. For the x16, LDM corresponds to the data on DQ0-DQ7; UDM correspons to the data on DQ8-DQ15.                                                                                                                                                                                                                                    |

| BA0, BA1      | Input  | Bank Addres Inputs: BA0 and BA1 define to which bank an ACTIVE, READ, WRITE or PRE-CHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A [n : 0]     | Input  | Address Inputs: Provide the row address for ACTIVE commands, and the column address and AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10 is sampled during a PRECHARGE command to determine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code during a MODE REGISTER SET command. BA0 and BA1 define which mode register is loaded during the MODE REGISTER SET command (MRS or EMRS). |

| *1DQ          | I/O    | Data Input/Output : Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *1LDQS,(U)DQS | I/O    | Data Strobe: Output with read data, input with write data. Edge-aligned with read data, centered in write data. Used to capture write data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                 |

| NC            | -      | No Connect : No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDQ          | Supply | DQ Power Supply: +2.5V ± 0.2V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VssQ          | Supply | DQ Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDD           | Supply | Power Supply: +2.5V ± 0.2V (device specific).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vss           | Supply | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VREF          | Input  | SSTL_2 reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### **Table 3. Input/Output Function Description**

$^{\star}1$ : DQ, DQS, DM signals may be floated to VTT when no data is being transfened.

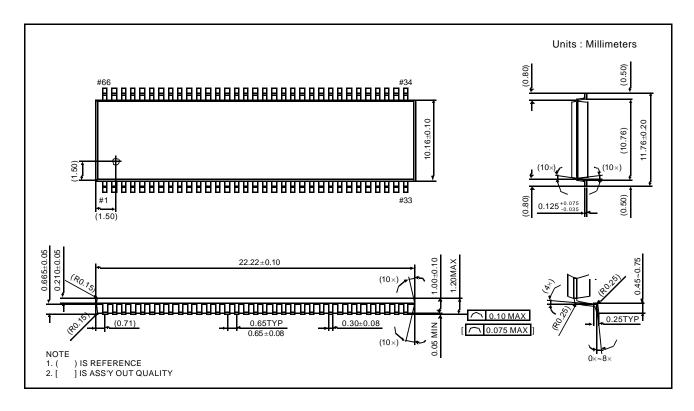

## E. 66pin TSOP-II Package Dimension

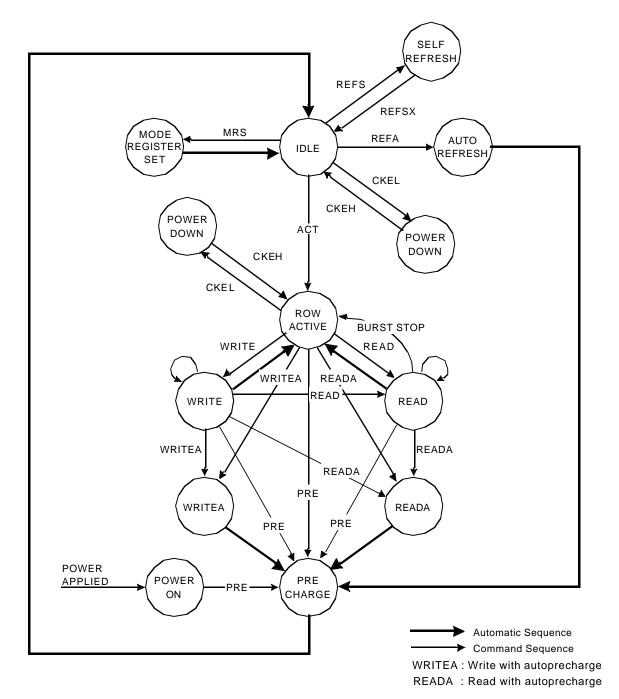

- 3. Functional Description

- 3.1 Simplified State Diagram

Figure 3. State diagram

#### 3.2 Basic Functionality

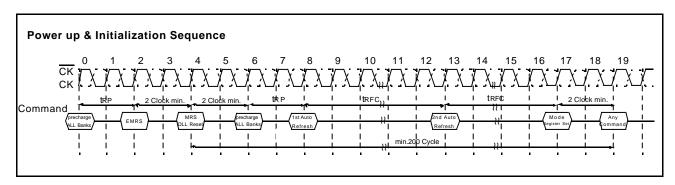

### 3.2.1 Power-Up and Initialization Sequence

The following sequence is required for POWER UP and Initialization.

- 1. Apply power and attempt to maintain CKE at a low state(all other inputs may be undefined.)

- Apply VDD before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT & Vref.

No power sequencing is specified during power up or power down given the following criteria:

- VDD and VDDQ are driven from a single power converter output, and

- VTT is limited to 1.44V (reflecting VDDQ(max)/2 + 50mV VREF variation +40m V VTT variation), and

- VREF tracks VDDQ/2, and

- A minimum resistance of 42 ohms(22 ohm series resistor + 22 ohm parallel resistor 5% tolerance) limits the input current from the VTT supply into any pin.

If the above criteria cannot be met by the system design, the following table must be adhered to during power up:

| Voltage Description | Sequencing         | Voltage Relationship to avoid latch-up |

|---------------------|--------------------|----------------------------------------|

| VDDQ                | After or with VDD  | <vdd +="" 0.3v<="" td=""></vdd>        |

| VTT                 | After or with VDDQ | < VDDQ +0.3V                           |

| VREF                | After or with VDDQ | <vddq +0.3v<="" td=""></vddq>          |

- 2. Start clock and maintain stable condition for a minimum of 200us.

- 3. The minimum of 200us after stable power and clock(CK, CK), apply NOP & take CKE high.

- 4. Issue precharge commands for all banks of the device.

- 5. Issue EMRS to enable DLL.(To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low" to all of the rest address pins, A1~A11 and BA1)

- 6. Issue a mode register set command for "DLL reset". The additional 200 cycles of clock input is required to lock the DLL. (To issue DLL reset command, provide "High" to A8 and "Low" to BA0)

- <sup>\*1</sup> 7. Issue precharge commands for all banks of the device.

- 8. Issue 2 or more auto-refresh commands.

- 9. Issue a mode register set command with low to A8 to initialize device operation.

- \*1 Sequence of 6 & 7 is regardless of the order.

Figure 4. Power up and initialization sequence

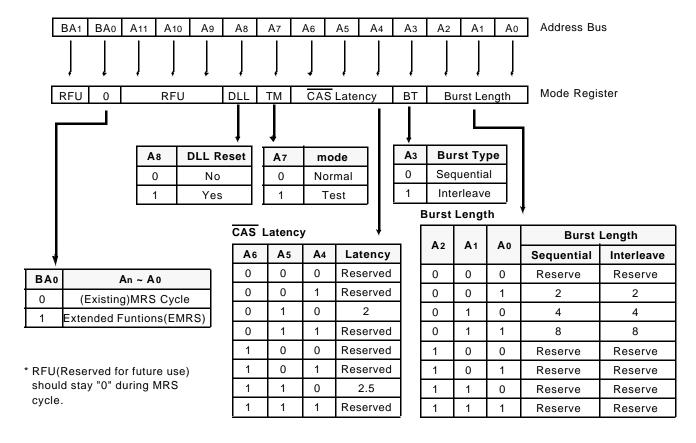

#### 3.2.2 Mode Register Definition

#### 3.2.2.1 Mode Register Set(MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs CAS latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make DDR SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for proper DDR SDRAM operation. The mode register is written by asserting low on CS, RAS, CAS, WE and BA0(The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register). The states of address pins A0 ~ A11 in the same cycle as CS, RAS, CAS, WE and BA0 going low are written in the mode register. Two clock cycles are requested to complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A0 ~ A2, addressing mode uses A3, CAS latency(read latency from column address) uses A4 ~ A6. A7 is used for test mode. A8 is used for DLL reset. A7 must be set to low for normal MRS operation. Refer to the table for specific codes for various burst lengths, addressing modes and CAS latencies.

Figure 5. Mode Register Set

| <b>Burst Address</b> | Ordering | for | Ruret | Lenath |

|----------------------|----------|-----|-------|--------|

| Duist Addiess        | Oracilia | 101 | Duisi | Lengui |

| Burst<br>Length | Starting<br>Address(A2, A1, A0) | Sequential Mode        | Interleave Mode        |

|-----------------|---------------------------------|------------------------|------------------------|

| 2               | xx0                             | 0, 1                   | 0, 1                   |

|                 | xx1                             | 1, 0                   | 1, 0                   |

|                 | x00                             | 0, 1, 2, 3             | 0, 1, 2, 3             |

| 4               | x01                             | 1, 2, 3, 0             | 1, 0, 3, 2             |

| 4               | x10                             | 2, 3, 0, 1             | 2, 3, 0, 1             |

|                 | x11                             | 3, 0, 1, 2             | 3, 2, 1, 0             |

|                 | 000                             | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |

|                 | 001                             | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |

|                 | 010                             | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |

| 8               | 011                             | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |

| 0               | 100                             | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |

|                 | 101                             | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |

|                 | 110                             | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |

|                 | 111                             | 7, 0, 1, 2, 3, 4, 5, 6 | 7, 6, 5, 4, 3, 2, 1, 0 |

Table 4. Burst address ordering for burst length

#### **DLL Enable/Disable**

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization, and upon returing to normal operation after having disabled the DLL for the purpose of debug or evaluation (upon exiting Self Refresh Mode, the DLL is enabled automatically). Any time the DLL is enabled, 200 clock cycles must occur before a READ command can be issued.

#### Output Drive Strength

The normal drive strength for all outputs is specified to be SSTL\_2, Class II. Some vendors might also support a weak driver strength option, intended for lighter load and/or point-to-point environments. I-V curves for the normal drive strength and weak drive strength will be included in a future revision of this document.

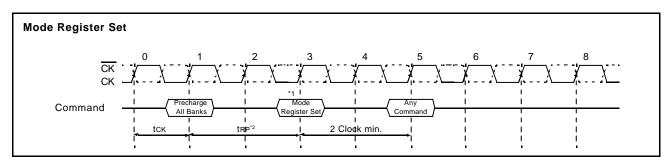

- \*1 : MRS can be issued only at all bank precharge state.

- \*2 : Minimum tRP is required to issue MRS command.

Figure 6. Mode Register Set sequence

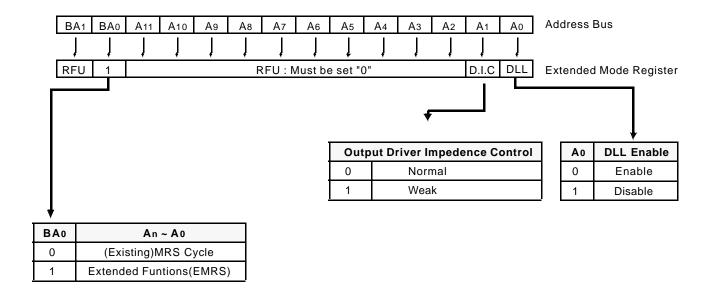

#### 3.2.2.2 Extended Mode Register Set(EMRS)

The extended mode register stores the data for enabling or disabling DLL,  $\overline{QFC}$  and selecting output driver size. The default value of the extended mode register is not defined, therefore the extended mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and high on BA0(The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register). The state of address pins A0 ~ A11 and BA1 in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  going low are written in the extended mode register. Two clock cycles are required to complete the write operation in the extended mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. A0 is used for DLL enable or disable. "High" on BA0 is used for EMRS. All the other address pins except A0 and BA0 must be set to low for proper EMRS operation. Refer to the table for specific codes.

Figure 7. Extend Mode Register set

#### 3.2.3 Precharge

The precharge command is used to precharge or close a bank that has been activated. The precharge command is issued when  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{WE}$  are low and  $\overline{CAS}$  is high at the rising edge of the clock. The precharge command can be used to precharge each bank respectively or all banks simultaneously. The bank select addresses(BA0, BA1) are used to define which bank is precharged when the command is initiated. For write cycle, tWR(min.) must be satisfied until the precharge command can be issued. After tRP from the precharge, an active command to the same bank can be initiated.

|        |     | • • |             |

|--------|-----|-----|-------------|

| A10/AP | BA1 | BA0 | Precharge   |

| 0      | 0   | 0   | Bank A Only |

| 0      | 0   | 1   | Bank B Only |

| 0      | 1   | 0   | Bank C Only |

| 0      | 1   | 1   | Bank D Only |

| 1      | X   | Х   | All Banks   |

Bank Selection for Precharge by Bank address bits

Table 5. Bank selection for precharge by Bank address bits

### 3.2.4 No Operation(NOP) & Device Deselect

The device should be deselected by deactivating the  $\overline{CS}$  signal. In this mode DDR SDRAM should ignore all the control inputs. The DDR SDRAMs are put in NOP mode when  $\overline{CS}$  is active and by deactivating RAS, CAS and WE. For both Deselect and NOP the device should finish the current operation when this command is issued.

#### 3.2.5 Row Active

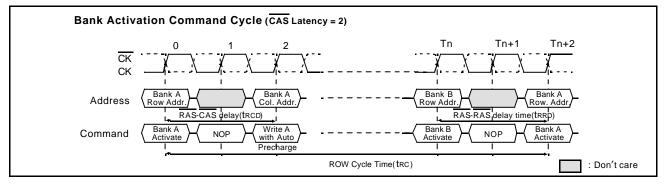

The Bank Activation command is issued by holding  $\overline{CAS}$  and  $\overline{WE}$  high with  $\overline{CS}$  and  $\overline{RAS}$  low at the rising edge of the clock(CK). The DDR SDRAM has four independent banks, so two Bank Select addresses(BA0, BA1) are required. The Bank Activation command must be applied before any Read or Write operation is executed. The delay from the Bank Activation command to the first read or write command must meet or exceed the minimum of  $\overline{RAS}$  to  $\overline{CAS}$  delay time(tRCD min). Once a bank has been activated, it must be precharged before another Bank Activation command can be applied to the same bank. The minimum time interval between interleaved Bank Activation commands(Bank A to Bank B and vice versa) is the Bank to Bank delay time(tRRD min).

Figure 8. Bank activation command cycle timing

#### 3.2.6 Read Bank

This command is use<u>d after the row activate command to initiate the burst read of data.</u> The read command is initiated by activating RAS, CS, CAS, and deasserting WE at the same clock sampling(rising) edge as described in the command truth table. The length of the burst and the CAS latency time will be determined by the values programmed during the MRS command.

#### 3.2.7 Write Bank

This command is used afte<u>r the row activate command</u> to initiate the burst write of data. The write command is initiated by activating RAS, CS, CAS, and WE at the same clock sampling(rising) edge as described in the command truth table. The length of the burst will be determined by the values programmed during the MRS command.

#### 3.3 Essential Functionality for DDR SDRAM

The essential functionality that is required for the DDR SDRAM device is described in this chapter

### 3.3.1 Burst Read Operation

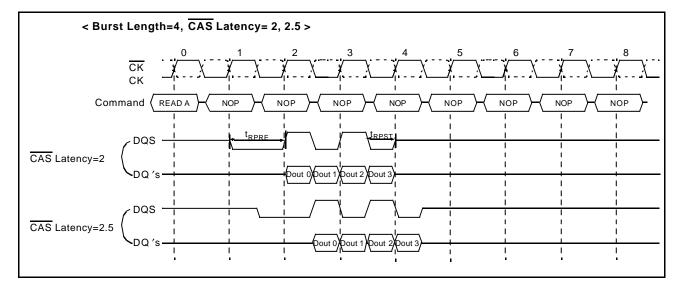

Burst Read operation in DDR SDRAM is in the same manner as the current SDRAM such that the Burst read command is issued by asserting CS and CAS low while holding RAS and WE high at the rising edge of the clock(CK) after tRCD from the bank activation. The address inputs (A0~A9) determine the starting address for the Burst. The Mode Register sets type of burst(Sequential or interleave) and burst length(2, 4, 8). The first output data is available after the CAS Latency from the READ command, and the consecutive data are presented on the falling and rising edge of Data Strobe(DQS) adopted by DDR SDRAM until the burst length is completed.

Figure 9. Burst read operation timing

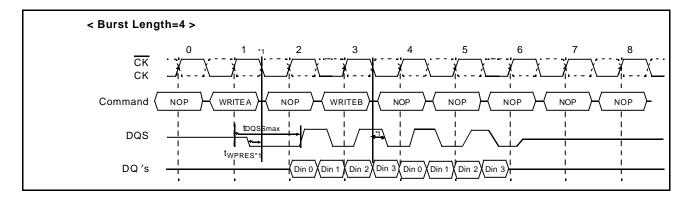

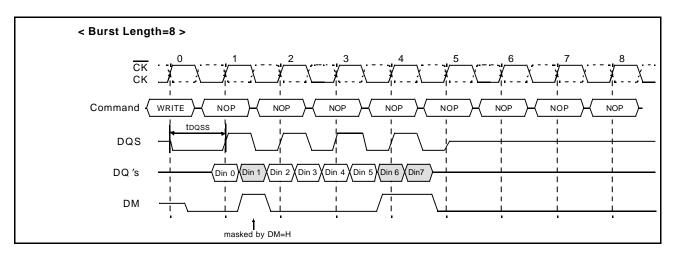

#### 3.3.2 Burst Write Operation

The Burst Write command is issued by having  $\overline{CS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  low while holding  $\overline{RAS}$  high at the rising edge of the clock(CK). The address inputs determine the starting column address. There is no write latency relative to DQS required for burst write cycle. The first data of a burst write cycle must be applied on the DQ pins tDS(Data-in setup time) prior to data strobe edge enabled after tDQSS from the rising edge of the clock(CK) that the write command is issued. The remaining data inputs must be supplied on each subsequent falling and rising edge of Data Strobe until the burst length is completed. When the burst has been finished, any additional data supplied to the DQ pins will be ignored.

Figure 10. Burst write operation timing

1. The specific requirement is that DQS be valid(High or Low) on or before this CK edge. The case shown (DQS going from High\_Z to logic Low) applies when no writes were previously in progress on the bus. If a previous write was in progress, DQS could be High at this time, depending on tDQSS.

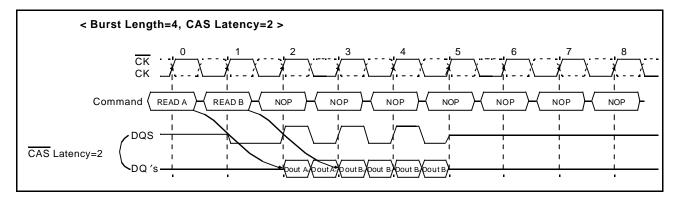

#### 3.3.3 Read Interrupted by a Read

A Burst Read can be interrupted before completion of the burst by new Read command of any bank. When the previous burst is interrupted, the remaining addresses are overridden by the new address with the full burst length. The data from the first Read command continues to appear on the outputs until the CAS latency from the interrupting Read command is satisfied. At this point the data from the interrupting Read command appears. Read to Read interval is minimum 1 Clock.

Figure 11. Read interrupted by a read timing

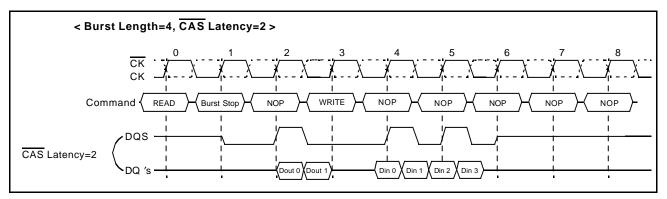

### 3.3.4 Read Interrupted by a Write & Burst Stop

To interrupt a burst read with a write command, Burst Stop command must be asserted to avoid data contention on the I/O bus by placing the DQ's (Output drivers) in a high impedance state. To insure the DQ's are tristated one cycle before the beginning the write operation, Burst stop command must be applied at least 2 clock cycles for CL=2 and at least 3 clock cycles for CL=2.5 before the Write command.

Figure 12. Read interrupted by a write and burst stop timing.

The following functionality establishes how a Write command may interrupt a Read burst.

- For Write commands interrupting a Read burst, a Burst Terminate command is required to stop the read burst and tristate the DQ bus prior to valid input write data. Once the <u>Burst Terminate command has been</u> issued, the minimum delay to a Write command = RU(CL) [CL is the <u>CAS</u> Latency and RU means round up to the nearest integer].

- 2. It is illegal for a Write command to interrupt a Read with autoprecharge command.

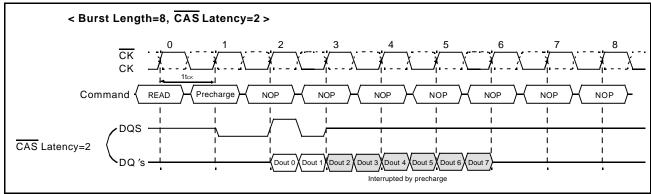

### 3.3.5 Read Interrupted by a Precharge

A Burst Read operation can be interrupted by precharge of the same bank. The minimum 1 clock is required for the read to precharge intervals. A precharge command to output disable latency is equivalent to the  $\overline{\text{CAS}}$  latency.

Figure 13. Read interrupted by a precharge timing

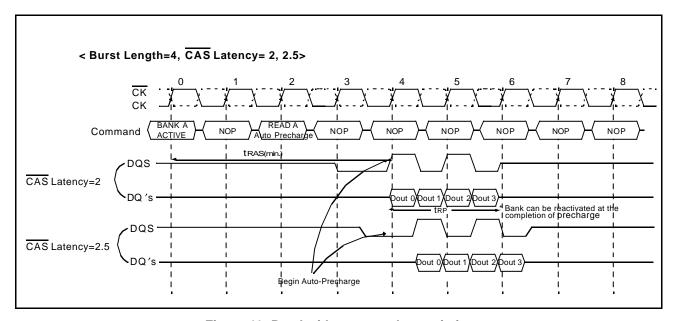

When a burst Read command is issued to a DDR SDRAM, a Precharge command may be issued to the same bank before the Read burst is complete. The following functionality determines when a Precharge command may be given during a Read burst and when a new Bank Activate command may be issued to the same bank.

- For the earliest possible Precharge command without interrupting a Read burst, the Precharge command may be given on the rising clock edge which is CL clock cycles before the end of the Read burst where CL is the CAS Latency. A new Bank Activate command may be issued to the same bank after tRP (RAS Precharge time).

- 2. When a Precharge command interrupts a Read burst operation, the Precharge command may be given on the rising <u>clock</u> edge which is CL clock cycles before the last data from the interrupted Read burst where CL is the CAS Latency. Once the last data word has been output, the output buffers are tristated. A new Bank Activate command may be issued to the same bank after tRP.

- 3. For a Read with autoprecharge command, a new Bank Activate command may be issued to the same bank after tRP where tRP begins on the rising clock edge which is CL clock cycles before the end of the Read burst where CL is the CAS Latency. During Read with autoprecharge, the initiation of the internal precharge occurs at the same time as the earliest possible external Precharge command would initiate a precharge operation without interrupting the Read burst as described in 1 above.

- 4. For all cases above, tRP is an analog delay that needs to be converted into clock cycles. The number of clock cycles between a Precharge command and a new Bank Activate command to the same bank equals tRP/tCK (where tCK is the clock cycle time) with the result rounded up to the nearest integer number of clock cycles. (Note that rounding to X.5 is not possible since the Precharge and Bank Activate commands can only be given on a *rising* clock edge).

In all cases, a Precharge operation cannot be initiated unless tRAS(min) [minimum Bank Activate to Precharge time] has been satisfied. This includes Read with autoprecharge commands where tRAS(min) must still be satisfied such that a Read with autoprecharge command has the same timing as a Read command followed by the earliest possible Precharge command which does not interrupt the burst.

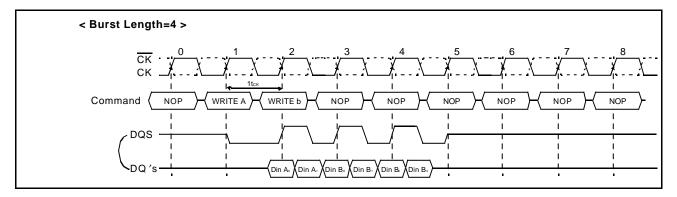

### 3.3.6 Write Interrupted by a Write

A Burst Write can be interrupted before completion of the burst by a new Write command, with the only restriction that the interval that separates the commands must be at least one clock cycle. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.

Figure 14. Write interrupted by a write timing

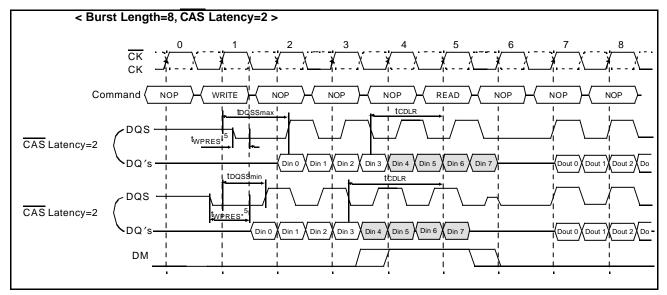

#### 3.3.7 Write Interrupted by a Read & DM

A burst write can be interrupted by a read command of any bank. The DQ's must be in the high impedance state at least one clock cycle before the interrupting read data appear on the outputs to avoid data contention. When the read command is registered, any residual data from the burst write cycle must be masked by DM. The delay from the last data to read command (tCDLR) is required to avoid the data contention DRAM inside. Data that are presented on the DQ pins before the read command is initiated will actually be written to the memory. Read command interrupting write can not be issued at the next clock edge of that of write command.

Figure 15. Write interrupted by a read and DM timing

The following function established how a Read command may interrupt a Write burst and which input data is not written into the memory.

- 1. For Read commands interrupting a Write burst, the minimum Write to Read command delay is 2 clock cycles. The case where the Write to Read delay is 1 clock cycle is disallowed

- 2. For Read commands interrupting a Write burst, the DM pin must be used to mask the input data words which immediately precede the interrupting Read operation and the input data word which immediately follows the interrupting Read operation

- 3. For all cases of a Read interrupting a Write, the DQ and DQS buses must be released by the driving chip (i.e., the memory controller) in time to allow the buses to turn around before the DDR SDRAM drives them during a read operation.

- 4. If input Write data is masked by the Read command, the DQS input is ignored by the DDR SDRAM.

- 5. Refer to "3.3.2 Burst write operation"

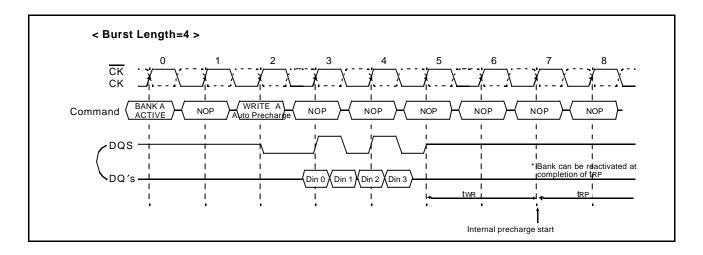

### 3.3.8 Write Interrupted by a Precharge & DM

A burst write operation can be interrupted before completion of the burst by a precharge of the same bank. Random column access is allowed. A write recovery time(tWR) is required from the last data to precharge command. When precharge command is asserted, any residual data from the burst write cycle must be masked by DM.

Figure 16. Write interrupted by a precharge and DM timing

Precharge timing for Write operations in DRAMs requires enough time to allow "write recovery" which is the time required by a DRAM core to properly store a full "0" or "1" level before a Precharge operation. For DDR SDRAM, a timing parameter, tWR, is used to indicate the required amount of time between the last valid write operation and a Precharge command to the same bank.

The precharge timing for writes is a complex definition since the write data is sampled by the data strobe and the address is sampled by the input clock. Inside the SDRAM, the data path is eventually synchronized with the address path by switching clock domains from the data strobe clock domain to the input clock domain. This makes the definition of when a precharge operation can be initiated after a write very complex since the write recovery parameter must reference only the clock domain that is used to time the internal write operation, i.e., the input clock domain.

tWR starts on the rising clock edge after the last possible DQS edge that strobed in the last valid data and ends on the rising clock edge that strobes in the precharge command.

- 1. For the earliest possible Precharge command following a Write burst without interrupting the burst, the minimum time for write recovery is defined by tWR.

- 2. When a precharge command interrupts a Write burst operation, the data mask pin, DM, is used to mask input data during the time between the last valid write data and the rising clock edge on which the Precharge command is given. During this time, the DQS input is still required to strobe in the state of DM. The minimum time for write recovery is defined by tWR.

- 3. For a Write with autoprecharge command, a new Bank Activate command may be issued to the same bank after tWR+tRP where tWR+tRP starts on the rising DQS edge that strobed in the last valid data and ends on the rising clock edge that strobes in the Bank Activate command. During write with autoprecharge, the initiation of the internal precharge occurs at the same time as the earliest possible external Precharge command without interrupting the Write burst as described in 1 above.

- 4. In all cases, a Precharge operation cannot be initiated unless tRAS(min) [minimum Bank Activate to Precharge time] has been satisfied. This includes Write with autoprecharge commands where tRAS(min) must still be satisfied such that a Write with autoprecharge command has the same timing as a Write command followed by the earliest possible Precharge command which does not interrupt the burst.

- 5. Refer to "3.3.2 Burst write operation"

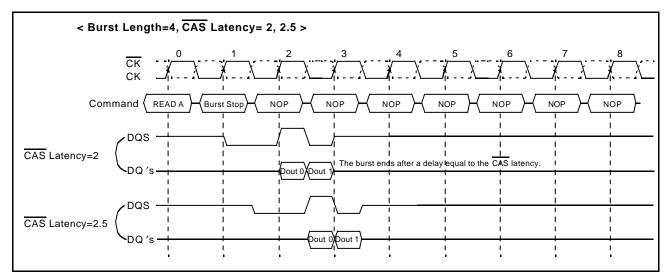

#### 3.3.9 Burst Stop

The burst stop command is initiated by having  $\overline{RAS}$  and  $\overline{CAS}$  high with  $\overline{CS}$  and  $\overline{WE}$  low at the rising edge of the clock(CK). The burst stop command has the fewest restrictions making it the easiest method to use when terminating a burst read operation before it has been completed. When the burst stop command is issued during a burst read cycle, the pair of data and DQS(Data Strobe) go to a high impedance state after a delay which is equal to the  $\overline{CAS}$  latency set in the mode register. The burst stop command, however, is not supported during a write burst operation.

Figure 17. Burst stop timing

The Burst Stop command is a mandatory feature for DDR SDRAMs. The following functionality is required:

- 1. The BST command may only be issued on the rising edge of the input clock, CK.

- 2. BST is only a valid command during Read bursts.

- 3. BST during a Write burst is undefined and shall not be used.

- 4. BST applies to all burst lengths.

- 5. BST is an undefined command during Read with autoprecharge and shall not be used.

- 6. When terminating a burst Read command, the BST command must be issued L<sub>BST</sub> ("BST Latency") clock cycles before the clock edge at which the output buffers are tristated, where L<sub>BST</sub> equals the CAS latency for read operations. This is shown in previous page Figure with examples for CAS latency (CL) of 1.5, 2, 2.5, 3 and 3.5 (only selected CAS latencies are required by the DDR SDRAM standards, the others are optional).

- 7. When the burst terminates, the DQ and DQS pins are tristated.

The BST command is not byte controllable and applies to all bits in the DQ data word and the(all) DQS pin(s).

### 3.3.10 DM masking

The DDR SDRAM has a data mask function that can be used in conjunction with data write cycle, not read cycle. When the data mask is activated (DM high) during write operation, DDR SDRAM does not accept the corresponding data.(DM to data-mask latency is zero).

DM must be issued at the rising or falling edge of data strobe.

Figure 18. DM masking timing

### 3.3.11 Read With Auto Precharge

If a read with auto-precharge command is initiated, the DDR SDRAM automatically enters the precharge operation BL/2 clock later from a read with auto-precharge command when tRAS(min) is satisfied. If not, the start point of precharge operation will be delayed until tRAS(min) is satisfied. Once the precharge operation has started the bank cannot be reactivated and the new command can not be asserted until the precharge time(tRP) has been satisfied.

Figure 19. Read with auto precharge timing

When the Read with Auto precharge command is issued, new command can be asserted at 3,4 and 5 respectively as follows,

| Asserted  | F                             | or same Bank   | <       | For Different Bank |       |       |  |

|-----------|-------------------------------|----------------|---------|--------------------|-------|-------|--|

| command   | 3                             | 4              | 5       | 3                  | 4     | 5     |  |

| READ      | READ +<br>No AP <sup>*1</sup> | READ+<br>No AP | Illegal | Legal              | Legal | Legal |  |

| READ+AP   | READ +<br>AP                  | READ +<br>AP   | Illegal | Legal              | Legal | Legal |  |

| Active    | Illegal                       | Illegal        | Illegal | Legal              | Legal | Legal |  |

| Precharge | Legal                         | Legal          | Illegal | Legal              | Legal | Legal |  |

<sup>\*1 :</sup> AP = Auto Precharge

Table 6. Operating description when new command asserted while read with auto precharge is issued

### 3.3.12 Write with Auto Precharge

If A10 is high when write command is issued, the write with auto-precharge function is performed. Any new command to the same bank should not be issued until the internal precharge is completed. The internal precharge begins after keeping tWR(min).

Figure 20. Write with auto precharge timing

Burst length = 4

| Asserted     |                   |                                | For same Bank    |                 |         |         | For Different Bank |         |         |       |       |

|--------------|-------------------|--------------------------------|------------------|-----------------|---------|---------|--------------------|---------|---------|-------|-------|

| command      | 3 4 5 6 7 8       |                                | 3                | 4               | 5       | 6       | 7                  |         |         |       |       |

| WRITE        | WRITE+<br>No AP*1 | WRITE+<br>No AP                | Illegal          | Illegal         | Illegal | Illegal | Legal              | Legal   | Legal   | Legal | Legal |

| WRITE+<br>AP | WRITE+<br>AP      | WRITE+<br>AP                   | Illegal          | Illegal         | Illegal | Illegal | Legal              | Legal   | Legal   | Legal | Legal |

| READ         | Illegal           | READ+NO<br>AP+DM <sup>*2</sup> | READ+NO<br>AP+DM | READ+<br>NO AP  | Illegal | Illegal | Illegal            | Illegal | Illegal | Legal | Legal |

| READ+AP      | Illegal           | READ +<br>AP+DM                | READ +<br>AP+DM  | READ +<br>AP    | Illegal | Illegal | Illegal            | Illegal | Illegal | Legal | Legal |

| Active       | Illegal           | Illegal                        | Illegal          | Illegal Illegal |         | Illegal | Legal              | Legal   | Legal   | Legal | Legal |

| Precharge    | Illegal           | Illegal                        | Illegal          | Illegal         | Illegal | Illegal | Legal              | Legal   | Legal   | Legal | Legal |

<sup>\*1 :</sup> AP = Auto Precharge

Table 7. Operating description when new command asserted while write with auto precharge is issued

$<sup>^{\</sup>star 2}$  : DM : Refer to " 3.3.7 Write Interrupted by a Read & DM " in page 25.

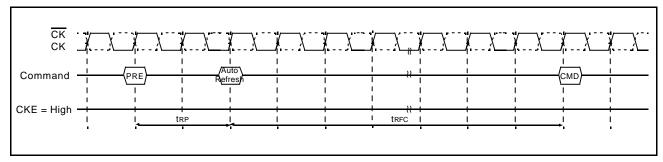

#### 3.3.13 Auto Refresh & Self Refresh

#### Auto Refresh

An auto refresh command is issued by having  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{CAS}$  held low with CKE and  $\overline{WE}$  high at the rising edge of the clock(CK). All banks must be precharged and idle for tRP(min) before the auto refresh command is applied. No control of the external address pins is required once this cycle has started because of the internal address counter. When the refresh cycle has completed, all banks will be in the idle state. A delay between the auto refresh command and the next activate command or subsequent auto refresh command must be greater than or equal to the tRFC(min).

Figure 21. Auto refresh timing

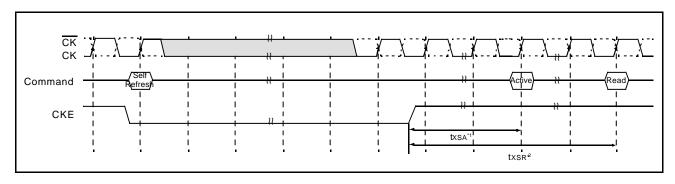

#### Self Refresh

A self refresh command is defined by having  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and CKE held low with  $\overline{WE}$  high at the rising edge of the clock(CK). Once the self refresh command is initiated, CKE must be held low to keep the device in self refresh mode. During the self refresh operation, all inputs except CKE are ignored. The clock is internally disabled during self refresh operation to reduce power consumption. The self refresh is exited by supplying stable clock input before returning CKE high, asserting deselect or NOP command and then asserting CKE high for longer than tXSR for locking of DLL.

Figure 22. Self refresh timing

- 1. Exit self refresh to bank active command, a write command can be applied as far as tRCD is satisfied after any bank active command.

- 2. Exit self refresh to read command

#### 3.3.14 Power down

The power down mode is entered when CKE is low and exited when CKE is high. Once the power down mode is initiated, all of the receiver circuits except clock, CKE and DLL circuit tree are gated off to reduce power consumption. All banks should be in idle state prior to entering the precharge power down mode and CKE should be set high at least 1tck+tlS prior to row active command. During power down mode, refresh operations cannot be performed, therefore the device cannot be remained in power down mode longer than the refresh period(Data retension time) of the device.

Figure 23. Power down entry and exit timing

#### 4. Command Truth Table

| CC                            | CKEn-1                 | CKEn         | cs  | RAS | CAS | WE | <b>BA</b> 0,1 | A10/AP | A11,<br>A9 ~ A0 | Note   |                                   |      |

|-------------------------------|------------------------|--------------|-----|-----|-----|----|---------------|--------|-----------------|--------|-----------------------------------|------|

| Register                      | Extended M             | IRS          | Н   | Х   | L   | L  | L             | L      | OP CODE         |        |                                   | 1, 2 |

| Register                      | Mode Regis             | ter Set      | Н   | Х   | L   | L  | L             | L      |                 | OP COD | E                                 | 1, 2 |

|                               | Auto Refres            | sh           | Н   | Н   | L   | L  | L             | Н      |                 | Х      |                                   | 3    |

| Refresh                       | 0.11                   | Entry        | ""  | L   |     | _  |               | ''     |                 | ^      |                                   | 3    |

| Kellesii                      | Self<br>Refresh        | Exit         | L   | Н   | L   | Н  | Н             | Н      |                 | Х      |                                   | 3    |

|                               |                        | EXIL         | L   |     | Н   | Х  | Х             | Х      |                 | ^      |                                   | 3    |

| Bank Active & Rov             | w Addr.                |              | Н   | Х   | L   | L  | Н             | Н      | V               | Row A  | Address                           |      |

| Read &                        | Auto Precha            | arge Disable | Н   | Х   | L   | Н  | L             | Н      | V               | L      | Column<br>Address                 | 4    |

| Column Address                | Auto Precha            | arge Enable  | ''' |     | -   | '' | _             |        | V               |        | (A <sub>0</sub> ~A <sub>9</sub> ) | 4    |

| Write &                       | Auto Precharge Disable |              | Н   | Х   | L   | Н  | L             | L      | V               | L      | Column<br>Address                 | 4    |

| Column Address Auto Precharge |                        | arge Enable  | П   | ^   | _   | п  | L             |        | V               | Н      | (A <sub>0</sub> ~A <sub>9</sub> ) | 4, 6 |

| Burst Stop                    | _                      |              | Н   | Х   | L   | Н  | Н             | L      |                 | Х      | _                                 | 7    |

| Precharge                     | Bank Selec             | tion         | Н   | - X | L   | L  | Н             | L      | V               | L      | X                                 |      |

| rrecharge                     | All Banks              |              |     |     | -   | _  | ''            |        | Х               | Н      |                                   | 5    |

|                               |                        | Entry        | Н   | L   | Н   | Х  | Х             | Х      | X               |        |                                   |      |

| Active Power Dow              | 'n                     | Littiy       | п   | _   | L   | V  | V             | V      |                 |        |                                   |      |

|                               |                        | Exit         | L   | Н   | Х   | Х  | Х             | Х      |                 |        |                                   |      |

|                               |                        | Entry        | Н   | L   | Н   | Х  | Х             | Х      |                 |        |                                   |      |

| Precharge Power               | Down Mode              | Littiy       |     |     | L   | Н  | Н             | Н      | X               |        |                                   |      |

| Precharge Power Down Mode     |                        | Exit         | L   | Н   | Н   | Х  | Х             | Х      | ^               |        |                                   |      |

| EXIL                          |                        |              | L   |     | L   | V  | V             | V      |                 |        |                                   |      |

| DM                            |                        |              | Н   |     | _   | Х  |               |        |                 | Х      |                                   | 8    |

| No operation (NOI             | P) · Not defin         | e d          | Н   | Х   | Н   | Х  | Х             | Х      |                 |        |                                   | 9    |

| ino operation (NOI            | r ) . Not dellii       | cu           | П   | _ ^ | L   | Н  | Н             | Н      | 1               | Χ      |                                   |      |

#### Table 8. Command truth table

(V=Valid, X=Don't Care, H=Logic High, L=Logic Low)

- 1. OP Code: Operand Code. A0 ~ A11 & BA0 ~ BA1: Program keys. (@EMRS/MRS)

- 2.EMRS/ MRS can be issued only at all banks precharge state.

A new command can be issued 2 clock cycles after EMRS or MRS.

- 3. Auto refresh functions are same as the CBR refresh of DRAM.

- The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

- 4. BA0 ~ BA1: Bank select addresses.

- If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.

- If both BAo is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected.

- If both BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected.

- If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected. 5. If A10/AP is "High" at row precharge, BA0 and BA1 are ignored and all banks are selected.

- 6. During burst write with auto precharge, new read/write command can not be issued.

- Another bank read/write command can be issued after the end of burst.

- New row active of the associated bank can be issued at tRP after the end of burst.

- 7. Burst stop command is valid at every burst length.

- 8. DM sampled at the rising and falling edges of the DQS and Data-in are masked at the both edges (Write DM latency is 0).

- 9. This combination is not defined for any function, which means "No Operation(NOP)" in DDR SDRAM.

### 5. Functional Truth Table

| Current State | CS  | RAS | CAS | WE | Address                | Command      | Action                                                                      |

|---------------|-----|-----|-----|----|------------------------|--------------|-----------------------------------------------------------------------------|

| PRECHARGE     | L   | Н   | Н   | L  | Х                      | Burst Stop   | ILLEGAL*2                                                                   |

| STANDBY       | L   | Н   | L   | Х  | BA, CA, A10 READ/WRITE |              | ILLEGAL*2                                                                   |

|               | L   | L   | Н   | Н  | BA, RA                 | Active       | Bank Active, Latch RA                                                       |

|               | L   | L   | Н   | L  | BA, A10                | PRE/PREA     | ILLEGAL*4                                                                   |

|               | L   | L   | L   | Н  | Х                      | Refresh      | AUTO-Refresh*5                                                              |

|               | L   | L   | L   | L  | Op-Code, Mode-Add      | MRS          | Mode Register Set*5                                                         |

| ACTIVE        | L   | Н   | Н   | L  | Х                      | Burst Stop   | NOP                                                                         |

| STANDBY       | L   | Н   | L   | н  | BA, CA, A10            | READ/READA   | Begin Read, Latch CA,<br>Determine Auto-Precharge                           |

|               | L   | Н   | L   | L  | BA, CA, A10            | WRITE/WRITEA | Begin Write, Latch CA,<br>Determine Auto-Precharge                          |

|               | L   | L   | Н   | Н  | BA, RA                 | Active       | Bank Active/ILLEGAL*2                                                       |

|               | ┙   | L   | Н   | L  | BA, A10                | PRE/PREA     | Precharge/Precharge All                                                     |

|               | L   | L   | L   | Н  | X                      | Refresh      | ILLEGAL                                                                     |

|               | L   | L   | L   | L  | Op-Code, Mode-Add      | MRS          | ILLEGAL                                                                     |

| READ          | L   | Н   | Η   | L  | X                      | Burst Stop   | Terminate Burst                                                             |

|               | لــ | Н   | L   | Ι  | BA, CA, A10            | READ/READA   | Terminate Burst, Latch CA,<br>Begin New Read, Determine<br>Auto-Precharge*3 |

|               | L   | Н   | L   | L  | BA, CA, A10            | WRITE/WRITEA | ILLEGAL                                                                     |

|               | L   | L   | Н   | Н  | BA, RA                 | Active       | Bank Active/ILLEGAL*2                                                       |

|               | L   | L   | Н   | L  | BA, A10                | PRE/PREA     | Terminate Burst, Precharge                                                  |

|               | L   | L   | L   | Н  | X                      | Refresh      | ILLEGAL                                                                     |

|               | L   | L   | L   | L  | Op-Code, Mode-Add      | MRS          | ILLEGAL                                                                     |

Table 9-1. Functional truth table

| Current State                  | cs | RAS | CAS | WE | Address           | Command      | Action                                                                                 |

|--------------------------------|----|-----|-----|----|-------------------|--------------|----------------------------------------------------------------------------------------|

| WRITE                          | L  | Н   | Н   | L  | Х                 | Burst Stop   | ILLEGAL                                                                                |

|                                | L  | Н   | L   | н  | BA, CA, A10       | READ/READA   | Terminate Burst With DM=High,<br>Latch CA, Begin Read, Deter-<br>mine Auto-Precharge*3 |

|                                | L  | Н   | L   | L  | BA, CA, A10       | WRITE/WRITEA | Terminate Burst, Latch CA,<br>Begin new Write, Determine<br>Auto-Precharge*3           |

|                                | L  | L   | Η   | Н  | BA, RA            | Active       | Bank Active/ILLEGAL*2                                                                  |

|                                | L  | L   | Н   | L  | BA, A10           | PRE/PREA     | Terminate Burst With DM=High, Precharge                                                |

|                                | L  | L   | L   | Н  | Х                 | Refresh      | ILLEGAL                                                                                |

|                                | L  | L   | L   | L  | Op-Code, Mode-Add | MRS          | ILLEGAL                                                                                |

| READ with                      | L  | Н   | Н   | L  | Х                 | Burst Stop   | ILLEGAL                                                                                |

| AUTO<br>PRECHARGE*6            | L  | Н   | L   | Н  | BA, CA, A10       | READ/READA   | *6                                                                                     |

| (READA)                        | L  | Н   | L   | L  | BA, CA, A10       | WRITE/WRITEA | ILLEGAL                                                                                |

|                                | L  | L   | Н   | Н  | BA, RA            | Active       | *6                                                                                     |

|                                | L  | L   | Н   | L  | BA, A10           | PRE/PREA     | *6                                                                                     |

|                                | L  | L   | L   | Н  | Х                 | Refresh      | ILLEGAL                                                                                |

|                                | L  | L   | L   | L  | Op-Code, Mode-Add | MRS          | ILLEGAL                                                                                |

| WRITE with                     | L  | Н   | Н   | L  | Х                 | Burst Stop   | ILLEGAL                                                                                |

| AUTO<br>RECHARGE <sup>*7</sup> | L  | Н   | L   | Η  | BA, CA, A10       | READ/READA   | *7                                                                                     |

| (WRITEA)                       | L  | Н   | L   | L  | BA, CA, A10       | WRITE/WRITEA | *7                                                                                     |

|                                | L  | L   | Н   | Н  | BA, RA            | Active       | *7                                                                                     |

|                                | L  | L   | Η   | L  | BA, A10           | PRE/PREA     | *7                                                                                     |

|                                | L  | L   | L   | Н  | X                 | Refresh      | ILLEGAL                                                                                |

|                                | L  | L   | L   | L  | Op-Code, Mode-Add | MRS          | ILLEGAL                                                                                |

Table 9-2. Functional truth table

| Current State                   | cs | RAS | CAS | WE | Address           | Command    | Action                |

|---------------------------------|----|-----|-----|----|-------------------|------------|-----------------------|

| PRECHARG-                       | L  | Н   | Н   | L  | Х                 | Burst Stop | ILLEGAL*2             |

| ING<br>(DURING tRP)             | L  | Н   | L   | Х  | BA, CA, A10       | READ/WRITE | ILLEGAL*2             |

|                                 | L  | L   | Н   | Н  | BA, RA            | Active     | ILLEGAL*2             |

|                                 | L  | L   | Н   | L  | BA, A 10          | PRE/PREA   | NOP*4(Idle after tRP) |

|                                 | L  | L   | L   | Н  | X                 | Refresh    | ILLEGAL               |

|                                 | L  | L   | L   | L  | Op-Code, Mode-Add | MRS        | ILLEGAL               |

| ROW                             | L  | Н   | Н   | L  | Х                 | Burst Stop | ILLEGAL*2             |

| ACTIVATING (FROM ROW  ACTIVE TO | L  | Н   | L   | Х  | BA, CA, A10       | READ/WRITE | ILLEGAL*2             |

|                                 | L  | L   | Н   | Н  | BA, RA            | Active     | ILLEGAL*2             |

| tRCD)                           | L  | L   | Н   | L  | BA, A10           | PRE/PREA   | ILLEGAL*2             |

|                                 | L  | L   | L   | Н  | Х                 | Refresh    | ILLEGAL               |

|                                 | L  | L   | L   | L  | Op-Code, Mode-Add | MRS        | ILLEGAL               |

| WRITE                           | L  | Н   | Н   | L  | Х                 | Burst Stop | ILLEGAL*2             |

| RECOVERING                      | L  | Н   | L   | Η  | BA, CA, A10       | READ       | ILLEGAL*2             |

| (DURING tWR :<br>OR tCDLR)      | L  | Н   | L   | L  | BA, CA, A10       | WRITE      | WRITE                 |

|                                 | ┙  | L   | Н   | Ι  | BA, RA            | Active     | ILLEGAL*2             |

|                                 | L  | L   | Н   | L  | BA, A 10          | PRE/PREA   | ILLEGAL*2             |

|                                 | L  | L   | L   | Н  | X                 | Refresh    | ILLEGAL               |

|                                 | L  | L   | L   | L  | Op-Code, Mode-Add | MRS        | ILLEGAL               |

Table 9-3. Functional truth table

| Current State       | cs | RAS | CAS | WE | Address           | Command    | Action  |

|---------------------|----|-----|-----|----|-------------------|------------|---------|

| RE-                 | L  | Н   | Н   | L  | Х                 | Burst Stop | ILLEGAL |

| FRESHING            | L  | Н   | L   | Х  | BA, CA, A10       | READ/WRITE | ILLEGAL |

|                     | L  | L   | Н   | Η  | BA, RA            | Active     | ILLEGAL |

|                     | L  | L   | Н   | L  | BA, A10           | PRE/PREA   | ILLEGAL |

|                     | L  | L   | L   | Н  | Х                 | Refresh    | ILLEGAL |

|                     | L  | L   | L   | L  | Op-Code, Mode-Add | MRS        | ILLEGAL |

| MODE                | L  | Н   | Н   | L  | Х                 | Burst Stop | ILLEGAL |

| REGISTER<br>SETTING | L  | Н   | L   | Х  | BA, CA, A10       | READ/WRITE | ILLEGAL |

| 02111110            | L  | L   | Н   | Ι  | BA, RA            | Active     | ILLEGAL |

|                     | L  | L   | Н   | L  | BA, A 10          | PRE/PREA   | ILLEGAL |

|                     | L  | L   | L   | Н  | Х                 | Refresh    | ILLEGAL |

|                     | L  | L   | L   | L  | Op-Code, Mode-Add | MRS        | ILLEGAL |

Table 9-4. Functional truth table

| Current State            | CKE<br>n-1 | CKE<br>n | cs | RAS | CAS | WE | Add | Action                            |