CC1000

## *CC1000* Single Chip Very Low Power RF Transceiver

## **Applications**

- Very low power UHF wireless data transmitters and receivers

- 315 / 433 / 868 and 915 MHz ISM/SRD band systems

- *RKE Two-way Remote Keyless Entry*

## **Product Description**

*CC1000* is a true single-chip UHF transceiver designed for very low power and very low voltage wireless applications. The circuit is mainly intended for the ISM (Industrial, Scientific and Medical) and SRD (Short Range Device) frequency bands at 315, 433, 868 and 915 MHz, but can easily be programmed for operation at other frequencies in the 300-1000 MHz range.

The main operating parameters of *CC1000* can be programmed via a serial bus, thus making *CC1000* a very flexible and easy to use transceiver. In a typical system *CC1000* will be used together with a microcontroller and a few external passive components.

#### Features

- True single chip UHF RF transceiver

- Very low current consumption

- Frequency range 300 1000 MHz

- Integrated bit synchroniser

- High sensitivity (typical -110 dBm at 2.4 kBaud)

- Programmable output power –20 to 10 dBm

- Small size (TSSOP-28 or UltraCSP™ package)

- Low supply voltage (2.1 V to 3.6 V)

- Very few external components required

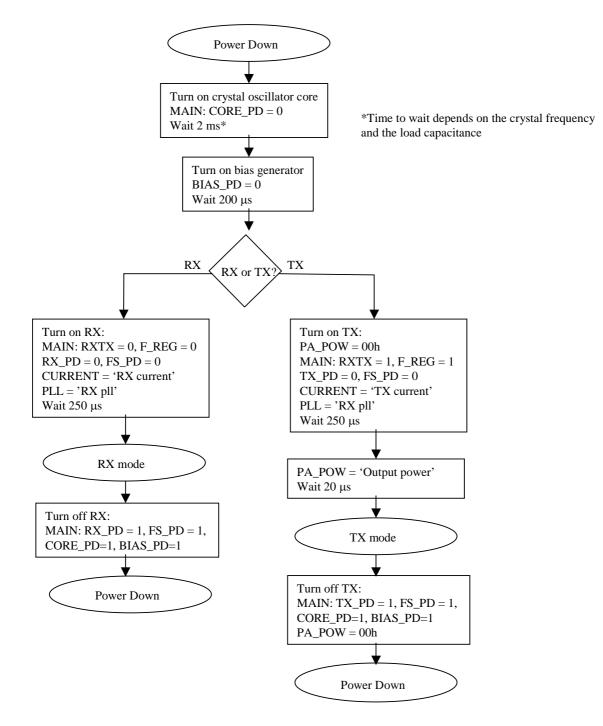

- No external RF switch / IF filter required

- Home automation

- Wireless alarm and security systems

- AMR Automatic Meter Reading

- Low power telemetry

- Game Controllers and advanced toys

*CC1000* is based on Chipcon's SmartRF<sup>®</sup> technology in 0.35  $\mu$ m CMOS.

- RSSI output

- Single port antenna connection

- FSK data rate up to 76.8 kBaud

- Complies with EN 300 220 and FCC CFR47 part 15

- Programmable frequency in 250 Hz steps makes crystal temperature drift compensation possible without TCXO

- Suitable for frequency hopping protocols

- Development kit available

- Easy-to-use software for generating the *CC1000* configuration data

## **Table of Contents**

| <i>CC1000</i>                                                                                                                                    | 1        |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Single Chip Very Low Power RF Transceiver                                                                                                        | 1        |

| 1. Absolute Maximum Ratings                                                                                                                      | 4        |

| 2. Operating Conditions                                                                                                                          | 4        |

| 3. Electrical Specifications                                                                                                                     | 4        |

| 4. Pin Assignment                                                                                                                                | 8        |

| 5. Circuit Description                                                                                                                           | 9        |

| 6. Application Circuit                                                                                                                           | 10       |

| <ul> <li>6.1 Input / output matching</li> <li>6.2 VCO inductor</li> <li>6.3 Additional filtering</li> <li>6.4 Power supply decoupling</li> </ul> | 10<br>10 |

| 7. Configuration Overview                                                                                                                        | 12       |

| 8. Configuration Software                                                                                                                        | 12       |

| 9. 3-wire Serial Configuration Interface                                                                                                         | 13       |

| Note: The set-up- and hold-times refer to 50% of VDD                                                                                             | 14       |

| 10. Microcontroller Interface                                                                                                                    | 15       |

| 10.1 Connecting the microcontroller                                                                                                              |          |

| 11. Signal interface                                                                                                                             |          |

| 11.1 Manchester encoding and decoding                                                                                                            |          |

| 12. Bit synchroniser and data decision                                                                                                           | 19       |

| 13. Receiver sensitivity versus data rate and frequency separation                                                                               | 22       |

| 14. Frequency programming                                                                                                                        | 23       |

| 15. Recommended RX settings for ISM frequencies                                                                                                  | 24       |

| 16. VCO                                                                                                                                          | 25       |

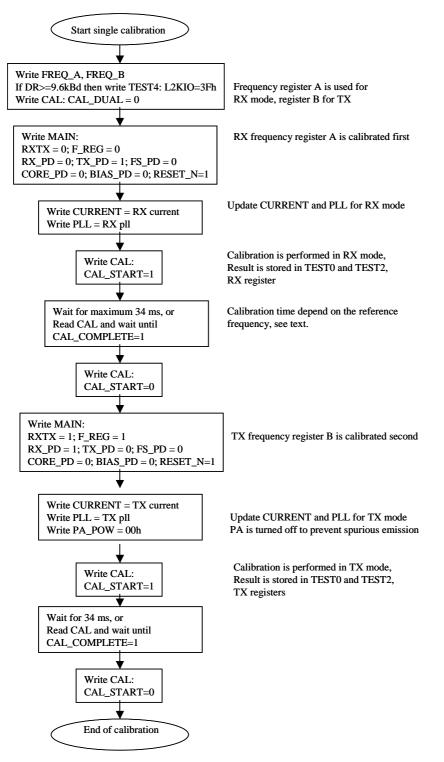

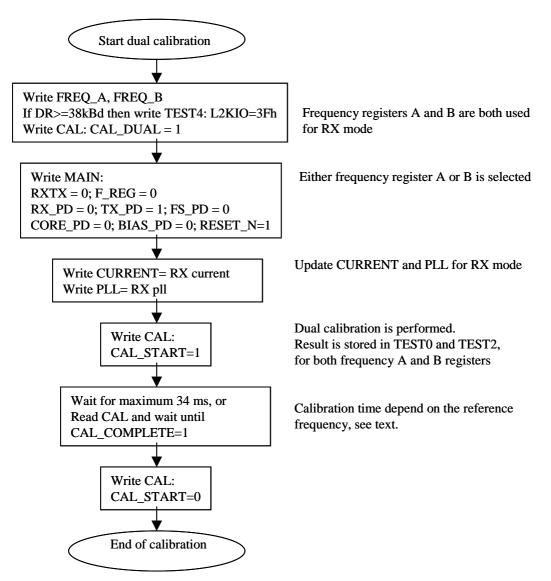

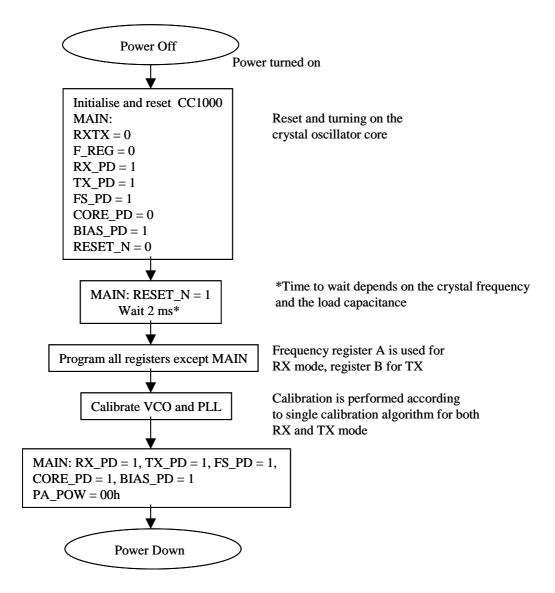

| 17. VCO and PLL self-calibration                                                                                                                 | 25       |

| 18. VCO and LNA current control                                                                                                                  | 28       |

| 19. Power management                                                                                                                             |          |

| 20. Input / Output Matching                                                                                                                                                                           | 31                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 21. Output power programming                                                                                                                                                                          | 32                                                             |

| 22. RSSI output                                                                                                                                                                                       | 33                                                             |

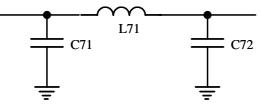

| 23. IF output                                                                                                                                                                                         | 34                                                             |

| 24. Crystal oscillator                                                                                                                                                                                | 35                                                             |

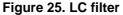

| 25. Optional LC Filter                                                                                                                                                                                | 36                                                             |

| 26. System Considerations and Guidelines                                                                                                                                                              | 37                                                             |

| 26.1 SRD regulations<br>26.2 Low cost systems<br>26.3 Battery operated systems<br>26.4 Crystal drift compensation<br>26.5 High reliability systems<br>26.6 Frequency hopping spread spectrum systems. | 37<br>37<br>37<br>37<br>37                                     |

| 27. PCB Layout Recommendations                                                                                                                                                                        | 38                                                             |

| 28. Antenna Considerations                                                                                                                                                                            | 38                                                             |

| L = 7125 / f                                                                                                                                                                                          | 38                                                             |

| L = 712371                                                                                                                                                                                            |                                                                |

| 29. Configuration registers                                                                                                                                                                           |                                                                |

|                                                                                                                                                                                                       | 39                                                             |

| 29. Configuration registers                                                                                                                                                                           | 39<br>48                                                       |

| 29. Configuration registers                                                                                                                                                                           | 39<br>48<br>49                                                 |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>49                                                 |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>49<br>51<br>51                                     |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>49<br>51<br>51<br>51                               |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>51<br>51<br>51<br>52                               |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>51<br>51<br>51<br>52<br>52                         |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>51<br>51<br>51<br>52<br>52<br>52                   |

| <ul> <li>29. Configuration registers</li></ul>                                                                                                                                                        | 39<br>48<br>51<br>51<br>51<br>51<br>52<br>52<br>52<br>52<br>52 |

#### 1. Absolute Maximum Ratings

| Parameter                                        | Min. | Max.                | Units | Condition                                   |

|--------------------------------------------------|------|---------------------|-------|---------------------------------------------|

| Supply voltage, VDD                              | -0.3 | 5.0                 | V     |                                             |

| Voltage on any pin                               | -0.3 | VDD+0.3,<br>max 5.0 | V     |                                             |

| Input RF level                                   |      | 10                  | dBm   |                                             |

| Storage temperature range (TSSOP)                | -50  | 150                 | °C    |                                             |

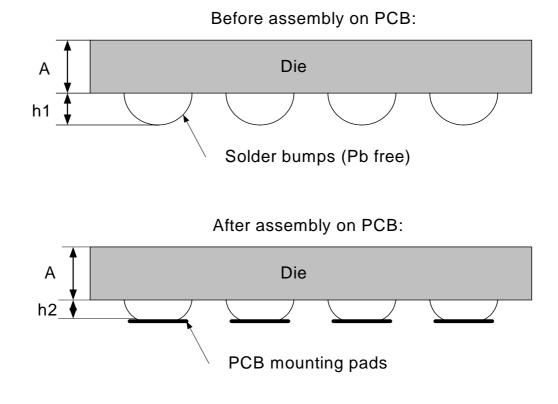

| Shelf life (UltraCSP™)                           |      | 1                   | year  | Room temperature and oxygen<br>free cabinet |

| Reflow soldering temperature (TSSOP)             |      | 260                 | °C    | IPC/JEDEC J-STD-020C                        |

| Peak reflow soldering temperature<br>(UltraCSP™) |      | 255                 | °C    | IPC/JEDEC J-STD-020C                        |

Under no circumstances the absolute maximum ratings given above should be violated. Stress exceeding one or more of

the limiting values may cause permanent damage to the device.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

## 2. Operating Conditions

| Parameter                           | Min. | Тур. | Max. | Unit | Condition / Note                                                                                 |

|-------------------------------------|------|------|------|------|--------------------------------------------------------------------------------------------------|

| RF Frequency Range                  | 300  |      | 1000 | MHz  | Programmable in steps of 250 Hz                                                                  |

| Operating ambient temperature range | -40  |      | 85   | °C   |                                                                                                  |

| Supply voltage                      | 2.1  | 3.0  | 3.6  | V    | Note: The same supply voltage<br>should be used for digital (DVDD)<br>and analogue (AVDD) power. |

## 3. Electrical Specifications

$Tc = 25^{\circ}C$ , VDD = 3.0 V if nothing else stated

| Parameter                       | Min. | Тур. | Max. | Unit  | Condition / Note                                                                                                                                                                                                          |

|---------------------------------|------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit Section                |      |      |      |       |                                                                                                                                                                                                                           |

| Transmit data rate              | 0.6  |      | 76.8 | kBaud | NRZ or Manchester encoding.<br>76.8 kBaud equals 76.8 kbit/s<br>using NRZ coding. See page 16.                                                                                                                            |

| Binary FSK frequency separation | 0    |      | 65   | kHz   | The frequency separation is<br>programmable in 250 Hz steps.<br>65 kHz is the maximum<br>guaranteed separation at 1 MHz<br>reference frequency. Larger<br>separations can be achieved at<br>higher reference frequencies. |

| Parameter                                                                                          | Min.       | Тур.                               | Max.    | Unit        | Condition / Note                                                                                                                                        |

|----------------------------------------------------------------------------------------------------|------------|------------------------------------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output power<br>433 MHz<br>868 MHz                                                                 | -20<br>-20 |                                    | 10<br>5 | dBm<br>dBm  | Delivered to 50 $\Omega$ load.<br>The output power is<br>programmable.                                                                                  |

| RF output impedance<br>433/868 MHz                                                                 |            | 140 / 80                           |         | Ω           | Transmit mode. For matching details see "Input/ output matching" p.31.                                                                                  |

| Harmonics                                                                                          |            | -20                                |         | dBc         | An external LC or SAW filter<br>should be used to reduce<br>harmonics emission to comply<br>with SRD requirements. See<br>p.36.                         |

| Receive Section                                                                                    |            |                                    |         |             |                                                                                                                                                         |

| Receiver Sensitivity, 433 MHz<br>Optimum sensitivity (9.3 mA)<br>Low current consumption (7.4 mA)  |            | -110<br>-109                       |         | dBm<br>dBm  | 2.4 kBaud, Manchester coded data, 64 kHz frequency separation, BER = 10 <sup>-3</sup>                                                                   |

| Receiver Sensitivity, 868 MHz<br>Optimum sensitivity (11.8 mA)<br>Low current consumption (9.6 mA) |            | -107<br>-105                       |         | dBm<br>dBm  | See Table 6 and Table 7 page 22 for typical sensitivity figures at other data rates.                                                                    |

| System noise bandwidth                                                                             |            | 30                                 |         | kHz         | 2.4 kBaud, Manchester coded data                                                                                                                        |

| Cascaded noise figure<br>433/868 MHz                                                               |            | 12/13                              |         | dB          |                                                                                                                                                         |

| Saturation                                                                                         | 10         |                                    |         | dBm         | 2.4 kBaud, Manchester coded data, BER = $10^{-3}$                                                                                                       |

| Input IP3                                                                                          |            | -18                                |         | dBm         | From LNA to IF output                                                                                                                                   |

| Blocking                                                                                           |            | 40                                 |         | dBc         | At +/- 1 MHz                                                                                                                                            |

| LO leakage                                                                                         |            |                                    | -57     | dBm         |                                                                                                                                                         |

| Input impedance                                                                                    |            | 88-j26<br>70-j26<br>52-j7<br>52-j4 |         | Ω<br>Ω<br>Ω | Receive mode, series equivalent<br>at 315 MHz<br>at 433 MHz<br>at 868 MHz.<br>At 915 MHz<br>For matching details see "Input/<br>output matching" p. 31. |

| Turn on time                                                                                       | 11         |                                    | 128     | Baud        | The turn-on time is determined by<br>the demodulator settling time,<br>which is programmable. See p.<br>19                                              |

| IF Section                                                                                         |            |                                    |         |             |                                                                                                                                                         |

| Intermediate frequency (IF)                                                                        |            | 150                                | 10.7    | kHz<br>MHz  | Internal IF filter<br>External IF filter                                                                                                                |

| IF bandwidth                                                                                       |            | 175                                |         | kHz         |                                                                                                                                                         |

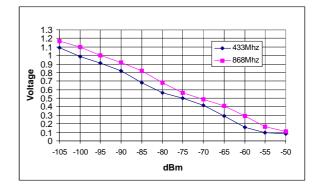

| RSSI dynamic range                                                                                 | -105       |                                    | -50     | dBm         |                                                                                                                                                         |

| RSSI accuracy                                                                                      |            | ± 6                                |         | dB          | See p.33 for details                                                                                                                                    |

| RSSI linearity                                                                                     |            | ± 2                                |         | dB          |                                                                                                                                                         |

|                                                                                                    |            |                                    |         |             |                                                                                                                                                         |

|                                                                                                    |            |                                    |         |             |                                                                                                                                                         |

| Parameter                                                     | Min.           | Тур.           | Max.           | Unit           | Condition / Note                                                                                                                                                                |

|---------------------------------------------------------------|----------------|----------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency Synthesiser<br>Section                              |                |                |                |                |                                                                                                                                                                                 |

| Crystal Oscillator Frequency                                  | 3              |                | 16             | MHz            | Crystal frequency can be 3-4, 6-8<br>or 9-16 MHz. Recommended<br>frequencies are 3.6864, 7.3728,<br>11.0592 and 14.7456. See page<br>35 for details.                            |

| Crystal frequency accuracy requirement                        |                | ± 50<br>± 25   |                | ppm            | 433 MHz<br>868 MHz<br>The crystal frequency accuracy<br>and drift (ageing and<br>temperature dependency) will<br>determine the frequency accuracy<br>of the transmitted signal. |

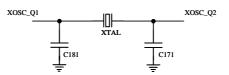

| Crystal operation                                             |                | Parallel       |                |                | C171 and C181 are loading capacitors, see page 35                                                                                                                               |

| Crystal load capacitance                                      | 12<br>12<br>12 | 22<br>16<br>16 | 30<br>30<br>16 | pF<br>pF<br>pF | 3-4 MHz, 22 pF recommended<br>6-8 MHz, 16 pF recommended<br>9-16 MHz, 16 pF recommended                                                                                         |

| Crystal oscillator start-up time                              |                | 5<br>1.5<br>2  |                | ms<br>ms<br>ms | 3.6864 MHz, 16 pF load<br>7.3728 MHz, 16 pF load<br>16 MHz, 16 pF load                                                                                                          |

| Output signal phase noise                                     |                | -85            |                | dBc/Hz         | At 100 kHz offset from carrier                                                                                                                                                  |

| PLL lock time (RX / TX turn time)                             |                | 200            |                | μS             | Up to 1 MHz frequency step                                                                                                                                                      |

| PLL turn-on time, crystal oscillator<br>on in power down mode |                | 250            |                | μS             | Crystal oscillator running                                                                                                                                                      |

| Digital Inputs/Outputs                                        |                |                |                |                |                                                                                                                                                                                 |

| Logic "0" input voltage                                       | 0              |                | 0.3*VDD        | V              |                                                                                                                                                                                 |

| Logic "1" input voltage                                       | 0.7*VDD        |                | VDD            | V              |                                                                                                                                                                                 |

| Logic "0" output voltage                                      | 0              |                | 0.4            | V              | Output current -2.5 mA,<br>3.0 V supply voltage                                                                                                                                 |

| Logic "1" output voltage                                      | 2.5            |                | VDD            | V              | Output current 2.5 mA,<br>3.0 V supply voltage                                                                                                                                  |

| Logic "0" input current                                       | NA             |                | -1             | μΑ             | Input signal equals GND                                                                                                                                                         |

| Logic "1" input current                                       | NA             |                | 1              | μΑ             | Input signal equals VDD                                                                                                                                                         |

| DIO setup time                                                | 20             |                |                | ns             | TX mode, minimum time DIO<br>must be ready before the positive<br>edge of DCLK                                                                                                  |

| DIO hold time                                                 | 10             |                |                | ns             | TX mode, minimum time DIO<br>must be held after the positive<br>edge of DCLK                                                                                                    |

| Serial interface (PCLK, PDATA and PALE) timing specification  |                |                |                |                | See Table 2 page 14                                                                                                                                                             |

| Current Consumption                                           |                |                |                |                |                                                                                                                                                                                 |

| Power Down mode                                               |                | 0.2            | 1              | μΑ             | Oscillator core off                                                                                                                                                             |

| Parameter                                                                    | Min. | Тур.            | Max. | Unit           | Condition / Note                                                                      |

|------------------------------------------------------------------------------|------|-----------------|------|----------------|---------------------------------------------------------------------------------------|

| Current Consumption,<br>receive mode 433/868 MHz                             |      | 7.4/9.6         |      | mA             | Current is programmable and can<br>be increased for improved<br>sensitivity           |

| Current Consumption,<br>average in receive mode using<br>polling 433/868 MHz |      | 74/96           |      | μΑ             | Polling controlled by micro-<br>controller using 1:100 receive to<br>power down ratio |

| Current Consumption,<br>transmit mode 433/868 MHz:                           |      |                 |      |                |                                                                                       |

| P=0.01mW (-20 dBm)                                                           |      | 5.3/8.6         |      | mA             | The ouput power is delivered to a                                                     |

| P=0.3 mW (-5 dBm)                                                            |      | 8.9/13.8        |      | mA             | $50\Omega$ load, see also p. 32                                                       |

| P=1 mW (0 dBm)                                                               |      | 10.4/16.5       |      | mA             |                                                                                       |

| P=3 mW (5 dBm)                                                               |      | 14.8/25.4       |      | mA             |                                                                                       |

| P=10 mW (10 dBm)                                                             |      | 26.7/NA         |      | mA             |                                                                                       |

| Current Consumption, crystal osc.                                            |      | 30<br>80<br>105 |      | μΑ<br>μΑ<br>μΑ | 3-8 MHz, 16 pF load<br>9-14 MHz, 12 pF load<br>14-16 MHz, 16 pF load                  |

| Current Consumption, crystal osc.<br>And bias                                |      | 860             |      | μΑ             |                                                                                       |

| Current Consumption, crystal osc., bias and synthesiser, RX/TX               |      | 4/5<br>5/6      |      | mA<br>mA       | < 500 MHz<br>> 500 MHz                                                                |

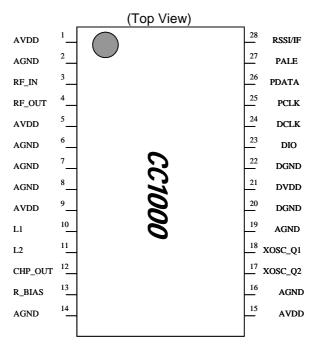

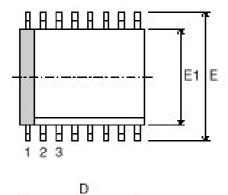

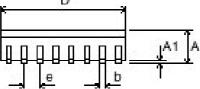

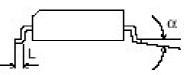

## 4. Pin Assignment

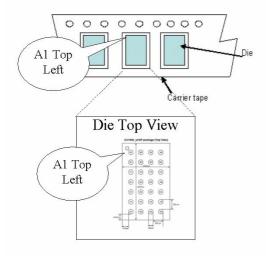

| Pin no. | UltraCSP<br>pin no. | Pin name | Pin type                | Description                                                                                                                                          |  |  |  |

|---------|---------------------|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | G3                  | AVDD     | Power (A)               | Power supply (3 V) for analog modules (mixer and IF)                                                                                                 |  |  |  |

| 2       | F2                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (mixer and IF)                                                                                            |  |  |  |

| 3       | G2                  | RF IN    | RF Input                | RF signal input from antenna                                                                                                                         |  |  |  |

| 4       | G1                  | RF OUT   | RF output               | RF signal output to antenna                                                                                                                          |  |  |  |

| 5       | F1                  | AVDD     | Power (A)               | Power supply (3 V) for analog modules (LNA and PA)                                                                                                   |  |  |  |

| 6       | E2                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (LNA and PA)                                                                                              |  |  |  |

| 7       | E1                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (PA)                                                                                                      |  |  |  |

| 8       | D1                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (VCO and prescaler)                                                                                       |  |  |  |

| 9       | C1                  | AVDD     | Power (A)               | Power supply (3 V) for analog modules (VCO and prescaler)                                                                                            |  |  |  |

| 10      | B1                  | L1       | Analog input            | Connection no 1 for external VCO tank inductor                                                                                                       |  |  |  |

| 11      | A1                  | L2       | Analog input            | Connection no 2 for external VCO tank inductor                                                                                                       |  |  |  |

| 12      | B2                  | CHP OUT  | Analog output           | Charge pump current output                                                                                                                           |  |  |  |

|         |                     | (LOCK)   |                         | The pin can also be used as PLL Lock indicator. Output is high when PLL is in lock.                                                                  |  |  |  |

| 13      | C2                  | R_BIAS   | Analog output           | Connection for external precision bias resistor (82 k $\Omega$ , ± 1%)                                                                               |  |  |  |

| 14      | F3                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (backplane)                                                                                               |  |  |  |

| 15      | A2                  | AVDD     | Power (A)               | Power supply (3 V) for analog modules (general)                                                                                                      |  |  |  |

| 16      | B3                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (general)                                                                                                 |  |  |  |

| 17      | A3                  | XOSC_Q2  | Analog output           | Crystal, pin 2                                                                                                                                       |  |  |  |

| 18      | A4                  | XOSC_Q1  | Analog input            | Crystal, pin 1, or external clock input                                                                                                              |  |  |  |

| 19      | B4                  | AGND     | Ground (A)              | Ground connection (0 V) for analog modules (guard)                                                                                                   |  |  |  |

| 20      | C3                  | DGND     | Ground (D)              | Ground connection (0 V) for digital modules (substrate)                                                                                              |  |  |  |

| 21      | C4                  | DVDD     | Power (D)               | Power supply (3 V) for digital modules                                                                                                               |  |  |  |

| 22      | D4                  | DGND     | Ground (D)              | Ground connection (0 V) for digital modules                                                                                                          |  |  |  |

| 23      | E4                  | DIO      | Digital<br>input/output | Data input/output. Data input in transmit mode. Data output in receive mode                                                                          |  |  |  |

| 24      | F4                  | DCLK     | Digital output          | Data clock for data in both receive and transmit mode                                                                                                |  |  |  |

| 25      | G4                  | PCLK     | Digital input           | Programming clock for 3-wire bus                                                                                                                     |  |  |  |

| 26      | D3                  | PDATA    | Digital                 | Programming data for 3-wire bus. Programming data input for                                                                                          |  |  |  |

|         | 20                  |          | input/output            | write operation, programming data output for read operation                                                                                          |  |  |  |

| 27      | D2                  | PALE     | Digital input           | Programming address latch enable for 3-wire bus. Internal pull-up.                                                                                   |  |  |  |

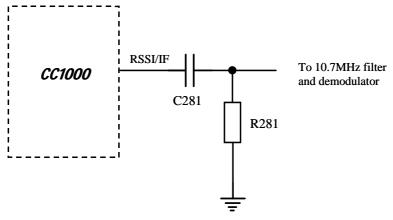

| 28      | E3                  | RSSI/IF  | Analog output           | The pin can be used as RSSI or 10.7 MHz IF output to optional external IF and demodulator. If not used, the pin should be left open (not connected). |  |  |  |

A=Analog, D=Digital

#### 5. Circuit Description

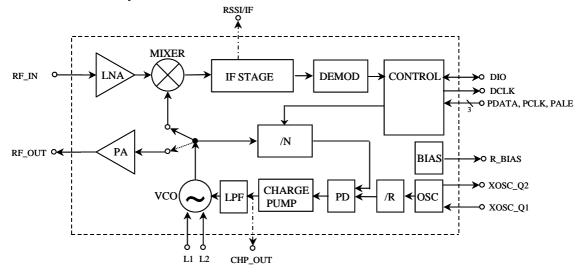

Figure 1. Simplified block diagram of the CC1000

A simplified block diagram of *CC1000* is shown in Figure 1. Only signal pins are shown.

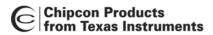

In receive mode *CC1000* is configured as a traditional superheterodyne receiver. The RF input signal is amplified by the lownoise amplifier (LNA) and converted down to the intermediate frequency (IF) by the mixer (MIXER). In the intermediate stage (IF STAGE) frequency this downconverted signal is amplified and filtered before being fed to the demodulator (DEMOD). As an option a RSSI signal, or the IF signal after the mixer is available at the RSSI/IF pin. After demodulation CC1000 outputs the digital demodulated data on the pin DIO. Synchronisation is done on-chip providing data clock at DCLK.

In transmit mode the voltage controlled oscillator (VCO) output signal is fed directly to the power amplifier (PA). The RF output is frequency shift keyed (FSK) by the digital bit stream fed to the pin DIO. The internal T/R switch circuitry makes the antenna interface and matching very easy.

The frequency synthesiser generates the local oscillator signal which is fed to the MIXER in receive mode and to the PA in transmit mode. The frequency synthesiser consists of a crystal oscillator (XOSC), phase detector (PD), charge pump (CHARGE PUMP), VCO, and frequency dividers (/R and /N). An external crystal must be connected to XOSC, and only an external inductor is required for the VCO.

The 3-wire digital serial interface (CONTROL) is used for configuration.

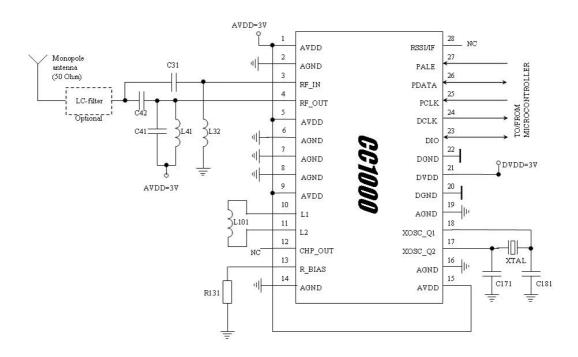

#### 6. Application Circuit

Very few external components are required for the operation of *CC1000*. A typical application circuit is shown in Figure 2. Component values are shown in Table 1.

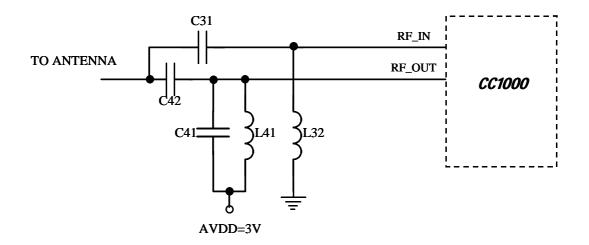

#### 6.1 Input / output matching

C31/L32 is the input match for the receiver. L32 is also a DC choke for biasing. C41, L41 and C42 are used to match the transmitter to 50  $\Omega$ . An internal T/R switch circuit makes it possible to connect the input and output together and match the *CC1000* to 50  $\Omega$  in both RX and TX mode. See "Input/output matching" p.31 for details.

#### 6.2 VCO inductor

The VCO is completely integrated except for the inductor L101.

Component values for the matching network and VCO inductor are easily calculated using the SmartRF® Studio software.

#### 6.3 Additional filtering

Additional external components (e.g. RF LC or SAW-filter) may be used in order to improve the performance in specific applications. See also "Optional LC filter" p.36 for further information.

#### 6.4 Power supply decoupling

Power supply decoupling and filtering must be used (not shown in the application circuit). The placement and size of the decoupling capacitors and the power supply filtering are very important to achieve the optimum performance. Chipcon provides reference designs (CC1000PP and CC1000uCSP\_EM) that should be followed very closely.

Figure 2. Typical *CC1000* application circuit (power supply decoupling not shown)

|   | Chipcon  | Produ    | cts<br>truments |

|---|----------|----------|-----------------|

| C | from Tex | xas Inst | truments        |

| CC1000 TSSOP package |                                                    |                                                     |                                                     |                                                     |  |  |  |

|----------------------|----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--|--|--|

| Item                 | 315 MHz                                            | 433 MHz                                             | 868 MHz                                             | 915 MHz                                             |  |  |  |

| C31                  | 8.2 pF, 5%, C0G, 0603                              | 15 pF, 5%, C0G, 0603                                | 10 pF, 5%, C0G, 0603                                | 10 pF, 5%, C0G, 0603                                |  |  |  |

| C41                  | 2.2 pF, 5%, C0G, 0603                              | 8.2 pF, 5%, C0G, 0603                               | Not used                                            | Not used                                            |  |  |  |

| C42                  | 5.6 pF, 5%, C0G, 0603                              | 5.6 pF, 5%, C0G, 0603                               | 4.7 pF, 5%, C0G, 0603                               | 4.7 pF, 5%, C0G, 0603                               |  |  |  |

| C171                 | 18 pF, 5%, C0G, 0603                               | 18 pF, 5%, C0G, 0603                                | 18 pF, 5%, C0G, 0603                                | 18 pF, 5%, C0G, 0603                                |  |  |  |

| C181                 | 18 pF, 5%, C0G, 0603                               | 18 pF, 5%, C0G, 0603                                | 18 pF, 5%, C0G, 0603                                | 18 pF, 5%, C0G, 0603                                |  |  |  |

| L32                  | 39 nH, 10%, 0805<br>(Coilcraft 0805CS-390XKBC)     | 68 nH, 10%, 0805<br>(Coilcraft 0805CS-680XKBC)      | 120 nH, 10%, 0805<br>(Coilcraft 0805CS-121XKBC)     | 120 nH, 10%, 0805<br>(Coilcraft 0805CS-121XKBC)     |  |  |  |

| L41                  | 20 nH, 10%, 0805<br>(Coilcraft 0805HQ-<br>20NXKBC) | 6.2 nH, 10%, 0805<br>(Coilcraft 0805HQ-<br>6N2XKBC) | 2.5 nH, 10%, 0805<br>(Coilcraft 0805HQ-<br>2N5XKBC) | 2.5 nH, 10%, 0805<br>(Coilcraft 0805HQ-<br>2N5XKBC) |  |  |  |

| L101                 | 56 nH, 5%, 0805<br>(Koa KL732ATE56NJ)              | 33 nH, 5%, 0805<br>(Koa KL732ATE33NJ)               | 4.7 nH, 5%, 0805<br>(Koa KL732ATE4N7C)              | 4.7 nH, 5%, 0805<br>(Koa KL732ATE4N7C)              |  |  |  |

| R131                 | 82 kΩ, 1%, 0603                                    | 82 kΩ, 1%, 0603                                     | 82 kΩ, 1%, 0603                                     | 82 kΩ, 1%, 0603                                     |  |  |  |

| XTAL                 | 14.7456 MHz crystal,                               | 14.7456 MHz crystal,                                | 14.7456 MHz crystal,                                | 14.7456 MHz crystal,                                |  |  |  |

|                      | 16 pF load                                         | 16 pF load                                          | 16 pF load                                          | 16 pF load                                          |  |  |  |

| CC1000 UltraCSP™ package |                       |                       |                       |                       |  |  |  |  |

|--------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| ltem                     | 315 MHz               | 433 MHz               | 868 MHz               | 915 MHz               |  |  |  |  |

| C31                      | 8.2 pF, 5%, C0G, 0402 | 15 pF, 5%, C0G, 0402  | 10 pF, 5%, C0G, 0402  | 10 pF, 5%, C0G, 0402  |  |  |  |  |

| C41                      | Not used              | Not used              | Not used              | Not used              |  |  |  |  |

| C42                      | 4.7 pF, 5%, C0G, 0402 | 4.7 pF, 5%, C0G, 0402 | 6.8 pF, 5%, C0G, 0402 | 6.8 pF, 5%, C0G, 0402 |  |  |  |  |

| C171                     | 18 pF, 5%, C0G, 0402  |  |  |  |  |

| C181                     | 18 pF, 5%, C0G, 0402  |  |  |  |  |

| L32                      | 39 nH, 5%, 0402       | 68 nH, 5%, 0402       | 120 nH, 5%, 0402      | 120 nH, 5%, 0402      |  |  |  |  |

|                          | (Ceramic multilayer)  | (Ceramic multilayer)  | (Ceramic multilayer)  | (Ceramic multilayer)  |  |  |  |  |

| L41                      | 22 nH, 5%, 0402       | 15 nH, 5%, 0402       | 2.7 nH, 5%, 0402      | 2.7 nH, 5%, 0402      |  |  |  |  |

|                          | (Ceramic multilayer)  | (Ceramic multilayer)  | (Ceramic multilayer)  | (Ceramic multilayer)  |  |  |  |  |

| L101                     | 56 nH, 5%, 0402       | 33 nH, 5%, 0402       | 7.5 nH, 5%, 0402      | 7.5 nH, 5%, 0402      |  |  |  |  |

|                          | (Thin film inductor)  | (Thin film inductor)  | (Thin film inductor)  | (Thin film inductor)  |  |  |  |  |

| R131                     | 82 kΩ, 1%, 0402       |  |  |  |  |

| XTAL                     | 14.7456 MHz crystal,  | 14.7456 MHz crystal,  | 14.7456 MHz crystal,  | 14.7456 MHz crystal,  |  |  |  |  |

|                          | 16 pF load            | 16 pF load            | 16 pF load            | 16 pF load            |  |  |  |  |

Note: Items shaded are different for different frequencies

#### Table 1. Bill of materials for the application circuit

Note that the component values for 868/915 MHz can be the same. However, it is important the layout is optimised for the selected VCO inductor in order to centre the tuning range around the operating frequency to account for inductor tolerance. The VCO inductor must be placed very close and symmetrical with respect to the pins (L1 and L2).

Chipcon provide reference layouts that should be followed very closely in order to achieve the best performance. The reference design can be downloaded from the Chipcon website.

#### 7. Configuration Overview

*CC1000* can be configured to achieve the best performance for different applications. Through the programmable configuration registers the following key parameters can be programmed:

- Receive / transmit mode

- RF output power

- Frequency synthesiser key parameters: RF output frequency, FSK

#### 8. Configuration Software

Chipcon provides users of *CC1000* with a software program, SmartRF® Studio (Windows interface) that generates all necessary *CC1000* configuration data based on the user's selections of various parameters. These hexadecimal numbers will then be the necessary input to the microcontroller for the configuration of

frequency separation (deviation), crystal oscillator reference frequency

- Power-down / power-up mode

- Crystal oscillator power-up / power down

- Data rate and data format (NRZ, Manchester coded or UART interface)

- Synthesiser lock indicator mode

- Optional RSSI or external IF

*CC1000.* In addition the program will provide the user with the component values needed for the input/output matching circuit and the VCO inductor.

Figure 3 shows the user interface of the *CC1000* configuration software.

| CC1000 - SmartRF Studio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eile View Configuration Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                               |

| System parameters         info       X-tal frequency         14.745600       MHz         info       X-tal frequency         14.745600       MHz         info       X-tal frequency         info       RF freq.         A       668.297200         MHz       R x         T x       B         B       668.297200         MHZ       R x         T x       B         Info       Freq. separation         64       KHz         info       Data rate         2.400       KBaud         info       Data Format         Manchester       C         Fast       Accurate         info       Lock Indicator         Continuous       Info         info       Mode         FX       Info | Component values           info         VC0:           L101         4.7           nH         info           Match:         L32           L32         120.0           L41         2.5           C31         10.0           PF           C41         NA           C42         4.7           PF           C42         4.7           PF           C42         4.7           PF           Calibrate           Read |

| Status information<br>Typical current consumption 12.00000 mA<br>Lock indicator Not Locked<br>Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Chipcon.com                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 3. SmartRF® Studio user interface

#### 9. 3-wire Serial Configuration Interface

CC1000 is configured via a simple 3-wire interface (PDATA, PCLK and PALE). There are 28 8-bit configuration registers, each addressed by a 7-bit address. A Read/Write bit initiates a read or write operation. A full configuration of CC1000 requires sending 22 data frames of 16 bits each (7 address bits, R/W bit and 8 data bits). The time needed for a full configuration depend on the PCLK frequency. With a PCLK frequency of 10 MHz the full configuration is done in less than 46 µs. Setting the device in power down mode requires sending one frame only and will in this case take less than 2 us. All registers are also readable.

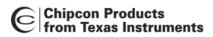

In each write-cycle 16 bits are sent on the PDATA-line. The seven most significant bits of each data frame (A6:0) are the address-bits. A6 is the MSB (Most Significant Bit) of the address and is sent as the first bit. The next bit is the R/W bit (high for write, low for read). During address and R/W bit transfer the PALE (Program Address Latch Enable) must be kept low. The 8 data-bits are then transferred (D7:0). See Figure 4.

The timing for the programming is also shown in Figure 4 with reference to Table 2. The clocking of the data on PDATA is done on the negative edge of PCLK. When the last bit, *D0*, of the 8 data-bits has been loaded, the data word is loaded in the internal configuration register.

The configuration data is stored in internal RAM. The data is retained during powerdown mode, but not when the powersupply is turned off. The registers can be programmed in any order.

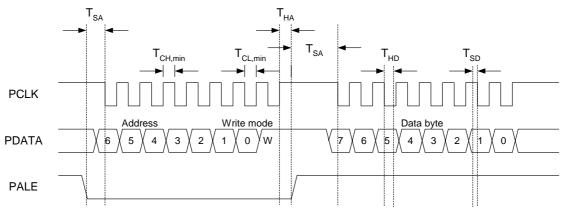

The configuration registers can also be read by the microcontroller via the same configuration interface. The seven address bits are sent first, then the R/W bit set <u>low</u> to initiate the data read-back. *CC1000* then returns the data from the addressed register. PDATA is in this case used as an output and must be tri-stated (or set high n the case of an open collector pin) by the microcontroller during the data read-back (D7:0). The read operation is illustrated in Figure 5.

Figure 4. Configuration registers write operation

Figure 5. Configuration registers read operation

| Parameter                      | Symbol              | Min | Мах | Units | Conditions                                                                     |

|--------------------------------|---------------------|-----|-----|-------|--------------------------------------------------------------------------------|

| PCLK, clock<br>frequency       | F <sub>с∟оск</sub>  | -   | 10  | MHz   |                                                                                |

| PCLK low<br>pulse<br>duration  | $T_{CL,min}$        | 50  |     | ns    | The minimum time PCLK must be low.                                             |

| PCLK high<br>pulse<br>duration | T <sub>CH,min</sub> | 50  |     | ns    | The minimum time PCLK must be high.                                            |

| PALE setup<br>time             | T <sub>SA</sub>     | 10  | -   | ns    | The minimum time PALE must be low before negative edge of PCLK.                |

| PALE hold<br>time              | T <sub>HA</sub>     | 10  | -   | ns    | The minimum time PALE must be held low after the <i>positive</i> edge of PCLK. |

| PDATA setup time               | T <sub>SD</sub>     | 10  | -   | ns    | The minimum time data on PDATA must be ready before the negative edge of PCLK. |

| PDATA hold<br>time             | T <sub>HD</sub>     | 10  | -   | ns    | The minimum time data must be held at PDATA, after the negative edge of PCLK.  |

| Rise time                      | T <sub>rise</sub>   |     | 100 | ns    | The maximum rise time for PCLK and PALE                                        |

| Fall time                      | T <sub>fall</sub>   |     | 100 | ns    | The maximum fall time for PCLK and PALE                                        |

Note: The set-up- and hold-times refer to 50% of VDD.

Table 2. Serial interface, timing specification

#### **10. Microcontroller Interface**

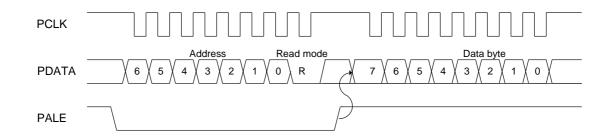

Used in a typical system, *CC1000* will interface to a microcontroller. This microcontroller must be able to:

- Program *CC1000* into different modes via the 3-wire serial configuration interface (PDATA, PCLK and PALE).

- Interface to the bi-directional synchronous data signal interface (DIO and DCLK).

#### **10.1 Connecting the microcontroller**

The microcontroller uses 3 output pins for the configuration interface (PDATA, PCLK and PALE). PDATA should be a bidirectional pin for data read-back. A bidirectional pin is used for data (DIO) to be transmitted and data received. DCLK providing the data timing should be connected to a microcontroller input. Optionally another pin can be used to monitor the LOCK signal (available at the CHP\_OUT pin). This signal is logic level high when the PLL is in lock. See **Figure 6**.

Also the RSSI signal can be connected to the microcontroller if it has an analogue ADC input.

- Optionally the microcontroller can do data encoding / decoding.

- Optionally the microcontroller can monitor the frequency lock status from pin CHP\_OUT (LOCK).

- Optionally the microcontroller can monitor the RSSI output for signal strength acquisition.

The microcontroller pins connected to PDATA and PCLK can be used for other purposes when the configuration interface is not used. PDATA and PCLK are high impedance inputs as long as PALE is high.

PALE has an internal pull-up resistor and should be left open (tri-stated by the microcontroller) or set to a high level during power down mode in order to prevent a trickle current flowing in the pullup. The pin state in power down mode is summarized in Table 3.

| Pin   | Pin state                                | Note                                                                  |

|-------|------------------------------------------|-----------------------------------------------------------------------|

| PDATA | Input                                    | Should be driven high or low                                          |

| PCLK  | Input                                    | Should be driven high or low                                          |

| PALE  | Input with internal pull-<br>up resistor | Should be driven high or high-impedance to minimize power consumption |

| DIO   | Input                                    | Should be driven high or low                                          |

| DCLK  | High-impedance                           |                                                                       |

|       | output                                   |                                                                       |

#### Table 3. CC1000 pins in power-down mode

Figure 6. Microcontroller interface

## 11. Signal interface

The signal interface consists of DIO and DCLK and is used for the data to be transmitted and data received. DIO is the bi-directional data line and DCLK provides a synchronous clock both during data transmission and data reception.

The CC1000 can be used with NRZ (Non-Return-to-Zero) data or Manchester (also known as bi-phase-level) encoded data. CC1000 can also synchronise the data from the demodulator and provide the data clock at DCLK.

CC1000 can be configured for three different data formats:

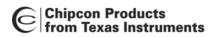

Synchronous NRZ mode. In transmit mode *CC1000* provides the data clock at DCLK, and DIO is used as data input. Data is clocked into *CC1000* at the rising edge of DCLK. The data is modulated at RF without encoding. CC1000 can be configured for the data rates 0.6, 1.2, 2.4, 4.8, 9.6, 19.2, 38.4 or 76.8 kbit/s. For 38.4 and 76.8 kbit/s a crystal frequency of 14,7456 MHz must be used. In receive mode *CC1000* does the synchronisation and provides received data clock at DCLK and data at DIO. The data should be clocked into the interfacing circuit at the rising edge of DCLK. See Figure 7.

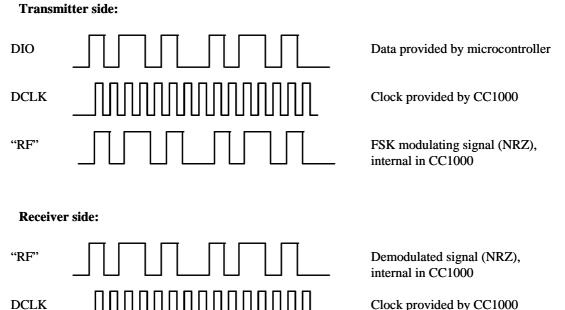

Synchronous Manchester encoded mode. In transmit mode *CC1000* provides the data clock at DCLK, and DIO is used as data input. Data is clocked into CC1000 at the rising edge of DCLK and should be in NRZ format. The data is modulated at RF with Manchester code. The encoding is done by CC1000. In this mode CC1000 can be configured for the data rates 0.3, 0.6, 1.2, 2.4, 4.8, 9.6, 19.2 or 38.4 kbit/s. The 38.4 kbit/s rate corresponds to the maximum 76.8 kBaud due to the Manchester encoding. For 38.4 and 76.8 kBaud a crystal frequency of 14.7456 MHz must be used. In receive mode CC1000 does the synchronisation and provides received data clock at DCLK and data at DIO. *CC1000* does the decoding and NRZ data

is presented at DIO. The data should be clocked into the interfacing circuit at the rising edge of DCLK. See Figure 8.

Transparent Asynchronous UART mode. In transmit mode DIO is used as data input. The data is modulated at RF without synchronisation or encoding. In receive mode the raw data signal from the demodulator is sent to the output. No synchronisation or decoding of the signal is done in CC1000 and should be done by the interfacing circuit. The DCLK pin is used as data output in this mode. Data rates in the range from 0.6 to 76.8 kBaud can be used. For 38.4 and 76.8 kBaud a crystal frequency of 14.7456 MHz must be used. See Figure 9.

#### 11.1 Manchester encoding and decoding

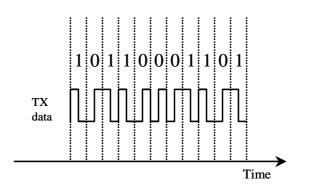

In the Synchronous Manchester encoded mode CC1000 uses Manchester coding when modulating the data. The CC1000 also performs the data decoding and synchronisation. The Manchester code is based on transitions; a "0" is encoded as a low-to-high transition, a "1" is encoded as a high-to-low transition. See Figure 10.

The CC1000 can detect a Manchester decoding violation and will set a Manchester Violation Flag when such a violation is detected in the incoming signal. The threshold limit for the Manchester Violation can be set in the *MODEM1* register. The Manchester Violation Flag can be monitored at the CHP\_OUT (LOCK) pin, configured in the LOCK register.

The Manchester code ensures that the signal has a constant DC component, which is necessary in some FSK demodulators. Using this mode also ensures compatibility with CC400/CC900 designs.

DIO

Clock provided by CC1000

Data provided by CC1000

Figure 7. Synchronous NRZ mode

| Transn  | nitter side: |                                                                            |

|---------|--------------|----------------------------------------------------------------------------|

| DIO     |              | Data provided by UART (TXD)                                                |

| DCLK    |              | DCLK is not used in transmit mode.<br>Used as data output in receive mode. |

| "RF"    |              | FSK modulating signal,<br>internal in CC1000                               |

| Receive | er side:     |                                                                            |

| "RF"    |              | Demodulated signal,<br>internal in CC1000                                  |

| DIO     |              | DIO is not used in receive mode. Used only as data input in transmit mode. |

| DCLK    |              | Data output provided by CC1000.<br>Connect to UART (RXD).                  |

Figure 9. Transparent Asynchronous UART mode

Figure 10. Manchester encoding

#### 12. Bit synchroniser and data decision

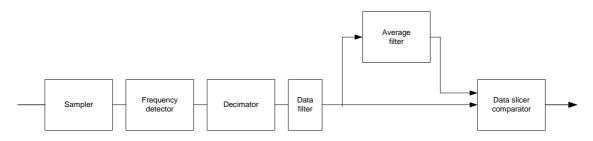

Figure 11. Demodulator block diagram

A block diagram of the digital demodulator is shown in Figure 11. The IF signal is sampled and its instantaneous frequency is detected. The result is decimated and filtered. In the data slicer the data filter output is compared to the average filter output to generate the data output.

The averaging filter is used to find the average value of the incoming data. While the averaging filter is running and acquiring samples, it is important that the number of high and low bits received is equal (e.g. Manchester code or a balanced preamble).

Therefore all modes, also synchronous NRZ mode, need a DC balanced preamble for the internal data slicer to acquire correct comparison level from the averaging filter. The suggested preamble is a '010101...' bit pattern. The same bit pattern should also be used in Manchester mode, giving a '011001100110...chip pattern. This is necessary for the bit synchronizer to synchronize correctly.

The averaging filter must be locked before any NRZ data can be received. If the averaging filter is locked (MODEM1.LOCK\_AVG\_MODE='1'), the acquired value will be kept also after Power Down or Transmit mode. After a modem reset (*MODEM1.MODEM\_RESET\_N*), or a main reset (using any of the standard reset sources), the averaging filter is reset.

In a polled receiver system the automatic locking can be used. This is illustrated in Figure 12. If the receiver is operated continuously and searching for a preamble, the averaging filter should be locked manually as soon as the preamble is detected. This is shown in Figure 13. If the data is Manchester coded there is no need to lock the averaging filter (MODEM1.LOCK\_AVG\_IN='0'), as shown in Figure 14.

The minimum length of the preamble depends on the acquisition mode selected and the settling time. Table 4 gives the minimum recommended number of chips for the preamble in NRZ and UART modes. In this context 'chips' refer to the data coding. Using Manchester coding every bit consists of two 'chips'. For Manchester mode the minimum recommended number of chips is shown in Table 5.

| Settling | Manua                            | al Lock                          | Automatic Lock |               |  |  |

|----------|----------------------------------|----------------------------------|----------------|---------------|--|--|

|          | NRZ mode                         | UART mode                        | NRZ mode       | UART mode     |  |  |

|          |                                  |                                  |                |               |  |  |

| MODEM1.  | MODEM1.LOCK_                     | MODEM1.LOCK_                     | MODEM1.LOCK_   | MODEM1.LOCK_  |  |  |

| SETTLING | AVG_MODE='1'                     | AVG_MODE='1'                     | AVG_MODE='0'   | AVG_MODE='0'  |  |  |

| (1:0)    | MODEM1.LOCK_                     | MODEM1.LOCK_                     | MODEM1.LOCK_   | MODEM1.LOCK_  |  |  |

|          | $AVG_IN='0'=\rightarrow'1'^{**}$ | $AVG_IN='0'=\rightarrow'1'^{**}$ | AVG_IN='X'***  | AVG_IN='X'*** |  |  |

| 00       | 14                               | 11                               | 16             | 16            |  |  |

| 01       | 25                               | 22                               | 32             | 32            |  |  |

| 10       | 46                               | 43                               | 64             | 64            |  |  |

| 11       | 89                               | 86                               | 128            | 128           |  |  |

Notes:

\*\* The averaging filter is locked when MODEM1.LOCK\_AVG\_IN is set to 1

\*\*\* X = Do not care. The timer for the automatic lock is started when RX mode is set in the **RFMAIN** register

Also please note that in addition to the number of bits required to lock the filter, you need to add the number of bits needed for the preamble detector. See the next section for more information.

#### Table 4. Minimum preamble bits for locking the averaging filter, NRZ and UART mode

| Settling                     | Free-running<br>Manchester mode                            |

|------------------------------|------------------------------------------------------------|

| MODEM1.<br>SETTLING<br>(1:0) | MODEM1.LOCK_<br>AVG_MODE='1'<br>MODEM1.LOCK_<br>AVG_IN='0' |

| 00                           | 23                                                         |

| 01                           | 34                                                         |

| 10                           | 55                                                         |

| 11                           | 98                                                         |

Table 5. Minimum number preamble chips for averaging filter, Manchester mode

| Data package to be received           |                            |                      |                                 |          |       |  |  |

|---------------------------------------|----------------------------|----------------------|---------------------------------|----------|-------|--|--|

|                                       | Noise                      | F                    | Preamble                        | NRZ data | Nois  |  |  |

|                                       | RX PD                      | ·                    | RX                              |          | 1     |  |  |

|                                       |                            |                      | Averaging filter locked         |          | ]     |  |  |

| Averaging filter<br>free-running / no | ot used                    |                      |                                 |          |       |  |  |

|                                       |                            | -                    | ked after a short period depend | -        |       |  |  |

|                                       | Figure 12. Autor           | natic locki          | ng of the averaging filte       | r        |       |  |  |

|                                       |                            |                      |                                 |          |       |  |  |

|                                       |                            |                      |                                 |          |       |  |  |

|                                       |                            |                      | Data package to be receive      | ed       |       |  |  |

|                                       |                            | •                    | Data package to be receive      |          | •     |  |  |