SLUS446B - MAY 2000 - REVISED DECEMBER 2000

- 2.5-V to 9-V Input Range

- 0.8-V to 8-V Output Range

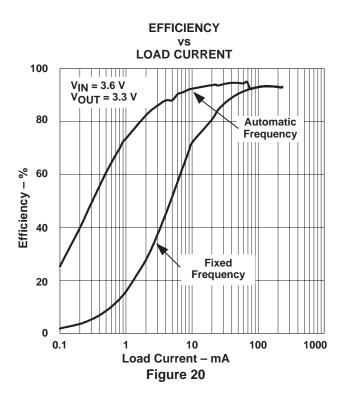

- Dual-Auto-Mode for High-Efficiency at Light Loads

- Externally Synchronizable

- 0% to 100% Duty Cycle

- Low-Quiescient, Standby, and Shutdown Currents

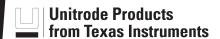

- 8-Pin SOIC Package

- Four PWM Frequency Versions (Maximum 2 MHz)

#### applications

- Cellular Telephones

- Satellite Telephones

- GPS Devices

- Digital Still Cameras

- PDAs and Handheld Cameras

#### description

The TPS6210x family of low-power high-efficiency buck converters is designed to operate from 1 or 2 li-ion cell battery packs. This part, with its wide input range of 2.5 V to 9 V, has an adjustable output from 0.8 V to 8 V and is capable of 500-mA output current. The TPS6210x family of synchronizable dc-to-dc converters is available in four different operating frequencies: 300 kHz, 600 kHz, 1 MHz, and 2 MHz. The circuit can be allowed to run at a fixed frequency, or sychronized, using the dual function SD/SYNC input pin.

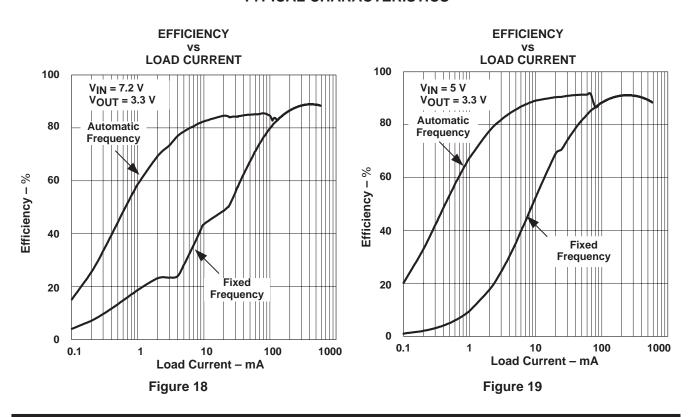

The TPS6210x family is highly efficient at both low and high output currents. The tri-function MODE input pin is used to select constant-frequency, auto-mode, or light-load modes of operation. The multimode operation allows the IC to select the most efficient operating mode, or if desirable, the user can determine which of three modes to operate in. In the auto-mode, the output load detector circuitry determines if the converter should be running in the constant-frequency, heavy-load mode, or pulsed-variable frequency, light-load mode.

The TPS6210x family also has a shutdown mode for optimum battery shelf life. The IC utilizes three methods of overload protection, including thermal shutdown and two levels of overcurrent protection. The TPS6210x is available in the small outline 8-pin SOIC package.

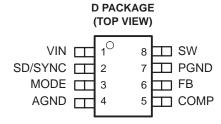

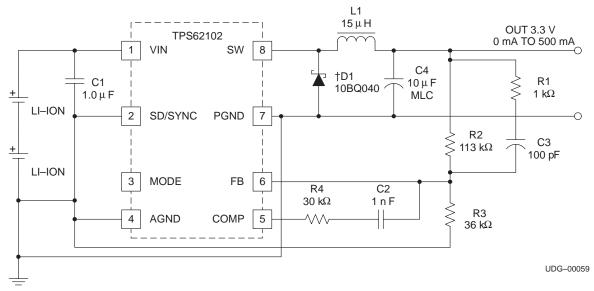

#### typical application (automatic mode switcher)

UDG-00059

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

n/TI

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

#### AVAILABLE OPTIONS $^{\dagger}$

| т.                                                | ODED ATING EDECLIENCY | PACKAGED DEVICES |  |  |

|---------------------------------------------------|-----------------------|------------------|--|--|

| TA                                                | OPERATING FREQUENCY   | SOIC (D)         |  |  |

|                                                   | 300 kHz               | TPS62100D        |  |  |

| T. 400C to 050C                                   | 600 kHz               | TPS62101D        |  |  |

| $T_A = -40^{\circ}\text{C to }85^{\circ}\text{C}$ | 1 MHz                 | TPS62102D        |  |  |

|                                                   | 2 MHz                 | TPS62103D        |  |  |

<sup>&</sup>lt;sup>†</sup> The D package is available taped and reeled. Add R suffix to device type (e.g. TPS62100DTR) to order quantities of 3000 devices per reel.

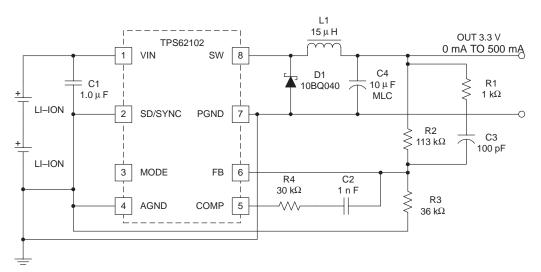

#### functional block diagram

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†‡

| VIN input supply voltage                    |

|---------------------------------------------|

| SD/SYNC input voltage –0.3 V to VIN + 0.3 V |

| MODE input voltage –0.3 V to VIN + 0.3 V    |

| COMP input voltage                          |

| SW output voltage0.3 V to VIN + 0.3 V       |

| SW output current                           |

| Operating junction temperature              |

| Storage temperature                         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                                                  | MIN | MAX | UNIT |

|--------------------------------------------------|-----|-----|------|

| Input voltage, VIN, SD/SYNC, MODE                |     | 9   | V    |

| Regulated output voltage                         |     | 8   | V    |

| Average output current, IOUT§                    |     | 500 | mA   |

| Operating junction temperature, T <sub>J</sub> § | -40 | 85  | °C   |

<sup>§</sup> It is not recommended that the device operate under conditions beyond those specified in this table for extended periods of time.

#### **Terminal Functions**

| TERMIN  | IAL |     | DECORPTION                                                                                                                                                                                                                                                                                                                       |

|---------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                      |

| COMP    | 5   | 0   | Output of the error amplifier. The loop compensation network connects between this pin and FB. When the converter enters the light-load mode, this pin goes into a high-impedance state                                                                                                                                          |

| FB      | 6   | 1   | Feedback voltage input. In the constant-frequency mode, the output duty cycle is varied to keep this pin at 800 mV. In light-load mode, this pin is kept between 785 mV and 815 mV. If this pin falls below 770 mV while the converter is in auto mode and light-load mode, the converter re-enters the constant-frequency mode. |

| AGND    | 4   |     | Reference point for the internal reference and all thresholds, as well as the return for the remainder of the device.                                                                                                                                                                                                            |

| MODE    | 3   | ı   | This pin allows the user to program the IC into one of three operating modes. Driving the pin high forces the converter into the constant-frequency mode. Driving the pin low forces it into the low-power mode. Letting the pin float puts the converter into the auto mode.                                                    |

| PGND    | 7   |     | Return for all high-level currents.                                                                                                                                                                                                                                                                                              |

| SD/SYNC | 2   | ı   | This dual function pin serves as the SYNC and SHUTDOWN input. To synchronize the internal clock, this pin must be driven from 0 V to 2 V. The clock syncs on the rising edge of the input pulse. To shutdown the converter, this pin must be driven high for more than 20 $\mu$ s.                                               |

| sw      | 8   | 0   | This is the PWM power output of the converter and is connected to an L-C (inductor-capacitor) filter and a Schottky catch diode.                                                                                                                                                                                                 |

| VIN     | 1   | I   | Input to the converter.                                                                                                                                                                                                                                                                                                          |

<sup>‡</sup> Unless otherwise noted, voltages are reference to ground and currents are positive into and negative out of the specified terminals. Pulsed is defined as a less than 10% duty cycle with a maximum duration of 500 µs. Consult the Packaging Section of the *Portable Products Data Book* (TI Literature No. SLUD001) for thermal limitations and considerations of the package.

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

electrical characteristics over recommended operating free-air temperature range,  $T_A = -40\,$  C to 85 C,  $T_A = T_J$ , typical values are at  $T_A = 25\,$  C,  $V_{IN} = 7.2\,$  V, MODE = 1 (constant frequency), SD/SYNC = 0 V. (unless otherwise noted)

| PARAMETER                                    | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|------------------------------------------------------------------|------|------|------|-------|

| Input Supply Section                         |                                                                  |      |      |      |       |

| VIN operating range                          |                                                                  | 2.5  | 7.2  | 9    | V     |

|                                              | VIN = 3.6 V, not switching                                       |      | 625  | 900  | μΑ    |

| VIN supply current (constant frequency mode) | VIN = 7.2 V, not switching                                       |      | 650  | 915  | μΑ    |

| (constant nequency mode)                     | VIN = 9.0 V, not switching                                       |      | 700  | 925  | μΑ    |

| VIN supply current                           | VIN = 3.6 V, not switching                                       |      | 220  | 295  | μΑ    |

| (burst mode)                                 | VIN = 7.2 V, not switching                                       |      | 250  | 370  | μΑ    |

| VIN supply current                           | VIN = 3.6 V                                                      |      | 230  | 340  | μΑ    |

| (sleep mode)                                 | VIN = 7.2 V                                                      |      | 190  | 275  | μΑ    |

|                                              | VIN = 7.2 V, SD/SYNC = VIN                                       |      | 1    | 15   | μΑ    |

| VIN shutdown current                         | VIN = 7.2 V, SD/SYNC = 4 V                                       |      | 2    | 25   | μΑ    |

|                                              | VIN = 3.6 V, SD/SYNC = 3.6 V                                     |      | 1    | 15   | μΑ    |

| Error Amplifier Section                      |                                                                  |      |      |      |       |

| FB input voltage                             | COMP = 0.5 V, $T_A = 25^{\circ}C$                                | 790  | 800  | 810  | mV    |

|                                              | $T_A = 25^{\circ}C$ , VIN = 2.8 V to 9 V                         |      |      | 0.1  | %/V   |

| FB voltage line requlation                   | $T_A = 25^{\circ}C$ , VIN = 2.8 V to 2.5 V                       |      |      | 0.5  | %     |

| ED insulvation                               | COMP = 0.5 V, $T_A = 0$ °C to 70°C                               | 784  | 800  | 816  | mV    |

| FB input voltage                             | COMP = 0.5 V, $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ | 777  | 800  | 823  | mV    |

| FB input bias current                        | COMP = 0.5 V                                                     |      | 100  | 500  | nA    |

| Open loop gain                               | COMP = 0.2 V to 0.5 V                                            | 50   | 80   | 130  | dB    |

| Unity gain BW                                | See Note 1                                                       |      | 5    |      | MHz   |

| Maximum sinking current                      |                                                                  | 250  | 500  |      | μΑ    |

| Maximum sourcing current                     |                                                                  |      | -500 | -250 | μΑ    |

| COMP output high voltage                     | I <sub>COMP</sub> = -10 μA                                       | 1.60 | 2.00 | 2.75 | V     |

| COMP output low voltage                      | I <sub>COMP</sub> = 10 μA                                        |      | 250  | 500  | mV    |

| Soft-start time                              |                                                                  | 1    | 5    | 9    | ms    |

| Light Load Detectors Section                 |                                                                  |      |      |      |       |

| FB VOFF threshold                            |                                                                  | 778  | 808  | 838  | mV    |

| FB V <sub>ON</sub> threshold                 |                                                                  | 741  | 778  | 815  | mV    |

| FB V <sub>MODE</sub> threshold               |                                                                  | 725  | 762  | 799  | mV    |

NOTE 1: Ensured by design. Not production tested.

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

electrical characteristics over recommended operating free-air temperature range,  $T_A = -40$  C to 85 C,  $T_A = T_J$ , typical values are at  $T_A = 25$  C,  $V_{IN} = 7.2$  V, MODE = 1 (constant frequency), SD/SYNC = 0 V. (unless otherwise noted)

| PARAMETER                              | TEST CONDITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|---------------------------------------------------------|------|------|------|-------|

| Pulse Width Modulator Section          |                                                         |      |      |      |       |

|                                        | TPS62100, 300 kHz version, VIN = 5 V                    | 225  | 300  | 375  | kHz   |

| CIM avritable a fraguesa               | TPS62101, 600 kHz version, VIN = 5 V                    | 450  | 600  | 750  | kHz   |

| SW switching frequency                 | TPS62102, 1 MHz version, VIN = 5 V                      | 0.75 | 1    | 1.25 | MHz   |

|                                        | TPS62103, 2 MHz version, VIN = 5 V                      | 1.5  | 2    | 2.5  | MHz   |

|                                        | TPS62100, 300 kHz version, VIN = 5 V, See Notes 1 and 2 |      |      | 490  | kHz   |

| Maximum ayna fraguanay                 | TPS62101, 600 kHz version, VIN = 5 V, See Notes 1 and 2 |      |      | 966  | kHz   |

| Maximum sync. frequency                | TPS62102, 1 MHz version, VIN = 5 V, See Notes 1 and 2   |      |      | 1.61 | MHz   |

|                                        | TPS62103, 2 MHz version, VIN = 5 V, See Notes 1 and 2   |      |      | 2.5  | MHz   |

| Maximum duty cycle                     | COMP = 2.5 V                                            |      |      | 100% |       |

| Minimum duty cycle                     | COMP = 0 V                                              | 0%   |      |      |       |

| Output Switch Section                  |                                                         |      |      |      |       |

| SW NFET R <sub>DS(on)</sub>            | $I_{SW} = 500 \text{ mA}$ $VIN = 7.2 \text{ V}$         |      | 0.3  | 0.6  | Ω     |

| SW PFET R <sub>DS(on)</sub>            | $I_{SW} = -500 \text{ mA}$ VIN = 7.2 V                  |      | 0.5  | 1    | Ω     |

| SW NFET R <sub>DS(on)</sub>            | $I_{SW} = 500 \text{ mA}$ VIN = 3.6 V                   |      | 0.6  | 1.2  | Ω     |

| SW PFET R <sub>DS(on)</sub>            | $I_{SW} = -500 \text{ mA}$ VIN = 3.6 V                  |      | 0.8  | 1.6  | Ω     |

| SW output leakage                      | SW = 4.5V VIN = 9 V                                     | -10  | 0    | 10   | μΑ    |

| SW charge switch current limit 1       | Terminates pulse                                        | 0.65 | 0.95 | 1.25 | Α     |

| SW charge switch current limit 2       | Initiates soft-start, See Note 1                        | 0.75 | 1.15 | 1.55 | Α     |

| SW current, light-load mode            | Peak inductor current                                   | 112  | 160  | 208  | mA    |

| Shutdown and Synchronization Section   | on                                                      |      |      |      |       |

| SD/SYNC threshold                      |                                                         | 0.5  | 1    | 2.3  | V     |

| SD/SYNC input current                  | SD/SYNC = 0 V                                           | -100 | 0    | 100  | nA    |

| SD/SYNC input current                  | SD/SYNC = 7.2 V                                         | -1   | 0    | 1    | μΑ    |

| Maximum synchronization pulse width    |                                                         |      | 25   | 37   | μs    |

| Minimum synchronization pulse width    |                                                         | 50   |      |      | ns    |

| Three-State Mode Control Input Section | on                                                      |      |      |      |       |

| Light-load MODE threshold              |                                                         | 225  | 300  | 410  | mV    |

| Constant frequency MODE threshold      |                                                         | 475  | 600  | 750  | mV    |

| Open circuit MODE voltage              |                                                         | 375  | 450  | 510  | mV    |

| MODE input-low current                 | Mode = 0 V                                              | -20  | -12  | -5   | μΑ    |

| MODE input-high current                | Mode = 1.4 V                                            | 10   | 22   | 33   | μΑ    |

NOTES: 1. Ensured by design. Not production tested.

<sup>2.</sup> Minimum synchronization frequency must be less than the natural running frequency.

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

#### **APPLICATION INFORMATION**

#### general information

The TPS6210x family of devices are low-power, synchronous buck controllers with integrated FETS. The thrust of these devices is to facilitate the construction of low-cost, small, high-frequency and fast-response dc-to-dc converters that operate from either one or two li-ion cells. Synchronous rectification allows for higher operating efficiency than relying on a Schottky diode alone. Shifting from a fixed-frequency PWM mode of operation to a fixed-current variable frequency mode during light loads preserves efficiency and increases battery life in this situation.

#### modes of operation

The TPS6210x family has four distinct modes of operation: automatic-constant frequency (or high-power mode), automatic-variable frequency (or low-power mode), forced-constant frequency, and forced-variable frequency. The mode that the chip is in is controlled by the MODE pin. Allowing this pin to float lets the chip automatically transition between the high-power mode and the low-power mode. The chip selects which mode to operate in depending upon load current and voltage. If the mode pin is forced high, the chip operates in the forced-constant frequency PWM mode. If the pin is driven low, the chip operates in the forced variable frequency mode. Detailed descriptions of the modes follow.

#### forced constant frequency (MODE = high)

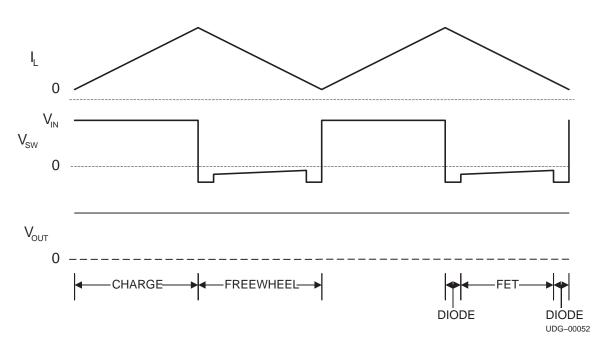

In this mode, the chip behaves like a standard buck regulator with a synchronous rectifier added. The synchronous rectifier turns on shortly after the buck switch turns off, and the buck switch turns on shortly after the synchronous rectifier turns off. During the small time interval when neither the buck switch nor the synchronous rectifier is turned on, an optional small external schottky diode carries the inductor freewheel current.

In this mode, the error amplifier is used in a normal feedback arrangement, forcing the divided output voltage to be equal to the 0.8-V reference. Also, note that the overall converter should be designed so that it always operates in the continuous conduction region, (i.e. the inductor current should never be allowed to decay to zero). If the inductor current decays to zero, the control loop characteristics change dramatically. Consequently, the loop must be designed for the worst case load condition and is not optimal in the general sense for a continuous mode converter.

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

#### APPLICATION INFORMATION

#### forced variable frequency (MODE = low)

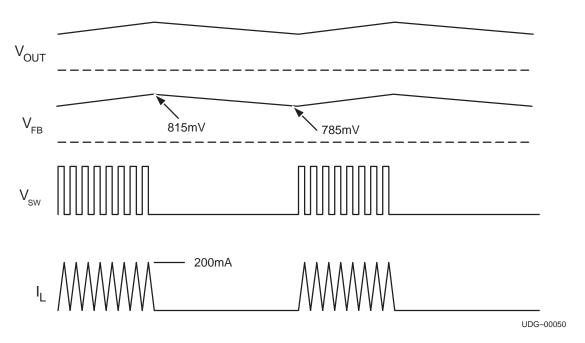

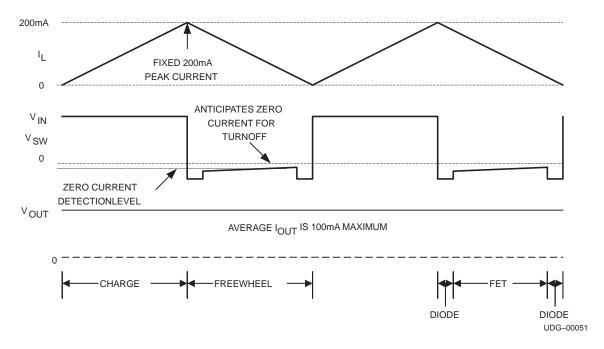

In this mode, the chip behaves like a 100-mA current source that is turned on and off as the output voltage falls below or rises above predetermined thresholds. These thresholds are located approximately 1.9% above and below the nominal output voltage. For instance, if the nominal output is 3.3 V, then the on and off thresholds are approximately 3.237 V and 3.363 V, respectively. The operational sequence is as follows:

- 1. As the output voltage falls below the turn-on threshold, the chip enters a burst period, and the buck switch is turned on.

- 2. When the current in the buck switch rises to 200 mA, the switch is turned off and the synchronous rectifier is turned on to pass the freewheel current.

- 3. As the current in the synchronous rectifier decays to zero, it is turned off and the buck switch is again turned on, continuing at step 2.

- 4. When the output voltage rises above the turn-off threshold, the buck switch is immediately turned off and the synchronous rectifier is turned on to handle the last cycle of free wheel current. The chip is also taken out of its burst period and remains dormant until the output voltage falls below the turn-on threshold, at which point operation continues at step 1.

The reason for limiting the current to 200 mA is to place a limit on the amount of overshoot that can occur from charging the inductor up with a large current and having a relatively small output capacitance available to absorb the energy stored.

In this mode, the error amplifier is not used and is essentially turned off, and its output is disconnected from the COMP pin. The FB pin is connected to two comparators, which generate the internal signals that put the chip into and out of a burst interval. The threshold levels, referenced to the FB pin, are 0.815 V and 0.785 V (off and on). Also, the largest load current that can be supplied by the converter operating in this mode is 100 mA. Sustained load currents greater than 100 mA deplete the energy in the output storage capacitor and cause the output voltage to fall.

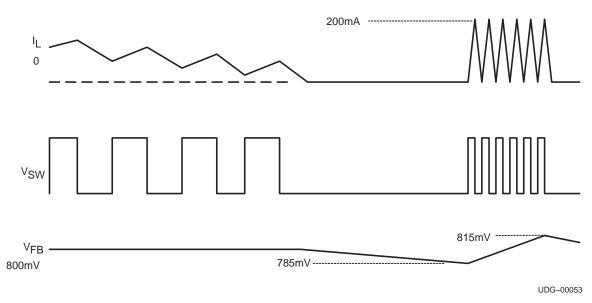

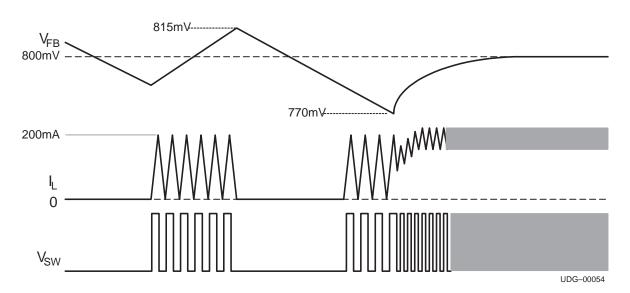

#### the automatic modes, or the high power and low power modes (MODE = floating)

Leaving the MODE pin unconnected or floating lets the chip automatically select one of two operating modes. In these two modes, operation is the same as for the forced modes with the exception that the chip is free to switch between the constant- and variable-frequency modes based upon the operating conditions of the converter. When the chip is initially powered, it is in the constant frequency (high-power) mode, and stays in this mode until it senses that the converter is on the verge of breaking into discontinuous operation. When this condition is sensed, the converter enters the variable-frequency mode of operation. The chip remains in the variable-frequency mode of operation until the voltage at the FB pin falls to approximately 0.770 V or 3.75% below nominal. When this happens, the chip enters the constant-frequency mode of operation and remains in that mode until it senses the converter is about to go discontinuous.

This has some design implications. In order for the transition to occur smoothly, the discontinuous current level of the converter must be less than 100 mA. This in turn implies a minimum inductor size for a given set of operating conditions. The minimum inductor size for smooth transitions is approximately:

$$L = \frac{V_O \left(1 - \frac{V_O}{V_I}\right)}{0.16 \times F} \tag{1}$$

#### Where:

- V<sub>O</sub> is the output voltage

- V<sub>I</sub> is the input voltage and

- F is the frequency of operation

- 0.16 is the minimum peak-inductor-current in low-power mode

It is recommended that something more than the minimum inductance be used to give a little hysteresis to the mode transition. A 10% increase in inductance over the minimum value should be sufficient.

Note that in **all modes**, on initial power-up, after a shutdown, and when there is a second stage overcurrent, the chip transitions into a constant frequency mode of operation and goes through a soft-start cycle. The chip remains in the constant frequency mode until the voltage presented to the FB pin exceeds 0.770 V. At this point the chip may go into a variable frequency mode if MODE is held low, or the load is insufficient to cause continuous inductor current and the MODE pin is left floating.

#### soft start

The TPS6210x family has a built in soft-start time of approximately 5 ms. The soft start is a *closed-loop* soft start, meaning that the reference input to the error amplifier is ramped up over the soft start interval and the converter control loop is allowed to track the ramping reference signal. This method generally allows for faster soft-start times with minimal output voltage overshoot at startup.

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

#### APPLICATION INFORMATION

#### shutdown and synchronization

The TPS6210x family incorporates a dual function shutdown and synchronization pin. Pulsing the SD/SYNC pin higher than 1 V forces the internal oscillator to reset, allowing synchronization to an external signal source. It is recommended that the part not be synchronized higher than two times its nominal operating frequency. The reason for this is that synchronizing to a higher frequency causes the internal saw-tooth voltage to have less amplitude. Since this is the signal that is compared to the error-amplifier output to determine the duty cycle, the reduction in amplitude causes a corresponding increase in PWM gain as well as increased susceptibility to noise. Doubling the operating frequency through synchronization effectively cuts the saw-tooth amplitude in half, doubling the PWM gain.

Bringing the SD/SYNC pin high and holding it for more than 20 µs forces the chip to enter a shutdown state. This causes almost all sections of the chip to enter a dormant state to conserve power. Bringing this pin low again allows the chip to resume operation, starting with a full soft-start cycle.

This pin **must not** be allowed to float, since there are no internal pulldown resistors. Floating this pin could cause the device to operate erratically.

#### error amplifier

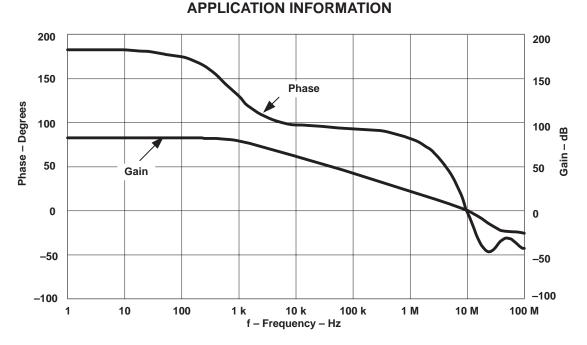

The internal error amplifier has a unity gain frequency of 3 MHz (typ). When designing a compensation network for this chip, the response of the error amplifier may be a limiting consideration. This is especially true with the 1-MHz and 2-MHz switching frequencies. The phase and gain characteristics of the error amplifier are shown in Figure 1.

Due to the method of sensing voltage thresholds in the variable-frequency mode, it is recommended that the compensation loop use integral compensation (no dc path from the COMP pin to the FB pin) if the chip is allowed to automatically switch between constant- and variable-frequency modes of operation. The reason for this is to avoid dc offsets creeping into the sense point and changing the nominal output voltage in the variable-frequency mode.

Figure 1. Error Amplifier Gain Phase Response

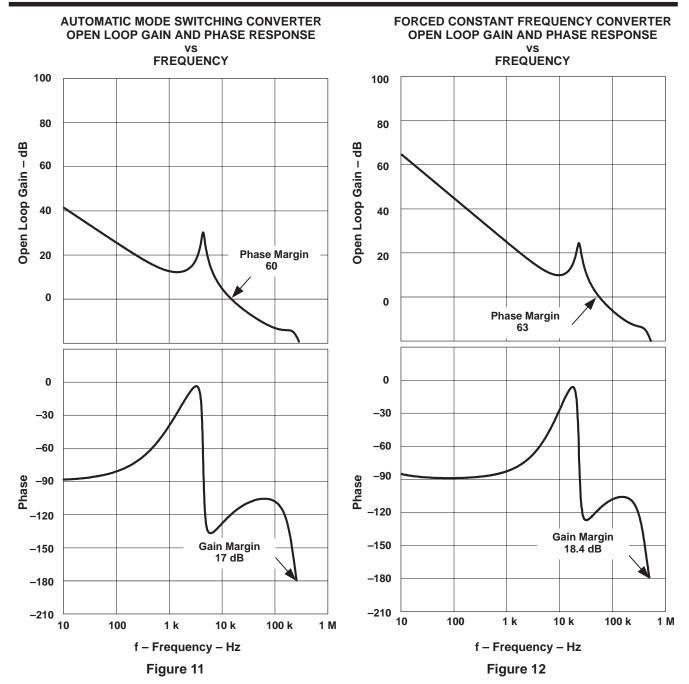

#### loop compensation and the TPS6210X series of converters

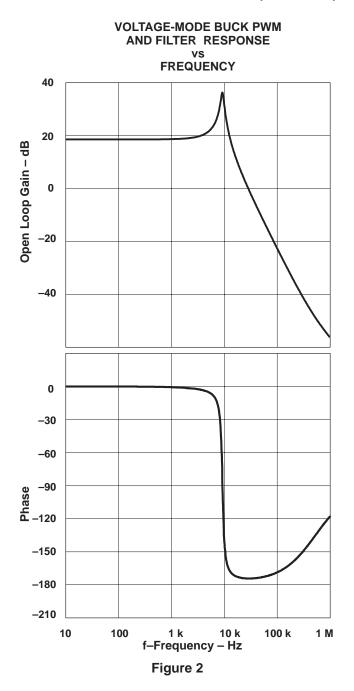

Feedback-loop compensation in the data sheet examples assumes that the output-filter capacitor is a mulit-layer ceramic (MLC) type. With this type of output capacitor, the ESR zero will be too high in frequency to use as part of the compensation network. This can complicate the loop compensation, especially in the higher-switching frequency versions where error-amplifier bandwidth must be taken into consideration. A typical PWM- and output-filter response plot is shown in Figure 2. Note the lightly-loaded circuit has a pair of complex poles that cause the gain peaking and rapid-phase shift near the L-C resonant frequency.

The strategy that has been the best to date for designing a compensator for this circuit has been to use:

- an origin pole (no dc path from COMP to FB),

- a zero placed below the L-C resonance,

- a zero placed above the L-C resonance,

- and the remaining pole placed above the last zero.

loop compensation and the TPS6210X series of converters (continued)

#### loop compensation and the TPS6210X series of converters (continued)

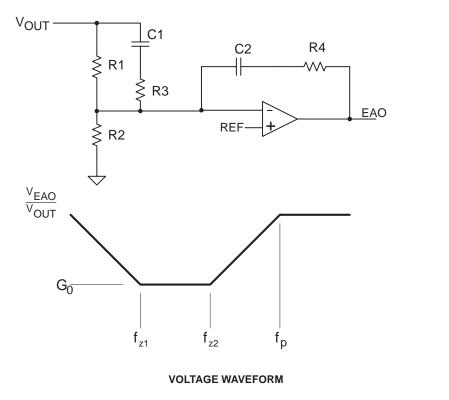

The circuit shown in Figure 3, implements an origin pole, two zeros and a high frequency pole. A second high frequency pole will be added by the response of the error amplifier. If desired, this additional pole can be controlled by adding a capacitor across the series R–C from COMP to FB.

Figure 3. Compensation Network and Gain Response

In this schematic and line approximation of response, the components are calculated as follows:

$$R_1 = R_2 \times \left(\frac{V_{OUT} - V_{REF}}{V_{REF}}\right)$$

(2)

UDG-00131

$$R_4 = R_1 \| R_2 \times G_0 \tag{3}$$

$$C_2 = \left(2 \times \pi \times f_{z1} \times R_4\right)^{-1} \tag{4}$$

$$C_1 = \left(2 \times \pi \times f_{z2} \times R_1 \| R_2\right)^{-1}$$

(5)

$$R_3 = \left(2 \times \pi \times f_p \times C_1\right)^{-1} \tag{6}$$

#### loop compensation and the TPS6210X series of converters (continued)

Note that  $f_{z1}$  is a lower frequency than  $f_{z2}$ . It is suggested that a spice or other simulator be used to verify feedback loop characteristics. When doing this modeling, be sure to use an amplifier that has a band limited response. Setting the amplifier up for an 80 dB gain with a single dominant pole at 200 Hz (2 MHz GBWP) will lead to a good loop design. The gain/phase plots for the example circuits were all done using a 2 MHz GBWP amplifier. Look at the example schematics and note where the poles and zeros are for an indication of where to start compensating a new design.

#### current limiting

The TPS6210x family has built-in over-current protection and thermal shutdown. The over-current protection is done in two stages. The first stage trips at approximately 1 A and simply causes an immediate pulse termination. If a hard short is present at the output of the LC filter, propagation delays from the first-level over current could allow the current to ratchet up in the inductor. To prevent this from happening, a second level of over-current protection trips at approximately 1.2 A. When this level is tripped, the chip is forced to do a soft start. If the chip is in an abnormally high ambient temperature, or has an inadequate heatsink for the power levels demanded, the thermal shutdown circuitry causes the chip to shut down if the die temperature ever reaches 170°C. After the die cools, normal operation resumes with a full soft start.

Figure 4. Typical Pulsed-Variable-Frequency Mode (PFM) Circuit Waveform

Figure 5. Typical Constant-Frequency Mode Circuit Waveforms

Figure 6. PFM Circuit Waveforms (Expanded View)

NOTE A: Time scale not constant for CF and PFM modes.

Figure 7. Constant Frequency To PFM Transition

Figure 8. PFM to Constant Frequency Transition

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

#### **APPLICATION INFORMATION**

#### design example: automatic-mode switching converter, two li-ion cell input, 3.0-V output

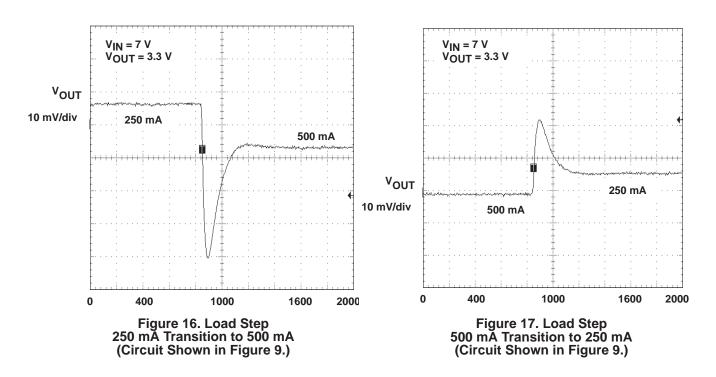

Figure 9 shows the schematic of an automatic-mode switching converter based upon the TPS62102. The output current for this design can range from 0 mA to 500 mA.

Figure 9. Automatic-Mode Switching Converter Application Circuit

† Optional

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

#### **APPLICATION INFORMATION**

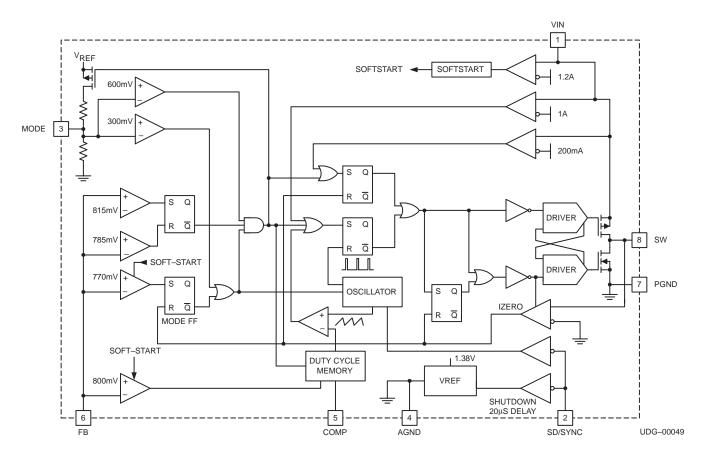

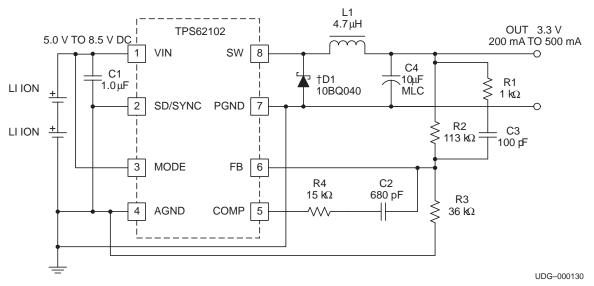

design example: forced constant-frequency mode switching converter, two li-ion cell input, 3.0-V output

Figure 10 shows the schematic of a forced constant-frequency mode switching converter based upon the TPS62102. The output current for this design can range from 200 mA to 500 mA.

† Optional

Figure 10. Forced Constant-Frequency Mode Application Circuit

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

SLUS446B - MAY 2000 - REVISED DECEMBER 2000

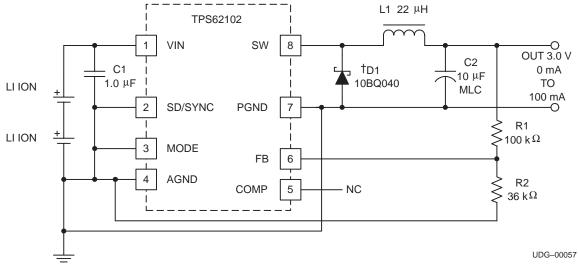

# design example: forced variable-frequency mode switching converter, two li-ion cell input, 3.0-V output

Figure 13 shows the schematic of a forced variable-frequency mode switching converter based upon the TPS62102. The output current for this design can range from 0 mA to 100 mA.

† Optional

Figure 13. Forced Variable-Frequency Mode Application Circuit

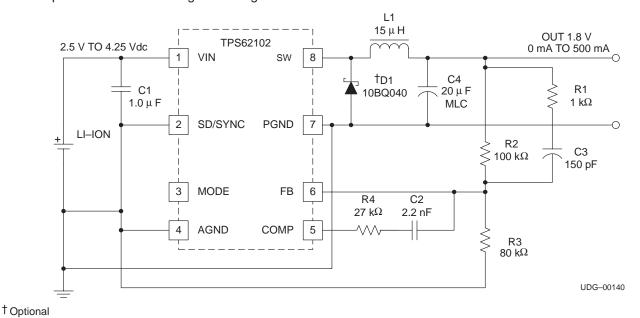

#### design example: automatic mode switching converter, single li-ion cell input, 1.8-V output

Figure 14 shows the schematic of an automatic-mode switching converter based upon the TPS62102. The output current for this design can range from 0 mA to 500 mA.

Figure 14. 1.8-V Output Automatic-Mode Switching Converter Application Circuit

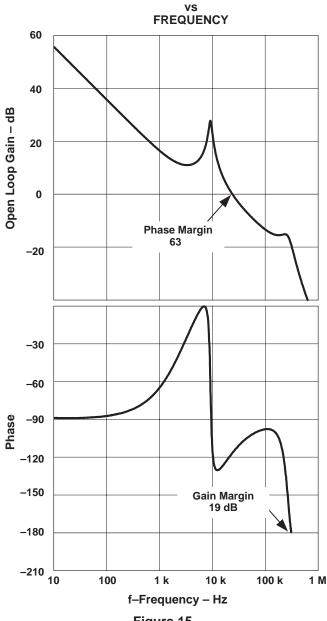

#### 1.8-V OUTPUT SWITCHING CONVERTER **OPEN LOOP GAIN AND PHASE RESPONSE**

Figure 15

#### PARAMETER MEASUREMENT INFORMATION

#### **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

#### PACKAGE OPTION ADDENDUM

com 13-Nov-2008

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TPS62100D        | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62100DG4      | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62100DR       | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62100DRG4     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62101D        | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62101DG4      | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62101DR       | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62101DRG4     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62102D        | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62102DG4      | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62102DR       | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62102DRG4     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62103D        | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS62103DG4      | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is

#### PACKAGE OPTION ADDENDUM

13-Nov-2008

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

9-Aug-2008

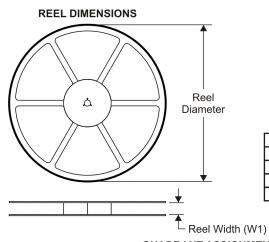

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

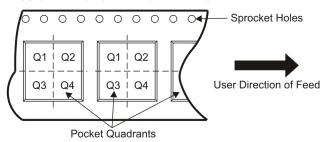

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device     | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

|   | TPS62100DR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

| I | TPS62101DR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

| I | TPS62102DR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

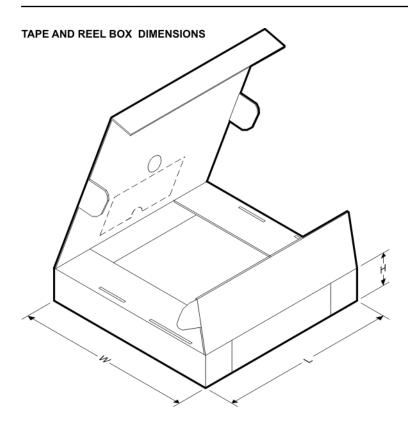

## PACKAGE MATERIALS INFORMATION

\*All dimensions are nominal

| 7 till difficilities die fremman |              |                 |      |      |             |            |             |

|----------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS62100DR                       | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| TPS62101DR                       | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| TPS62102DR                       | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mamt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| www.ti.com/audio          |

|---------------------------|

| www.ti.com/automotive     |

| www.ti.com/broadband      |

| www.ti.com/digitalcontrol |

| www.ti.com/medical        |

| www.ti.com/military       |

| www.ti.com/opticalnetwork |

| www.ti.com/security       |

| www.ti.com/telephony      |

| www.ti.com/video          |

| www.ti.com/wireless       |

|                           |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated