# BUCK CURRENT/VOLTAGE FED PUSH-PULL PWM CONTROLLERS

#### **FEATURES**

- Ideal for Multiple Output and/or High Voltage Output Voltage Converters

- Up to 500 kHz Operation

- High Voltage, High Current Floating Driver for Buck Converter Stage

- UC3827-1 Current Fed Controller has Push-Pull Drivers with Overlapping Conduction Periods

- UC3827-2 Voltage Fed Controller has Push-Pull Drivers with Nonoverlapping Conduction Periods

- Average Current Mode, Peak Current Mode or Voltage Mode with Input Voltage Feedforward Control for Buck Power Stage

- Wide Bandwidth, Low Offset,

Differential Current Sense Amplifier

- Precise Short Circuit Current Control

#### DESCRIPTION

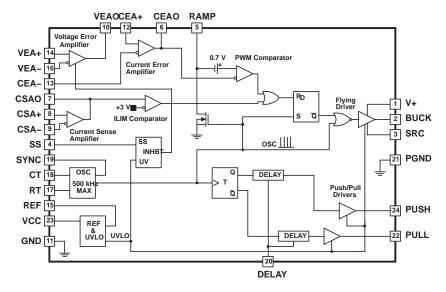

The UC3827 family of controller devices provides an integrated control solution for cascaded buck and push-pull converters. These converters are known as current fed or voltage fed push-pull converters and are ideally suited for multiple output and/or high voltage output applications. In both current fed and voltage fed modes, the push-pull switches are driven at 50% nominal duty cycles and at one half the switching frequency of the buck stage. In the current fed mode, the two switches are driven with a specified over-lap period to prevent ringing and voltage stress on the devices. In the voltage fed mode, the two switches are driven with a specified gap time between the switches to prevent shorting the transformer across the energy storage capacitor and to prohibit excessive currents flowing through the devices.

The converter's output voltage is regulated by pulse width modulation of the buck switch. The UC3827 contains complete protection and PWM control functions for the buck converter. Easy control of the floating switch is accomplished by the floating drive circuitry. The gate drive waveform is level shifted to support an input voltage up to  $72\ V_{DC}$ .

#### **BLOCK DIAGRAM**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### **DESCRIPTION (CONTINUED)**

The UC3827 can be set up in traditional voltage mode control using input voltage feedforward technique or in current mode control. Using current mode control prevents potential core saturation of the push-pull transformer due to mismatches in timing and in component tolerances. With average current mode control, precise control of the inductor current feeding the push-pull stage is possible without the noise sensitivity associated with peak current mode control. The UC3827 average current mode loop can also be connected in parallel with the voltage regulation loop to assist only in fault conditions.

Other valuable features of the UC3827 include bidirectional synchronization capability, user programmable overlap time (UC3827-1), user programmable gap time (UC3827-2), a high bandwidth differential current sense amplifier, and soft start circuitry.

#### ORDERING INFORMATION(1)

| т _т        | PUSH-PULL TOPOLOGY | PACKAGES   |           |           |  |  |  |  |

|-------------|--------------------|------------|-----------|-----------|--|--|--|--|

| $T_A = T_J$ | POSH-PULL TOPOLOGY | SOIC-24    | PDIP-24   | PLCC-28   |  |  |  |  |

| -40C to 85C | Current Fed        | UC2827DW-1 | UC2827N-1 | -         |  |  |  |  |

| -400 10 650 | Voltage Fed        | UC2827DW-2 | UC2827N-2 | -         |  |  |  |  |

| 0C to 70C   | Current Fed        | UC3827DW-1 | UC3827N-1 | UC3827Q-1 |  |  |  |  |

| 00 10 700   | Voltage Fed        | UC3827DW-2 | UC3827N-2 | -         |  |  |  |  |

<sup>(1)</sup> The DW and Q packages are also available taped and reeled. Add a TR suffix to the device type (i.e., UC2827DWTR-1).

#### **DISSIPATION RATINGS**

| PACKAGE       | (θ <sub>JA</sub> ) JUNCTION-TO-AMBIENT<br>TEMPERATURE (C/W) | (θ <sub>JC</sub> ) JUNCTION-TO-WHAT?<br>TEMPERATURE (C/W) |

|---------------|-------------------------------------------------------------|-----------------------------------------------------------|

| 24-pin (N)    | 60 <sup>(1)</sup>                                           | 30                                                        |

| 24-pin (J)    | 70 to 90                                                    | 28 <sup>(2)</sup>                                         |

| 28-pin (DW)   | 71 to 83 <sup>(3)</sup>                                     | 24 <sup>(3)</sup>                                         |

| 28-pin (QLCC) | 40-65 <sup>(1)</sup>                                        | 30                                                        |

- (1) Specified θ<sub>JA</sub> (junction-to-ambient) refers to devices mounted to 5-in<sup>2</sup> FR4 PC board with 1 oz. copper where noted. When a resistance range is given, the lower values refer to a 5-in<sup>2</sup> aluminum PC board. The test PWB is 0.062 inches thick and typically used 0.635 mm trace widths for power packages and 1.3 mm trace widths for non-power packages with a 100 1100 mil probe land area at the end of each trace.

- (2) Specified θ<sub>JC</sub> (junction-to-what?) data values stated were derived from MIL-STD-1835B which states "The baseline values shown are worst case (mean + 2s) for a 60 x 60 mil microcircuit device silicon die and applicable for devices with die sizes up to 14400 mils². For device sizes greater than 14400 mils² use the following values; dual-in-line, 11 C/W; flat pack, 10 C/W; pin grid array, 10 C/W pin grid array, 10 C/W."

- (3) Modeled data. If there is a value range given for θ<sub>JA</sub>, the lower value refers to a 3 x 3 in., 1-oz, internal copper ground plane. The higher value refers to a 1 x 1 in. ground plane. All model data assumes only one trace for each non-fused lead.

#### ABSOLUTE MAXIMUM RATINGS(1)

|                        |                                                                                            | UC2827-1<br>UC2827-2<br>UC3827-1<br>UC3827-2 | UNITS |

|------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------|-------|

| Supply voltage, VCC    |                                                                                            | 20                                           |       |

|                        | CEAO, CEA+, CEA-, CSAO, CSA+, CSA-, CT, DELAY, PUSH, PULL, RAMP, RT, SS, SYNC, VEA+, VEAO, | -0.3 to 5                                    | V     |

| Input voltage range    | V+ and BUCK                                                                                | 90                                           |       |

|                        | SRC                                                                                        | 90-VCC                                       |       |

| DLICK data a           | I/O continuous                                                                             | 250                                          | mA    |

| BUCK driver            | I/O peak                                                                                   | 1                                            | Α     |

| DUCU/DUU drivor        | I/O continuous                                                                             | 200                                          | mA    |

| PUSH/PULL driver       | I/O peak                                                                                   | 0.8                                          | А     |

| Storage temperature    |                                                                                            | -65 to 150                                   |       |

| Junction temperature   |                                                                                            | -55 to 150                                   | С     |

| Lead temperature (sold | ering, 10 sec)                                                                             | 300                                          |       |

<sup>(1)</sup> Voltages are referenced to ground. Currents are positive into, negative out of the specified terminal. Consult *Packaging* section of databook for thermal limitations and considerations of packages.

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise spsecified,  $V_{VCC}$  = 15 V,  $V_{V+}$  = 14.3 V,  $C_{CT}$  = 340 pF,  $R_{RT}$  = 10 k $\Omega$ ,  $R_{DELAY}$  = 24.3 k $\Omega$ ,  $V_{SRC}$  =  $V_{GND}$  =  $V_{BUCK}$  =  $V_{PUSH}$  =  $V_{PULL}$  outputs no load,  $T_J$  =  $T_A$

|                    | PARAMETER                        | TEST CONDITIONS                   | MIN  | TYP  | MAX  | UNIT |

|--------------------|----------------------------------|-----------------------------------|------|------|------|------|

| SUPPLY             |                                  |                                   |      |      |      |      |

|                    | VCC UVLO, Turn-on                |                                   | 8.3  | 8.8  | 9.5  | V    |

|                    | Hysteresis                       |                                   | 0.9  | 1.2  | 1.5  | V    |

| I <sub>VCC</sub>   | Supply current start             | V <sub>VCC</sub> = 8 V            |      |      | 1000 | Α    |

| I <sub>VCC</sub>   | Supply current run               |                                   |      | 32   | 45   | mA   |

|                    | I <sub>V+</sub> buck high        |                                   | 0.2  | 1    | 2    | mA   |

| VOLTAGE            | ERROR AMPLIFIER                  |                                   |      | •    |      |      |

| IB                 |                                  |                                   |      | 0.5  | 3    | Α    |

| VIO                |                                  |                                   |      |      | 10   | mV   |

| AVOL               |                                  |                                   | 80   | 95   |      | dB   |

| GBW <sup>(1)</sup> | Gain bandwidth                   |                                   | 1    | 4    |      | MHz  |

| V <sub>OL</sub>    | Low-level output voltage         | I <sub>VEAO</sub> = 0 A (No load) |      | 0.3  | 0.5  | V    |

| V <sub>OH</sub>    | High-level output voltage        | I <sub>VEAO</sub> = 0 A (No load) | 2.85 | 3    | 3.20 | V    |

| CURRENT            | SENSE AMPLIFIER                  |                                   |      | •    |      |      |

| IB                 |                                  |                                   |      | -1   | -5   | Α    |

| VIO                |                                  |                                   |      |      | 5    | mV   |

| AVOL               |                                  |                                   | 80   | 110  |      | dB   |

| GBW (1)            | Gain bandwidth                   |                                   | 15   | 29   |      | MHz  |

| V <sub>OL</sub>    | Low-level output voltage         | I <sub>CEAO</sub> = 0 A (No load) |      | 0.25 | 0.5  | V    |

| V <sub>OH</sub>    | High-level output voltage        | I <sub>CEAO</sub> = 0 A (No load) | 3    | 3.3  |      | V    |

| CMRR               | Common mode range <sup>(1)</sup> |                                   | -0.3 |      | 2    | V    |

| CURRENT            | ERROR AMPLIFIER                  |                                   |      |      | ,    |      |

| IB                 |                                  |                                   |      | -1   | -5   | Α    |

| VIO                |                                  |                                   |      |      | 10   | mV   |

| AVOL               |                                  |                                   | 80   | 110  |      | dB   |

(1) Ensured by design. Not production tested.

#### **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise spsecified,  $V_{VCC}$  = 15 V,  $V_{V+}$  = 14.3 V,  $C_{CT}$  = 340 pF,  $R_{RT}$  = 10 k $\Omega$ ,  $R_{DELAY}$  = 24.3 k $\Omega$ ,  $V_{SRC}$  =  $V_{GND}$  =  $V_{BUCK}$  =  $V_{PUSH}$  =  $V_{PULL}$  outputs no load,  $T_J$  =  $T_A$

|                                           | PARAMETER                            |          | TEST CONDITIONS                                                | MIN        | TYP  | MAX | UNIT |

|-------------------------------------------|--------------------------------------|----------|----------------------------------------------------------------|------------|------|-----|------|

| GBW <sup>(1)</sup>                        | Gain bandwidth                       |          | At 100 kHz, Measure Gain                                       | 2          | 4.5  |     | MHz  |

| V <sub>OL</sub>                           |                                      |          | I <sub>CEAO</sub> = 0 A (No Load)                              |            | 0.25 | 0.5 | V    |

| V <sub>OH</sub>                           |                                      |          | I <sub>CEAO</sub> = 0 A (No Load)                              | 3.3        | 3.5  |     | V    |

| CMRR                                      | Common mode range <sup>(1)</sup>     |          |                                                                | -0.3       |      | 5   | V    |

| OSCILLAT                                  | OR SECTION                           |          |                                                                |            |      |     |      |

| fosc                                      | Frequency                            |          |                                                                | 180        | 220  | 250 | kHz  |

| I <sub>CT(dsch)</sub>                     | CT discharge current                 |          | 3.5V at CT when CT removed                                     | 5          |      |     | mA   |

| PWM COM                                   | <b>IPARATOR</b>                      |          |                                                                |            |      |     |      |

| D <sub>MAX</sub>                          | Minimum duty cycle                   |          | 200 kHz                                                        |            |      | 0%  |      |

| D <sub>MAX</sub>                          | Maximum duty cycle                   |          | 200 kHz                                                        | 85%        | 91%  | 95% |      |

| BUCK OU                                   | TPUT STAGE                           |          |                                                                |            |      |     |      |

| t <sub>RISE</sub>                         | Rise time                            |          | 1 nF Load <sup>(2)</sup>                                       |            | 40   | 100 | ns   |

| t <sub>FALL</sub>                         | Fall time                            |          | 1 nF, Load                                                     |            | 30   | 80  | ns   |

| V <sub>OH</sub> High-level output voltage |                                      |          | $I_{BUCK} = -15 \text{ mA}$ , V+ $-BUCK^{(3)}$                 |            | 1.5  | 2.5 | V    |

| V <sub>OH</sub>                           | High-level output voltage            |          | IBUCK = $-150$ mA, V+ $-BUCK$ <sup>(3)</sup>                   |            | 2    | 2.5 | V    |

| \/                                        | Low-level output voltage             |          | I <sub>BUCK</sub> = 15 mA <sup>(4)</sup>                       |            | 0.2  | 0.4 | V    |

| $V_{OL}$                                  | Low-level output voltage             |          | I <sub>BUC</sub> K = 150 mA <sup>(4)</sup>                     |            | 0.7  | 1.2 | V    |

| PUSH/PUL                                  | L OUTPUT STAGES                      |          |                                                                |            |      |     |      |

| t <sub>RISE</sub>                         | Rise time                            |          | 1 nF load                                                      |            | 50   | 100 | ns   |

| t <sub>FALL</sub>                         | Fall time                            |          | 1 nF load                                                      |            | 35   | 100 | ns   |

|                                           | Overlap time                         | UCx827-1 | 1 nF loads <sup>(5)</sup>                                      | 100        | 250  | 400 | ns   |

|                                           | Nonoverlapping time (6)              | UCx827-2 |                                                                | 100        | 250  | 500 | ns   |

|                                           | Library and a second configurations. |          | I <sub>PUSH/PULL</sub> = -10 mA, VCC - PUSH                    |            | 2    | 3   | V    |

| V <sub>OH</sub>                           | High-level output voltage            |          | I <sub>PUSH/PULL</sub> = -100 mA, VCC -<br>PUSH <sup>(7)</sup> |            | 2.5  | 3   | V    |

| . ,                                       |                                      |          | I <sub>PUSH/PULL</sub> = 10 mA <sup>(7)</sup>                  |            | 0.2  | 0.8 | V    |

| $V_{OL}$                                  | Low-level output voltage             |          | I <sub>PUSH/PULL</sub> = 100 mA <sup>(7)</sup>                 |            | 0.6  | 1.2 | V    |

| REFEREN                                   | CE                                   |          |                                                                | 1          | '    | ,   |      |

|                                           | Reference voltage                    |          |                                                                | 4.8        | 5    | 5.2 | V    |

| I <sub>SC</sub>                           | Shor-circuit current                 |          | V <sub>REF</sub> = 0V                                          | -35        | -50  | -65 | mA   |

|                                           | Line regulation                      |          | 0.5V < V <sub>VCC</sub> < 20 V                                 |            | 5    | 20  | mV   |

|                                           | Load regulation                      |          | 0 mA < I <sub>IO</sub> < 10 mA                                 |            | 8    | 20  | mV   |

| SOFT STA                                  | RT                                   |          |                                                                | 1          |      |     |      |

| V <sub>OL</sub>                           | Low-level output voltage saturation  |          | $V_{VCC} = 7 \text{ V}, I_{SS} = 100 \mu\text{A}$              |            | 1.4  | 2.0 | V    |

| I <sub>SS</sub>                           | Soft-start current                   |          |                                                                | <b>-</b> 5 | -12  | -25 | Α    |

<sup>(2)</sup> Measure the rise time from when BUCK crosses 1 V until it crosses 9 V.

To force BUCK high, force  $V_{CSAO}$ =2.5 V,  $V_{CEAO}$  = 2.5 V, a 25-k $\Omega$  pulldown resistor from RAMP to ground, and  $V_{CT}$  = 0.5 V. To force BUCK low, force  $V_{CSAO}$  = 2.5 V,  $V_{CEAO}$  = 2.5 V, a 10-k $\Omega$  pulldown resistor from RAMP to ground, and  $V_{CT}$  = 3.5 V. The overlap time is measured from the point at which the rising edge of PUSH/PULL crosses 5 V until the falling edge of PULL/PUSH (5) crosses 5V.

The non-overlap time is measured from the point at which the falling edge of PUSH/PULL crosses 5 V until the rising edge of PULL/PUSH crosses 5 V.

<sup>(7)</sup> To toggle PUSH or PULL into a desired state, pulse CT from 0.5 V to 3.5 V. PUSH and PULL toggle on the rising edge of CT.

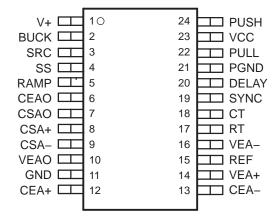

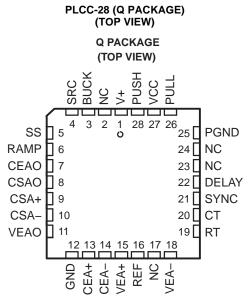

#### **CONNECTION DIAGRAMS**

DIL-24 (N or J, DW PACKAGES) (TOP VIEW)

N, J OR DW PACKAGES (TOP VIEW)

NC - No internal connection

#### **Terminal Functions**

| TE    | ERMINAL    |    | TERMINAL |                                                                                                                                                                                                                                                                                                                                                                                                             | RMINAL |  | ERMINAL |  |  |  |

|-------|------------|----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|---------|--|--|--|

| NAME  | N or<br>DW | Q  | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |        |  |         |  |  |  |

| BUCK  | 2          | 3  | 0        | Output of the buck PWM controller. The BUCK output is a floating driver, optimized for controlling the gate of an N-channel MOSFET. The peak sink and source currents are 1 A. V <sub>CC</sub> undervoltage faults disables BUCK to an off condition (low).                                                                                                                                                 |        |  |         |  |  |  |

| CEA+  | 12         | 13 | ı        | Non-inverting input of the current error amplifier.                                                                                                                                                                                                                                                                                                                                                         |        |  |         |  |  |  |

| CEA-  | 13         | 14 | ı        | Inverting input of the current error amplifier                                                                                                                                                                                                                                                                                                                                                              |        |  |         |  |  |  |

| CEAO  | 6          | 7  | 0        | Output of the current error amplifier and the inverting input of the PWM comparator of the buck converter.                                                                                                                                                                                                                                                                                                  |        |  |         |  |  |  |

| CSA+  | 8          | 9  | ı        | Noninverting input of the current sense amplifier.                                                                                                                                                                                                                                                                                                                                                          |        |  |         |  |  |  |

| CSA-  | 9          | 10 | ı        | Inverting input of the current sense amplifier.                                                                                                                                                                                                                                                                                                                                                             |        |  |         |  |  |  |

| CSAO  | 7          | 8  | 0        | Output of the current sense amplifier and the noninverting input of the current limit comparator. When the signal level on this pin exceeds the 3V threshold of the current limit comparator, the buck gate drive pulse is terminated. This feature is useful to implement cycle-by-cycle current limiting for the buck converter.                                                                          |        |  |         |  |  |  |

| СТ    | 18         | 20 | I        | Provides for the timing capacitor which is connected between CT and GND. The oscillator frequency is set by CT and a resistor RT, connected between pin RT and GND. The CT discharge current is approximately 40 x the bias current through the resistor connected to RT. A practical maximum value for the discharge current is 20 mA. The frequency of the oscillator is given by equation <sup>(1)</sup> |        |  |         |  |  |  |

| DELAY | 20         | 22 | I        | A resistor to GND programs the overlap time of the PUSH and PULL outputs of the UC3827-1 and the dead time of the PUSH and PULL outputs of the UC3827-2. The minimum value of the resistor, $R_{DELAY}$ , is 18 k $\Omega$ . The delay or overlap time is given by equation (2)                                                                                                                             |        |  |         |  |  |  |

| GND   | 11         | 12 | -        | Ground reference for all sensitive setup components not related to driving the outputs. They include all timing, voltage sense, current sense, and bypass components.                                                                                                                                                                                                                                       |        |  |         |  |  |  |

| PGND  | 21         | 25 | -        | Ground connection for the PUSH and PULL outputs. PGND must be connected to GND at a single point on the printed circuit board. This is imperative to prevent large, high frequency switching currents flowing through the ground metalization inside the device.                                                                                                                                            |        |  |         |  |  |  |

| PULL  | 22         | 26 | 0        | Ground referenced output to drive an N-channel MOSFET. The PULL and the PUSH outputs are driving the two switches of the push-pull converter with complementary signals at close to a 50% duty cycle. Any undervoltage faults will disable PULL to an off condition (low).                                                                                                                                  |        |  |         |  |  |  |

$$f_{OSC} = \frac{0.77}{R_{RT} \times C_{CT}} \text{ (Hz)}$$

$$t_{DELAY} = \frac{R_{DELAY}}{200\Omega} \times 10^{-9} \text{ (s)}$$

#### **Terminal Functions (continued)**

| TERMINAL |            |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | N or<br>DW | Q  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PUSH     | 24         | 28 | 0   | Ground referenced output to drive an N-channel MOSFET. The PULL and the PUSH outputs are driving the two switches of the push-pull converter with complementary signals at close to a 50% duty cycle. Any undervoltage faults disables PUSH to an off condition (low).                                                                                                                                                                                                                                                                                                                                              |

| RAMP     | 5          | 6  | I   | The RAMP voltage, after a 700 mV internal level shift, is fed to the noninverting input of the buck PWM comparator. A resistor to $V_{\rm IN}$ and a capacitor to GND provide an input voltage feedforward signal for the buck controller in voltage mode control. In peak current mode control, the RAMP pin receives the current signal of the buck converter. In an average current mode setup, the RAMP pin has a linearly increasing ramp signal. This waveform may be generated either by connecting RAMP directly to CT, or by connecting both a resistor from VCC to RAMP and a capacitor from RAMP to GND. |

| REF      | 15         | 16 | 0   | The output of the +5V on board reference. Bypass this pin with a capacitor to GND. The reference is off when the chip is in undervoltage lockout mode.o                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RT       | 17         | 19 | I   | A resistor to GND programs the charge current of the timing capacitor connected to CT. The charge current approximately equals that shown in equation (3). The charge current should be less than 500 A to keep CT's discharge peak current less than 20 mA, which is CT's maximum practical discharge value. The discharge time, which sets the maximum duty cycle, is set internally and is influenced by the charge current.                                                                                                                                                                                     |

| SRC      | 3          | 4  | I   | The source connection for the floating buck switch. The voltage on the SRC pin can exceed VCC but must be lower than 90 V– $V_{VCC}$ . Also, during turn-off transients of the buck switch, the voltage at SRC can go to $-2V$ .                                                                                                                                                                                                                                                                                                                                                                                    |

| SS       | 4          | 5  | 0   | 5Soft-start pin requires a capacitor to GND. During soft-start the output of the voltage error amplifier is clamped to the soft-start capacitor voltage which is slowly charged by an internal current source. In UVLO, SS is held low.                                                                                                                                                                                                                                                                                                                                                                             |

| SYNC     | 19         | 21 | I   | A bidirectional pin for the oscillator., used to synchronize several chips to the fastest oscillator. Its input synchronization threshold is 1.4 V. The SYNC voltage is 3.6 V when the oscillator capacitor, CT, is discharged. Otherwise it is 0 V. If the recommended synchronization circuit is not used, a 1 k $\Omega$ or lower value resistor from SYNC to GND may be needed to increase the fall time of the signal at SYNC.                                                                                                                                                                                 |

| VCC      | 23         | 27 | ı   | A voltage source connected to this pin supplies the power for the UC3827. It is recommended to bypass this pin to both GND and PGND ground connections with good quality high frequency capacitors                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VEA+     | 14         | 15 | ı   | Non-inverting input of the voltage error amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VEA-     | 16         | 18 | I   | Inverting input of the voltage error amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VEAO     | 10         | 11 | 0   | Output of the voltage error amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V+       | 1          | 1  | I   | Supply voltage for the buck output. The floating driver of the UC3827 uses the bootstrap technique which requires a reservoir capacitor to store the required energy for the on time of the buck switch. A diode must be connected from VCC to V+ to charge the reservoir capacitor. This diode must be able to withstand $V_{\text{IN}}$ . The reservoir capacitor must be connected between V+ and SRC.                                                                                                                                                                                                           |

(3)

$$I_{RT} = \frac{2.5 \text{ V}}{R_{RT}}$$

#### APPLICATION INFORMATION

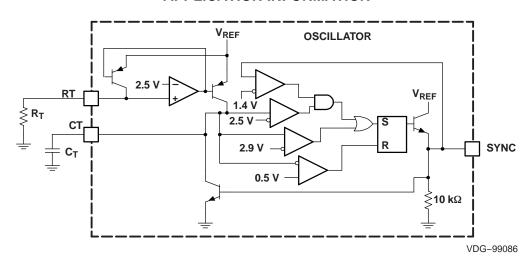

Figure 1. Oscillator Block With External Connections

#### CIRCUIT BLOCK DESCRIPTION

#### **PWM Oscillator**

The oscillator block diagram with external connections is shown in Equation 1. A resistor ( $R_T$ ) connected to pin RT sets the linear charge current:

$$I_{RT} = \frac{2.5 \text{ V}}{R_{RT}} \tag{1}$$

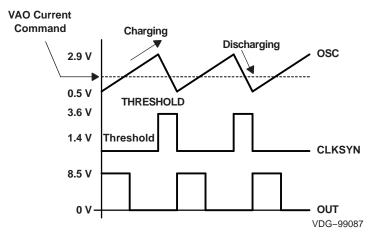

The timing capacitor ( $C_{CT}$ ) is linearly charged with the charge current forcing the OSC pin to charge to a 3.4 V threshold. After exceeding this threshold, the RS flip-flop is set driving CLKSYN high and  $R_{DEAD}$  low which discharges  $C_{CT}$ . CT continues to discharge until it reaches a 0.5 V threshold and resets the RS flip-flop which repeats the charging sequence as shown in Figure 2

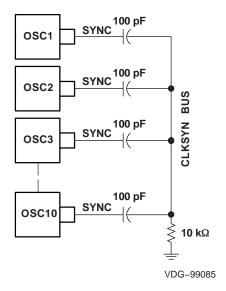

As shown in Figure 3, several oscillators are synchronized to the highest free running frequency by connecting 100 pF capacitors in series with each CLKSYN pin and connecting the other side of the capacitors together forming the CLKSYN bus. The CLKSYN bus is then pulled down to ground with a resistance of approximately 10k. Referring to Figure 1, the synchronization threshold is 1.4 V. The oscillator blanks any synchronization pulse that occurs when OSC is below 2.5 V. This allows units, once they discharge below 2.5 V, to continue through the current discharge and subsequent charge cycles whether or not other units on the CLKSYN bus are still synchronizing. This requires the frequency of all free running oscillators to be within 17% of each other to assure synchronization.

Figure 2. Oscillator and PWM Output Waveform

Figure 3. Oscillator Synchronization Connection Diagram

#### **REVISION HISTORY**

| REVISION | DATE OF CHANGE | DESCRIPTION                                         |

|----------|----------------|-----------------------------------------------------|

| SLUS365A | 8/2005         | Improved CMRR of CSA from (0 - 2 V) to (-0.3 - 2 V) |

| SLUSSOSA | 0/2005         | Improved CMRR of CEA from (0 - 5 V) to (-0.3 - 5 V) |

#### PACKAGE OPTION ADDENDUM

www.ti.com 16-Apr-2009

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| UC2827DW-1       | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC2827DW-1G4     | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC2827DW-2       | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC2827DW-2G4     | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC2827DWTR-1     | ACTIVE                | SOIC            | DW                 | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC2827DWTR-1G4   | ACTIVE                | SOIC            | DW                 | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC2827N-1        | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC2827N-1G4      | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3827DW-1       | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC3827DW-1G4     | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC3827DW-2       | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC3827DW-2G4     | ACTIVE                | SOIC            | DW                 | 24   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| UC3827N-1        | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3827N-1G4      | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3827N-2        | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3827N-2G4      | ACTIVE                | PDIP            | N                  | 24   | 15             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

#### PACKAGE OPTION ADDENDUM

www.ti.com 16-Apr-2009

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC3827-1:

Military: UC1827-1

NOTE: Qualified Version Definitions:

• Military - QML certified for Military and Defense Applications

W.ti.com 5-Feb-2009

#### TAPE AND REEL INFORMATION

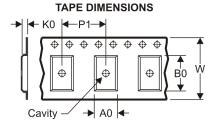

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

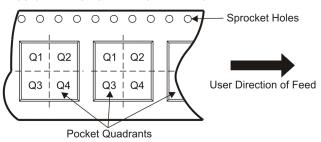

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       |      | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UC2827DWTR-1 | SOIC | DW                 | 24 | 2000 | 330.0                    | 24.4                     | 10.85   | 15.8    | 2.7     | 12.0       | 24.0      | Q1               |

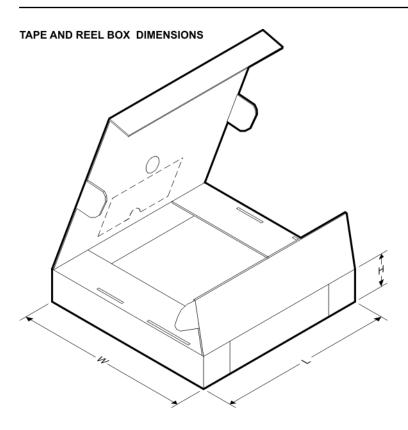

## PACKAGE MATERIALS INFORMATION

5-Feb-2009

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2827DWTR-1 | SOIC         | DW              | 24   | 2000 | 346.0       | 346.0      | 41.0        |

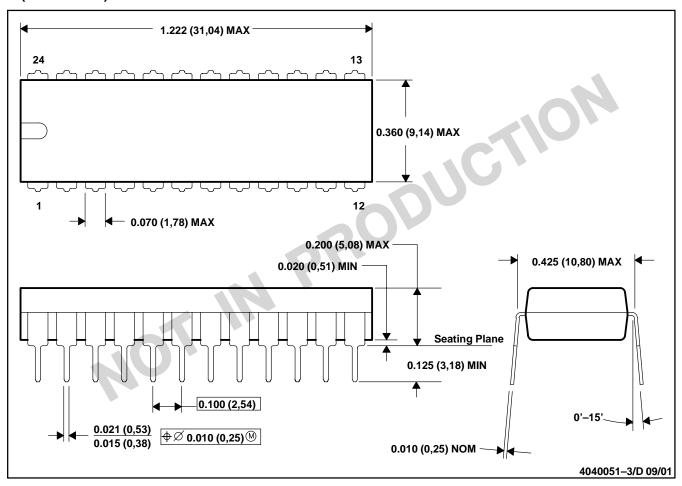

#### N (R-PDIP-T24)

#### PLASTIC DUAL-IN-LINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-010

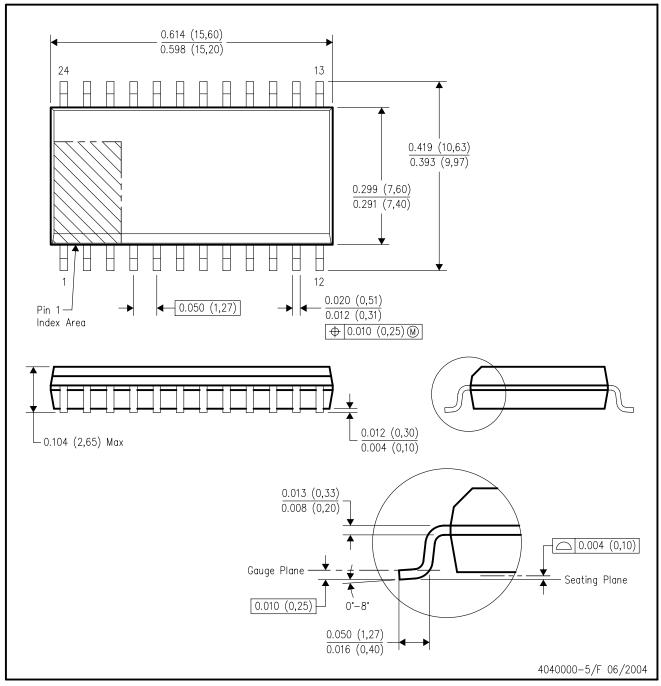

## DW (R-PDSO-G24)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AD.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Applications Amplifiers** amplifier.ti.com Audio www.ti.com/audio **Data Converters** dataconverter.ti.com Automotive www.ti.com/automotive **DLP® Products** www.dlp.com Communications and www.ti.com/communications Telecom DSP Computers and www.ti.com/computers dsp.ti.com Peripherals Clocks and Timers www.ti.com/clocks Consumer Electronics www.ti.com/consumer-apps Interface interface.ti.com **Energy** www.ti.com/energy Industrial www.ti.com/industrial Logic logic.ti.com Power Mgmt power.ti.com Medical www.ti.com/medical Microcontrollers microcontroller.ti.com www.ti.com/security Security **RFID** www.ti-rfid.com Space, Avionics & www.ti.com/space-avionics-defense Defense RF/IF and ZigBee® Solutions www.ti.com/lprf Video and Imaging www.ti.com/video www.ti.com/wireless-apps Wireless

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2010, Texas Instruments Incorporated