# Low Dropout Regulator

## **FEATURES**

- Low Resistance Pass Transistor:  $0.25\Omega$

- Dropout Voltage: 0.75V at 3A

- ±1% Reference Voltage

- Accurate Programmable Current Limit

- Shutdown Capability

- Internal Reference Available

- Full Remote Sense

- Low Quiescent Current: 2.5mA

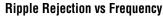

- Good High Frequency Ripple Rejection

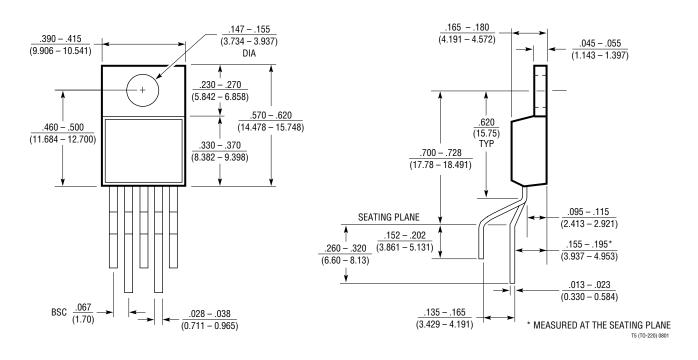

- Available in 5-Lead TO-220 and DD Packages

## DESCRIPTION

The LT $^{\$}$ 1185 is a 3A low dropout regulator with adjustable current limit and remote sense capability. It can be used as a positive output regulator with floating input or as a standard negative regulator with grounded input. The output voltage range is 2.5V to 25V, with  $\pm 1\%$  accuracy on the internal reference voltage.

The LT1185 uses a saturation-limited NPN transistor as the pass element. This device gives the linear dropout characteristics of a FET pass element with significantly less die area. High efficiency is maintained by using special anti-saturation circuitry that adjusts base drive to track load current. The "on resistance" is typically  $0.25\Omega$ .

Accurate current limit is programmed with a single 1/8W external resistor, with a range of zero to three amperes. A second, fixed internal limit circuit prevents destructive currents if the programming current is accidentally overranged. Shutdown of the regulator output is guaranteed when the program current is less than  $1\mu\text{A}$ , allowing external logic control of output voltage.

The LT1185 has all the protection features of previous LTC regulators, including power limiting and thermal shutdown.

7, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

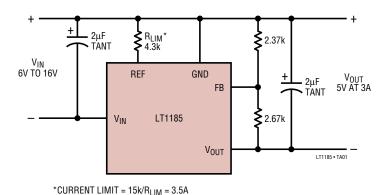

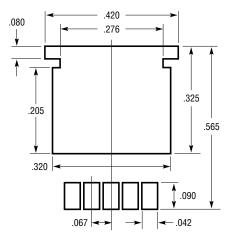

# TYPICAL APPLICATION

5V, 3A Regulator with 3.5A Current Limit

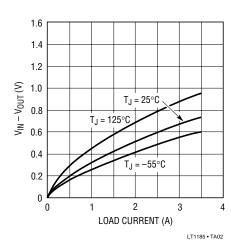

#### **Dropout Voltage**

L11185 • 1AUZ

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Input Voltage 35V                        | , |

|------------------------------------------|---|

| Input-Output Differential 30V            |   |

| FB Voltage 7V                            |   |

| REF Voltage 7V                           |   |

| Output Voltage                           |   |

| Output Reverse Voltage 2V                |   |

| Operating Ambient Temperature Range      |   |

| LT1185C 0°C to 70°C                      |   |

| LT1185I40°C to 85°C                      |   |

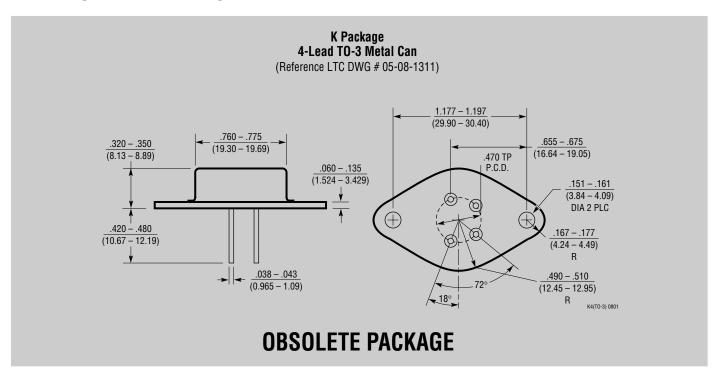

| LT1185M ( <b>OBSOLETE</b> )55°C to 125°C |   |

<sup>\*</sup>See Application Section for details on calculating Operation Junction Temperature

| Operating Junction Temperature Range* |       |    |       |

|---------------------------------------|-------|----|-------|

| Control Section                       |       |    |       |

| LT1185C                               | 0°C   | to | 125°C |

| LT1185I –                             | 40°C  | to | 125°C |

| LT1185M (OBSOLETE)                    | ·55°C | to | 150°C |

| Power Transistor Section              |       |    |       |

| LT1185C                               | 0°C   | to | 150°C |

| LT1185I –                             | 40°C  | to | 150°C |

| LT1185M (OBSOLETE)                    | .55°C | to | 175°C |

| Storage Temperature Range             | 65°C  | to | 150°C |

| Lead Temperature (Soldering, 10 sec)  |       |    | 300°C |

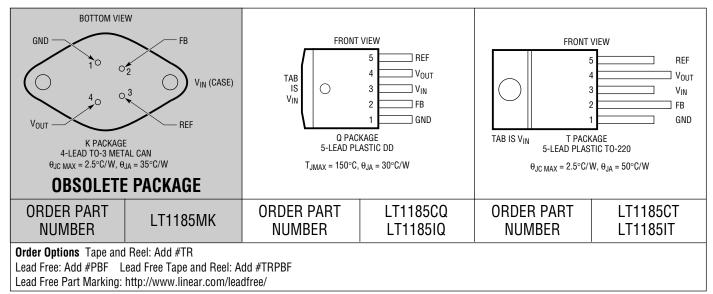

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Adjustable version,  $V_{IN} = 7.4V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 1mA$ ,  $R_{LIM} = 4.02k$ , unless otherwise noted.

| PARAMETER                                        | CONDITIONS                                                                                                                                                                                                                             |   | MIN | TYP          | MAX          | UNITS |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--------------|--------------|-------|

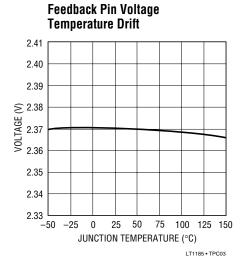

| Reference Voltage (At FB Pin)                    |                                                                                                                                                                                                                                        |   |     | 2.37         |              | V     |

| Reference Voltage Tolerance (At FB Pin) (Note 2) | V <sub>IN</sub> - V <sub>OUT</sub> = 5V, V <sub>OUT</sub> = V <sub>REF</sub>                                                                                                                                                           |   |     | 0.3          | ±1           | %     |

|                                                  | $\begin{split} &1\text{mA} \leq I_{OUT} \leq 3\text{A} \\ &V_{IN} - V_{OUT} = 1.2\text{V to } V_{IN} = 30\text{V} \\ &P \leq 25\text{W (Note 6), } V_{OUT} = 5\text{V} \\ &T_{MIN} \leq T_J \leq T_{MAX} \text{ (Note 9)} \end{split}$ | • |     | 1            | ±2.5         | %     |

| Feedback Pin Bias Current                        | V <sub>OUT</sub> = V <sub>REF</sub>                                                                                                                                                                                                    | • |     | 0.7          | 2            | μΑ    |

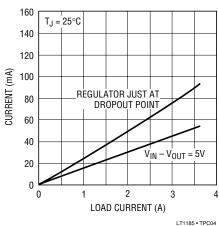

| Droput Voltage (Note 3)                          | $I_{OUT} = 0.5A, V_{OUT} = 5V$<br>$I_{OUT} = 3A, V_{OUT} = 5V$                                                                                                                                                                         |   |     | 0.20<br>0.67 | 0.37<br>1.00 | V     |

## **ELECTRICAL CHARACTERISTICS**

The ullet denotes specifications which apply over the operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Adjustable version,  $V_{IN} = 7.4V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 1mA$ ,  $R_{LIM} = 4.02k$ , unless otherwise noted.

| PARAMETER                                                            | CONDITIONS                                                                                                              |   | MIN                             | TYP                                            | MAX                                                          | UNITS                |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|---------------------------------|------------------------------------------------|--------------------------------------------------------------|----------------------|

| Load Regulation (Note 7)                                             | I <sub>OUT</sub> = 5mA to 3A<br>V <sub>IN</sub> - V <sub>OUT</sub> = 1.5V to 10V, V <sub>OUT</sub> = 5V                 |   |                                 | 0.05                                           | 0.3                                                          | %                    |

| Line Regulation (Note 7)                                             | $V_{IN} - V_{OUT} = 1V \text{ to } 20V, V_{OUT} = 5V$                                                                   |   |                                 | 0.002                                          | 0.01                                                         | %/V                  |

| Minimum Input Voltage                                                | I <sub>OUT</sub> = 1A (Note 4), V <sub>OUT</sub> = V <sub>REF</sub><br>I <sub>OUT</sub> = 3A                            |   |                                 | 4.0<br>4.3                                     |                                                              | V                    |

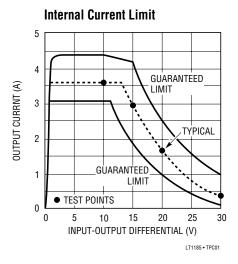

| Internal Current Limit (See Graph for<br>Guaranteed Curve) (Note 12) | $1.5V \le V_{IN} - V_{OUT} \le 10V$<br>$V_{IN} - V_{OUT} = 15V$<br>$V_{IN} - V_{OUT} = 20V$<br>$V_{IN} - V_{OUT} = 30V$ | • | 3.3<br>3.1<br>2.0<br>1.0<br>0.2 | 3.6<br>3.0<br>1.7<br>0.4                       | 4.2<br>4.4<br>4.2<br>2.6<br>1.0                              | A<br>A<br>A<br>A     |

| External Current Limit Programming Constant                          | 5k ≤ R <sub>LIM</sub> ≤ 15k, V <sub>OUT</sub> = 1V<br>(Note 11)                                                         | • |                                 | 15k                                            |                                                              | Α•Ω                  |

| External Current Limit Error                                         | $1A \le I_{LIM} \le 3A$ $R_{LIM} = 15k \bullet A/I_{LIM}$                                                               | • |                                 | 0.02 I <sub>LIM</sub><br>0.04 I <sub>LIM</sub> | 0.06 I <sub>LIM</sub> + 0.03<br>0.09 I <sub>LIM</sub> + 0.05 | A<br>A               |

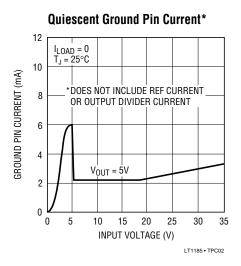

| Quiescent Supply Current                                             | $I_{OUT} = 5$ mA, $V_{OUT} = V_{REF}$<br>$4$ V $\leq$ $V_{IN} \leq$ 25V (Note 5)                                        | • |                                 | 2.5                                            | 3.5                                                          | mA                   |

| Supply Current Change with Load                                      | $V_{IN} - V_{OUT} = V_{SAT}$ (Note 10)<br>$V_{IN} - V_{OUT} \ge 2V$                                                     | • |                                 | 25<br>10                                       | 40<br>25                                                     | mA/A<br>mA/A         |

| REF Pin Shutoff Current                                              |                                                                                                                         | • | 0.4                             | 2                                              | 7                                                            | μА                   |

| Thermal Regulation (See Applications Information)                    | V <sub>IN</sub> – V <sub>OUT</sub> = 10V<br>I <sub>OUT</sub> = 5mA to 2A                                                |   |                                 | 0.005                                          | 0.014                                                        | %/W                  |

| Reference Voltage Temperature Coefficient                            | (Note 8)                                                                                                                |   |                                 | 0.003                                          | 0.01                                                         | %/°C                 |

| Thermal Resistance Junction to Case                                  | TO-3 Control Area Power Transistor TO-220 Control Area Power Transistor                                                 |   |                                 |                                                | 1<br>3<br>1<br>3                                             | °C/W<br>°C/W<br>°C/W |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Reference voltage is guaranteed both at nominal conditions (no load, 25°C) and at worst-case conditions of load, line, power and temperature. An intermediate value can be calculated by adding the effects of these variables in the actual application. See the Applications Information section of this data sheet.

**Note 3:** Dropout voltage is tested by reducing input voltage until the output drops 1% below its nominal value. Tests are done at 0.5A and 3A. The power transistor looks basically like a pure resistance in this range so that minimum differential at any intermediate current can be calculated by interpolation;  $V_{DROPOUT} = 0.25V + 0.25\Omega \cdot I_{OUT}$ . For load current less than 0.5A, see graph.

**Note 4:** "Minimum input voltage" is limited by base emitter voltage drive of the power transistor section, not saturation as measured in Note 3. For output voltages below 4V, "minimum input voltage" specification may limit dropout voltage before transistor saturation limitation.

**Note 5:** Supply current is measured on the ground pin, and does not include load current,  $R_{LIM}$ , or output divider current.

**Note 6:** The 25W power level is guaranteed for an input-output voltage of 8.3V to 17V. At lower voltages the 3A limit applies, and at higher voltages the internal power limiting may restrict regulator power below 25W. See graphs.

**Note 7:** Line and load regulation are measured on a pulse basis with a pulse width of  $\approx 2$ ms, to minimize heating. DC regulation will be affected by thermal regulation and temperature coefficient of the reference. See Applications Information section for details.

**Note 8:** Guaranteed by design and correlation to other tests, but not tested.

**Note 9:**  $T_{JMIN} = 0^{\circ}C$  for the LT1185C,  $-40^{\circ}C$  for LT1185I, and  $-55^{\circ}C$  for the LT1185M. Power transistor area and control circuit area have different maximum junction temperatures. Control area limits are  $T_{JMAX} = 125^{\circ}C$  for the LT1185C and LT1185I and 150°C for the LT1185M. Power area limits are 150°C for LT1185C and LT1185I and 175°C for LT1185M.

**Note 10:**  $V_{SAT}$  is the maximum specified dropout voltage;  $0.25V + 0.25 \cdot I_{OLIT}$ .

**Note 11:** Current limit is programmed with a resistor from REF pin to GND pin. The value is  $15k/I_{LIM}$ .

Note 12: For  $V_{IN} - V_{OUT} = 1.5V$ ;  $V_{IN} = 5V$ ,  $V_{OUT} = 3.5V$ .  $V_{OUT} = 1V$  for all other current limit tests.

# TYPICAL PERFORMANCE CHARACTERISTICS

#### **Ground Pin Current**

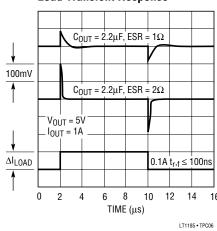

#### **Load Transient Response**

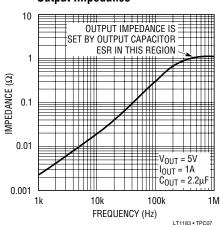

### **Output Impedance**

LINEAR

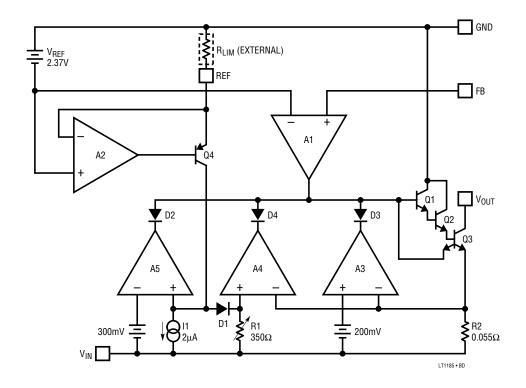

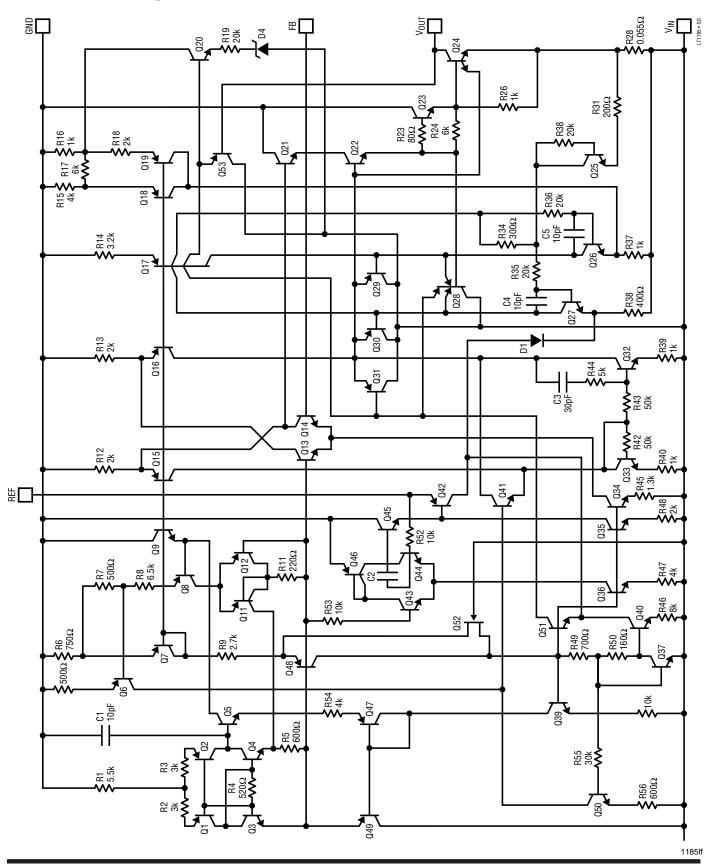

## **Block Diagram**

A simplified block diagram of the LT1185 is shown in Figure 1. A 2.37V bandgap reference is used to bias the input of the error amplifier A1, and the reference amplifier A2. A1 feeds a triple NPN pass transistor stage which has the two driver collectors tied to ground so that the main pass transistor can completely saturate. This topology normally has a problem with unlimited current in Q1 and Q2 when the input voltage is less than the minimum required to create a regulated output. The standard "fix" for this problem is to insert a resistor in series with Q1 and Q2 collectors, but this resistor must be low enough in value to supply full base current for Q3 under worst-case

conditions, resulting in very high supply current when the input voltage is low. To avoid this situation, the LT1185 uses an auxiliary emitter on Q3 to create a drive limiting feedback loop which automatically adjusts the drive to Q1 so that the base drive to Q3 is just enough to saturate Q3, but no more. Under saturation conditions, the auxiliary emitter is acting like a collector to shunt away the output current of A1. When the input voltage is high enough to keep Q3 out of saturation, the auxiliary emitter current drops to zero even when Q3 is conducting full load current.

Figure 1. Block Diagram

Amplifier A2 is used to generate an internal current through Q4 when an external resistor is connected from the REF pin to ground. This current is equal to 2.37V divided by  $R_{LIM}$ . It generates a current limit sense voltage across R1. The regulator will current limit via A4 when the voltage across R2 is equal to the voltage across R1. These two resistors essentially form a current "amplifier" with a gain of 350/0.055 = 6,360. Good temperature drift is inherent because R1 and R2 are made from the same diffusions. Their ratio, not absolute value, determines current limit. Initial accuracy is enhanced by trimming R1 slightly at wafer level. Current limit is equal to  $15k\Omega/R_{LIM}$ .

D1 and  $I_1$  are used to guarantee regulator shutdown when REF pin current drops below  $2\mu A$ . A current less than  $2\mu A$  through Q4 causes the +input of A5 to go low and shut down the regulator via D2.

A3 is an internal current limit amplifier which can override the external current limit. It provides "goof proof" protection for the pass transistor. Although not shown, A3 has a nonlinear foldback characteristic at input-output voltages above 12V to guarantee safe area protection for Q3. See the graph, Internal Current Limit in the Typical Performance Characteristics of this data sheet.

## **Setting Output Voltage**

The LT1185 output voltage is set by two external resistors (see Figure 2). Internal reference voltage is trimmed to 2.37V so that a standard 1% 2.37k resistor (R1) can be used to set divider current at 1mA. R2 is then selected from:

R2 =

$$\frac{(V_{OUT} - 2.37) R1}{V_{REF}}$$

for R1 = 2.37k and  $V_{REF}$  = 2.37V, this reduces to:

$$R2 = V_{OUT} - 2.37k$$

suggested values of 1% resistors are shown.

| V <sub>OUT</sub> | R2 WHEN R1 = 2.37k |

|------------------|--------------------|

| 5V               | 2.67k              |

| 5.2V             | 2.87k              |

| 6V               | 3.65k              |

| 12V              | 9.76k              |

| 15V              | 12.7k              |

## **Output Capacitor**

The LT1185 has a collector output NPN pass transistor, which makes the open-loop output impedance much higher than an emitter follower. Open-loop gain is a direct function of load impedance, and causes a main-loop "pole" to be created by the output capacitor, in addition to an internal pole in the error amplifier. To ensure loop stability, the output capacitor must have an ESR (effective series resistance) which has an upper limit of  $2\Omega$ , and a lower limit of 0.2 divided by the capacitance in  $\mu F$ . A  $2\mu F$ output capacitor, for instance, should have a maximum ESR of  $2\Omega$ , and a minimum of  $0.2/2 = 0.1\Omega$ . These values are easily encompassed by standard solid tantalum capacitors, but occasionally a solid tantalum unit will have abnormally high ESR, especially at very low temperatures. The suggested 2µF value shown in the circuit applications should be increased to  $4.7\mu$ F for  $-40^{\circ}$ C and -55°C designs if the 2µF units cannot be guaranteed to stay below  $2\Omega$  at these temperatures.

Although solid tantalum capacitors are suggested, other types can be used if they meet the ESR requirements. Standard aluminum electrolytic capacitors need to be upward of  $25\mu F$  in general to hold  $2\Omega$  maximum ESR, especially at low temperatures. Ceramic, plastic film, and monolithic capacitors have a problem with ESR being too *low*. These types should have a  $1\Omega$  carbon resistor in series to guarantee loop stability.

The output capacitor should be located close to the regulator ( $\leq$ 3") to avoid excessive impedance due to lead inductance. A six inch lead length ( $2 \cdot 3$ ") will generate an extra  $0.8\Omega$  inductive reactance at 1MHz, and unity-gain frequency can be up to that value.

For remote sense applications, the capacitor should still be located close to the regulator. Additional capacitance can be added at the remote sense point, but the remote capacitor must be at least  $2\mu F$  solid tantalum. It cannot be a low ESR type like ceramic or mylar unless a  $0.5\Omega$  to  $1\Omega$  carbon resistor is added in series with the capacitor. Logic boards with multiple low ESR bypass capacitors should have a solid tantalum unit added in parallel whose value is approximately five times the combined value of low ESR capacitors.

Large output capacitors (electrolytic or solid tantalum) will not cause the LT1185 to oscillate, but they will cause a damped "ringing" at light load currents where the ESR of the capacitor is several orders of magnitude lower than the load resistance. This ringing only occurs as a result of transient load or line conditions and normally causes no problems because of its low amplitude ( $\leq 25$ mV).

## **Heat Sinking**

The LT1185 will normally be used with a heat sink. The size of the heat sink is determined by load current, input and output voltage, ambient temperature, and the thermal resistance of the regulator, junction-to-case  $(\theta_{JC})$ . The LT1185 has two separate values for  $\theta_{JC}$ : one for the power transistor section, and a second, lower value for the control section. The reason for two values is that the power transistor is capable of operating at higher continuous temperature than the control circuitry. At low power levels, the two areas are at nearly the same temperature, and maximum temperature is limited by the control area. At high power levels, the power transistor will be at a significantly higher temperature than the control area and its maximum operating temperature will be the limiting factor.

To calculate heat sink requirements, you must solve a thermal resistance formula twice, one for the power transistor and one for the control area. The *lowest* value obtained for heat sink thermal resistance must be used. In these equations, two values for maximum junction temperature and junction-to-case thermal resistance are used, as given in Electrical Specifications.

$$\theta_{HS} = \frac{(T_{JMAX} - T_{AMAX})}{P} - \theta_{JC} - \theta_{CHS}.$$

$\theta_{HS}$  = Maximum heat sink thermal resistance

$\theta_{JC}$  = LT1185 junction-to-case thermal resistance

$\theta_{CHS}$  = Case-to-heat sink (interface) thermal resistance, including any insulating washers

T<sub>JMAX</sub> = LT1185 maximum operating junction temperature

T<sub>AMAX</sub> = Maximum ambient temperature in customers application

P = Device dissipaton =  $(V_{IN} - V_{OUT}) (I_{OUT}) + \frac{I_{OUT}}{40} (V_{IN})$  **Example:** A commercial version of the LT1185 in the TO-220 package is to be used with a maximum ambient temperature of 60°C. Output voltage is 5V at 2A. Input voltage can vary from 6V to 10V. Assume an interface resistance of 1°C/W.

First solve for control area, where the maximum junction temperature is 125°C for the TO-220 package, and  $\theta_{JC}$  = 1°C/W:

$$P = (10V - 5V) (2A) + \frac{2A}{40} (10V) = 10.5W$$

$$\theta_{HS} = \frac{125^{\circ}\text{C} - 60^{\circ}\text{C}}{10.5\text{W}} - 1^{\circ}\text{C/W} - 1^{\circ}\text{C/W} = 4.2^{\circ}\text{C/W}$$

Next, solve for power transistor limitation, with  $T_{JMAX} = 150^{\circ}C$ ,  $\theta_{JC} = 3^{\circ}C/W$ :

$$\theta_{HS} = \frac{150 - 60}{10.5} - 3 - 1 = 4.6$$

°C/W

The lowest number must be used, so heat sink resistance must be less than 4.2°C/W.

Some heat sink data sheets show graphs of heat sink temperature rise vs power dissipation instead of listing a value for thermal resistance. The formula for  $\theta_{HS}$  can be rearranged to solve for maximum heat sink temperature rise:

$$\Delta T_{HS} = T_{JMAX} - T_{AMAX} - P(\theta_{JC} + \theta_{CHS})$$

Using numbers from the previous example:

$$\Delta T_{HS} = 125^{\circ}C - 60 - 10.5(1 + 1) = 44^{\circ}C$$

control section

$$\Delta T_{HS} = 150^{\circ}C - 60 - 10.5(3 + 1) = 48^{\circ}C$$

power transistor

The smallest rise must be used, so heat sink temperature rise must be less than 44°C at a power level of 10.5W.

For board level applications, where heat sink size may be critical, one is often tempted to use a heat sink which barely meets the requirements. This is permissible *if* correct assumptions were made concerning maximum ambient temperature and power levels. One complicating

factor is that local ambient temperature may be somewhat higher because of the point source of heat. The consequences of excess junction temperature include poor reliability, especially for plastic packages, and the possibility of thermal shutdown or degraded electrical characteristics. The final design should be checked *in situ* with a thermocouple attached to the regulator case under worst-case conditions of high ambient, high input voltage and full load.

#### What About Overloads?

IC regulators with thermal shutdown, like the LT1185, allow heat sink designs which concentrate on worst-case "normal" conditions and ignore "fault" conditions. An output overload or short may force the regulator to exceed its maximum junction temperature rating, but thermal shutdown is designed to prevent regulator failure under these conditions. A word of caution however; thermal shutdown temperatures are typically 175°C in the control portion of the die and 180°C to 225°C in the power transistor section. Extended operation at these temperatures can cause permanent degradation of plastic encapsulation. Designs which may be subjected to extended periods of overload should either use the hermetic TO-3 package or increase heat sink size. Foldback current limiting can be implemented to minimize power levels under fault conditions.

#### **External Current Limit**

The LT1185 requires a resistor to set current limit. The value of this resistor is 15k divided by the desired current limit (in amps). The resistor for 2A current limit would be 15k/2A = 7.5k. Tolerance over temperature is  $\pm 10\%$ , so current limit is normally set 15% above maximum load current. Foldback limiting can be employed if short-circuit current must be lower than full load current (see Typical Applications).

The LT1185 has internal current limiting which will override external current limit if power in the pass transistor is excessive. The internal limit is  $\approx 3.6A$  with a foldback characteristic which is dependent on input-output voltage, not output voltage *per se* (see Typical Performace Characteristics).

#### **Ground Pin Current**

Ground pin current for the LT1185 is approximately 2mA plus  $I_{OUT}/40$ . At  $I_{OUT}=3A$ , ground pin current is typically 2mA + 3/40=77mA. Worst case guarantees on the ratio of  $I_{OUT}$  to ground pin current are contained in the Electrical Specifications.

Ground pin current can be important for two reasons. It adds to power dissipation in the regulator and it can affect load/line regulation if a long line is run from the ground pin to load ground. The additional power dissipation is found by multiplying ground pin current by input voltage. In a typical example, with  $V_{IN} = 8V$ ,  $V_{OUT} = 5V$  and  $I_{OUT} = 2A$ , the LT1185 will dissipate (8V - 5V)(2A) = 6W in the pass transistor and (2A/40)(8V) = 0.4W in the internal drive circuitry. This is only a 1.5% efficiency loss, and a 6.7% increase in regulator power dissipation, but these values will increase at higher output voltages.

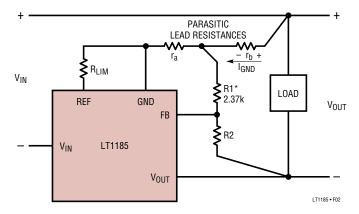

Ground pin current can affect regulation as shown in Figure 2. Parasitic resistance in the ground pin lead will create a voltage drop which *increases* output voltage as load current is increased. Similarly, output voltage can *decrease* as input voltage increases because the "I<sub>OUT</sub>/40" component of ground pin current drops significantly at higher input-output differentials. These effects are small enough to be ignored for local regulation applications, but

\*R1 SHOULD BE CONNECTED DIRECTLY TO GROUND LEAD, NOT TO THE LOAD, SO THAT  $r_a\approx0$ 1. THIS LIMITS THE OUTPUT VOLTAGE ERROR TO  $(l_{GND})(r_b)$ . ERRORS CREATED BY  $r_a$  ARE MULTIPLIED BY  $(l_1+R2/R1)$ . NOTE THAT  $V_{OUT}$  *INCREASES* WITH INCREASING GROUND PIN CURRENT. R2 SHOULD BE CONNECTED DIRECTLY TO LOAD FOR REMOTE SENSING

Figure 2. Proper Connection of Positive Sense Lead

for remote sense applications, they may need to be considered. Ground lead resistance of  $0.4\Omega$  would cause an output voltage error of up to  $(3A/40)(0.4\Omega)=30\text{mV},$  or 0.6% at  $V_{OUT}=5\text{V}.$  Note that if the sense leads are connected as shown in Figure 2, with  $r_a\approx0\Omega,$  this error is a fixed number of millivolts, and does not increase as a function of DC output voltage.

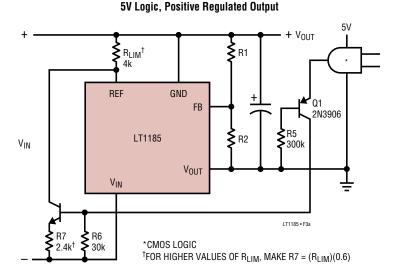

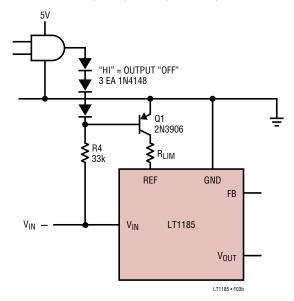

## **Shutdown Techniques**

The LT1185 can be shut down by open-circuiting the REF pin. The current flowing into this pin must be less than  $0.4\mu A$  to guarantee shutdown. Figure 3 details several ways to create the "open" condition, with various logic levels. For variations on these schemes, simply remember that the voltage on the REF pin is 2.4V negative with respect to the ground pin.

## **Output Overshoot**

Very high input voltage slew rate during start-up may cause the LT1185 output to overshoot. Up to 20% overshoot could occur with input voltage ramp-up rate exceeding  $1V/\mu s$ . This condition cannot occur with normal 50Hz

to 400Hz rectified AC inputs because parasitic resistance and inductance will limit rate of rise even if the power switch is closed at the peak of the AC line voltage. This assumes that the switch is in the AC portion of the circuit. If instead, a switch is placed directly in the regulator input so that a large filter capacitor is precharged, fast input slew rates will occur on switch closure. The output of the regulator will slew at a rate set by current limit and output capacitor size; dVdt =  $I_{LIM}/C_{OUT}$ . With  $I_{LIM}$  = 3.6A and  $C_{OUT}$  = 2.2 $\mu$ F, the output will slew at 1.6V/ $\mu$ s and overshoot can occur. This overshoot can be reduced to a few hundred millivolts or less by increasing the output capacitor to  $10\mu$ F and/or reducing current limit so that output slew rate is held below 0.5V/ $\mu$ s.

A second possibility for creating output overshoot is recovery from an output short. Again, the output slews at a rate set by current limit and output capacitance. To avoid overshoot, the ratio  $I_{LIM}/C_{OUT}$  should be less than  $0.5\times10^6$ . Remember that load capacitance can be added to  $C_{OUT}$  for this calculation. Many loads will have multiple supply bypass capacitors that total more than  $C_{OUT}$ .

**5V Logic, Negative Regulated Output**

Figure 3. Shutdown Techniques

## **Thermal Regulation**

IC regulators have a regulation term not found in discrete designs because the power transistor is thermally coupled to the reference. This creates a shift in the output voltage which is proportional to power dissipation in the regulator.

$$\Delta V_{OUT} = P(K1 + K2 \Theta_{JA})$$

$$= (I_{OUT})(V_{IN} - V_{OUT})(K1 + K2 \Theta_{JA})$$

K1 and K2 are constants. K1 is a fast time constant effect caused by die temperature *gradients* which are established within 50ms of a power change. K1 is specified on the data sheet as thermal regulation, in percent per watt.

K2 is a long time constant term caused by the temperature drift of the regulator reference voltage. It is also specified, but in percent per degree centigrade. It must be multiplied by overall thermal resistance, junction-to-ambient,  $\theta_{JA}$ .

As an example, assume a 5V regulator with an input voltage of 8V, load current of 2A, and a total thermal resistance of  $4^{\circ}$ C/W, including junction-to-case, (use control area specification), interface, and heat sink resistance. K1 and K2, respectively, from the data sheet are 0.014%/W and 0.01%/°C.

$$\Delta V_{OUT} = (2A)(8V - 5V)(0.014 + 0.01 \cdot 4)$$

= 0.32%

This shift in output voltage could be in either direction because K1 and K2 can be either positive or negative.

Thermal regulation is already included in the worst case reference specification.

### **Output Voltage Reversal**

Some IC regulators suffer from a latch-up state when their output is forced to a reverse voltage of as little as one diode drop. The latch-up state can be triggered without a fault condition when the load is connected to an opposite polarity supply instead of to ground. If the second supply is turned on first, it will pull the output of the first supply to a reverse voltage through the load. The first supply may then latch off when turned on. This problem is particularly annoying because the diode clamps which should always be used to protect against polarity reversal do not usually stop the latch-up problem.

The LT1185 is designed to allow output reverse polarity of several volts without damage or latch-up, so that a simple diode clamp can be used.

# TYPICAL APPLICATIONS

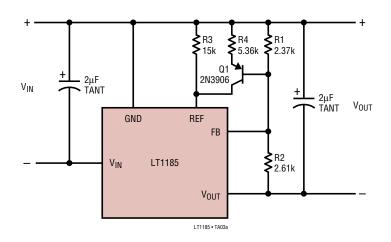

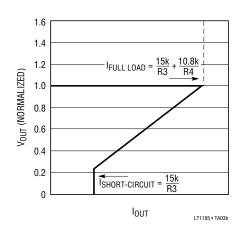

### **Foldback Current Limiting**

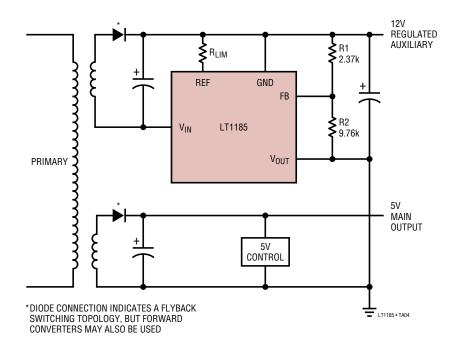

### Auxiliary + 12V Low Dropout Regulator for Switching Supply

# TYPICAL APPLICATIONS

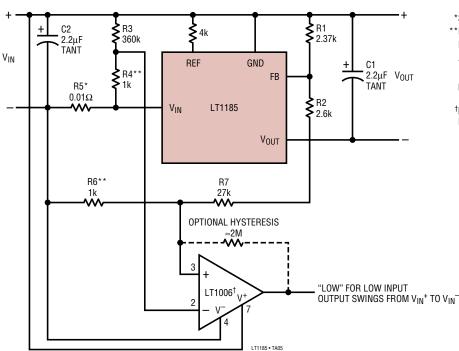

### **Low Input Voltage Monitor Tracks Dropout Characteristics**

- \*3" #26 WIRE

- \*\*R4 DETERMINES TRIP POINT AT  $I_{OUT} = 0$ R6 DETERMINES INCREASE OF TRIP POINT AS  $I_{OUT}$  INCREASES TRIP POINT FOR  $V_{IN} = V_{OUT} \left(1 + \frac{R4 \cdot R7}{R3 \cdot R6}\right) + I_{OUT} \frac{R5 \cdot R7}{R6}$

FOR VALUES SHOWN, TRIP POINT FOR  $V_{IN}$  IS:  $V_{OUT}+0.37V$  AT  $I_{OUT}=0$  AND  $V_{OUT}=1.18V$  AT  $I_{OUT}=3A$   $^{\dagger}DO$  NOT SUBSTITUTE. OP AMP MUST HAVE COMMON MODE RANGE EQUAL TO NEGATIVE SUPPLY

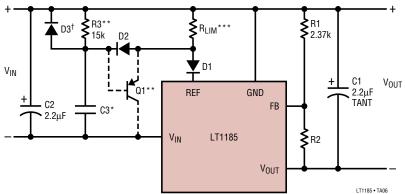

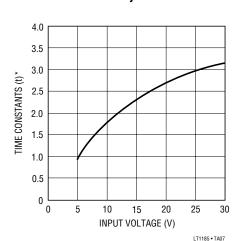

#### Time Delayed Start-Up

ALL DIODES 1N4148

- \*SEE CHART FOR DELAY TIME VERSUS (C3)(R3//R<sub>LIM</sub>) PRODUCT

- \*\*FOR LONG DELAY TIMES, REPLACE D2 WITH 2N3906 TRANSISTOR AND USE R3 ONLY FOR CALCULATING DELAY TIME. R3 CAN INCREASE TO 100k

- \*\*\*\*I<sub>LIM</sub> IS ≈11k/R<sub>LIM</sub>, INSTEAD OF 15k, BECAUSE OF VOLTAGE DROP IN D1. TEMPERATURE COEFFICIENT OF I<sub>LIM</sub> WILL BE ≈0.11%/°C, SO ADEQUATE MARGIN MUST BE ALLOWED FOR COLD OPERATION

$^{\dagger}$ D3 PROVIDES FAST RESET OF TIMING. INPUT MUST DROP TO A LOW VALUE TO RESET TIMING

### **Delay Time**

$^{\star}t=(R3//R_{LIM})(C3)=\left(\frac{R3\bullet R_{LIM}}{R3+R_{LIM}}\right)(C3)$

# **SCHEMATIC DIAGRAM**

# PACKAGE DESCRIPTION

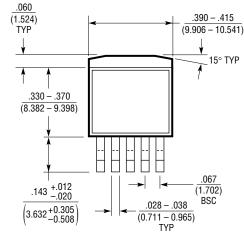

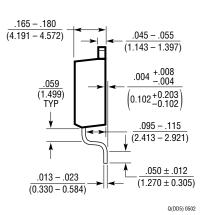

## T Package 5-Lead Plastic TO-220 (Standard)

(Reference LTC DWG # 05-08-1421)

LINEAR TECHNOLOGY

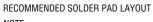

# PACKAGE DESCRIPTION

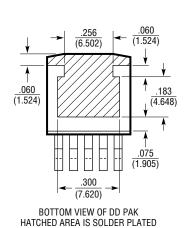

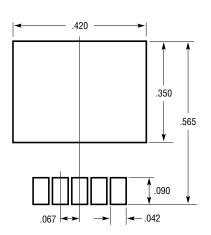

### Q Package 5-Lead Plastic DD Pak

(Reference LTC DWG # 05-08-1461)

COPPER HEAT SINK

- 1. DIMENSIONS IN INCH/(MILLIMETER)

- 2. DRAWING NOT TO SCALE

RECOMMENDED SOLDER PAD LAYOUT FOR THICKER SOLDER PASTE APPLICATIONS

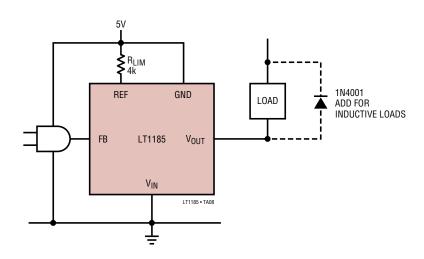

# TYPICAL APPLICATIONS

### Logic Controlled 3A Low-Side Switch with Fault Protection

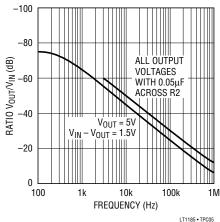

## Improved High Frequency Ripple Rejection

NOTE: C3 IMPOVES HIGH FREQUENCY RIPPLE REJECTION BY 6dB AT  $v_{OUT}$  = 5V, AND BY 14dB AT  $v_{OUT}$  = 12V. C1 IS INCREASED TO 4.7 $\mu\text{F}$  TO ENSURE GOOD STABILTITY WHEN C3 IS USED

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                        | COMMENTS                                                                                                                       |

|-------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| LT1085      | 7.5A Low Dropout Regulator                         | 1V Dropout Voltage                                                                                                             |

| LT1117      | 800mA Low Dropout Regulator with Shutdown          | Reverse Voltage and Reverse Current Protection                                                                                 |

| LT1120A     | Micropower Regulator with Comparator and Shutdown  | 20μA Supply Current, 2.5V Reference Output                                                                                     |

| LT1129      | 200mA Micropower Low Dropout Regulator             | 400mV Dropout Voltage, 50μA Supply Current                                                                                     |

| LT1175      | 500mA Negative Low Dropout Micropower Regulator    | 45μA Supply Current, Adjustable Current Limit                                                                                  |

| LT1585      | 4.6A Low Dropout Fast Transient Response Regulator | For High Performance Microprocessors                                                                                           |

| LT1964      | 200mA, Low Noise Micropower, Negative LDO          | $V_{IN}$ : -0.9V to -20V, $V_{OUT(MIN)}$ = -1.21V, $V_{DO}$ = 0.34V, $I_Q$ = 30 $\mu$ A, $I_{SD}$ = 3 $\mu$ A, ThinSOT Package |

LT/LWI 0906 REV F • PRINTED IN USA

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 1994