# 具停机功能的6通道、 14位、600ksps 同时采样 ADC

## 特点

- 具有 6 个同时采样差分输入的 600ksps ADC

- 每个通道的吞吐速率为 100ksps

- 76dB SINAD

- 低功耗 : 15mW

- 3V 单电源操作

- 2.5V 内部带隙基准，可利用外部基准进行过驱动

- 三线式串行接口

- 内部转换由 CONV 引脚来触发

- 睡眠 (6 $\mu$ W) 停机模式

- 打盹 (3.3mW) 停机模式

- 0V 至 2.5V 单极、或  $\pm$ 1.25V 双极差分输入范围

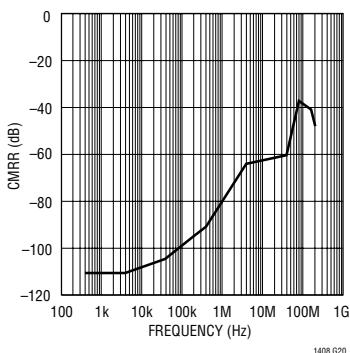

- 90dB 共模抑制

- 纤巧型 32 引脚 (5mm  $\times$  5mm) QFN 封装

## 应用

- 多相功率测量

- 多相电机控制

- 数据采集系统

- 不间断电源

**L**、**LTC**、**LT** 和 **LTM** 是凌力尔特公司的注册商标。所有其他商标均为其各自拥有者的产权。受包括第 6084440、6522187 号美国专利的保护。

## 描述

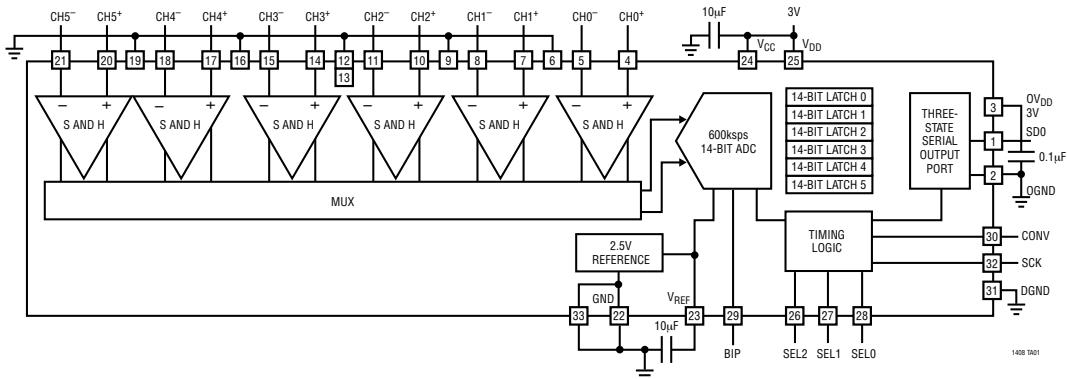

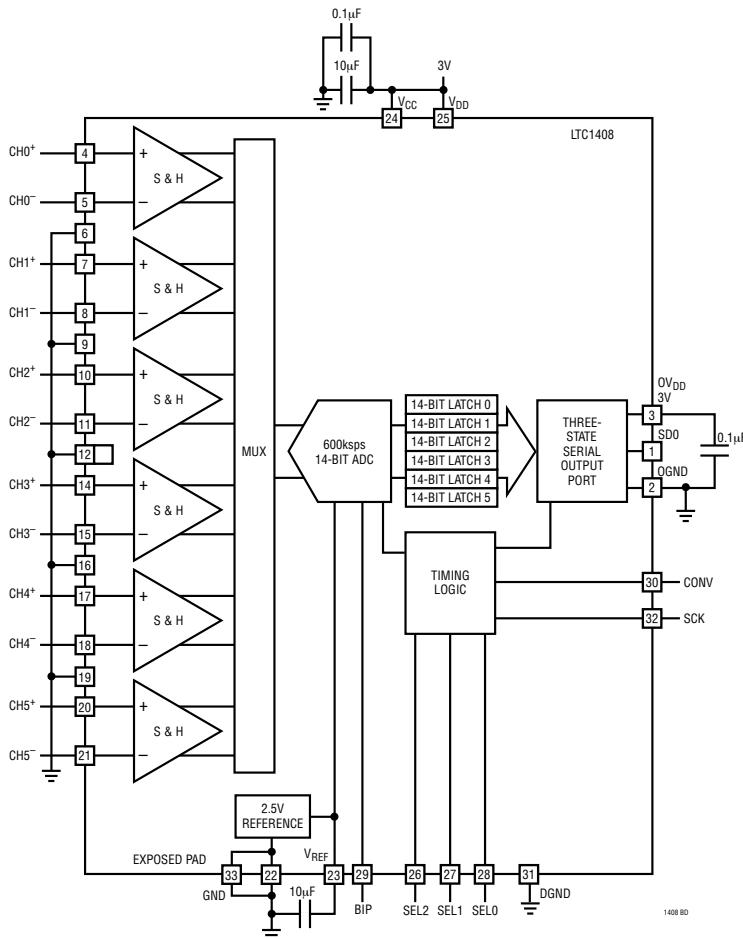

LTC<sup>®</sup>1408 是一款具有 6 个同时采样差分输入的 14 位、600ksps ADC。该器件采用纤巧型 32 引脚 (5mm  $\times$  5mm) QFN 封装，当采用单 3V 电源时，其电流消耗仅为 5mA。睡眠停机功能可将功耗降低至 6 $\mu$ W。低功耗与纤巧型封装的结合令 LTC1408 成为便携式应用的合适之选。

LTC1408 具有 6 个单独的差分输入，它们在 CONV 信号的上升沿上同时进行采样。然后，以每通道 100ksps 的速率对这 6 个采样输入进行转换。

共模抑制达 90dB，这使得用户能够通过从信号源对信号进行差分测量来消除接地环路和共模噪声。

根据 BIP 引脚状态的不同，该器件可对 0V 至 2.5V 单极输入 (或  $\pm$ 1.25V 双极输入) 实施差分转换。任何模拟输入均可拥有轨至轨摆幅，只要差分输入范围得以保持即可。

视 SEL2、SEL1 和 SEL0 输入的逻辑状态的不同，可压缩转换序列，以对 6 个以下的通道进行转换。

串行接口通过 96 个时钟将 6 个转换结果发出，以便与标准串行接口相兼容。

## 典型应用

## 绝对最大额定值 (注1、2)

电源电压 ( $V_{DD}$ ,  $V_{CC}$ ,  $OV_{DD}$ ) ..... 4V

模拟输入电压

(注3) ..... -0.3V 至 ( $V_{DD}$  + 0.3V)

数字输入电压 ..... -0.3V 至 ( $V_{DD}$  + 0.3V)

数字输出电压 ..... -0.3V 至 ( $V_{DD}$  + 0.3V)

功耗 ..... 100mW

工作温度范围

LTC1408C ..... 0°C 至 70°C

LTC1408I ..... -40°C 至 85°C

贮存温度范围 ..... -65°C 至 125°C

## 封装/订购信息

|      |                          |

|------|--------------------------|

| 产品型号 | LTC1408CUH<br>LTC1408IUH |

|      | QFN 器件标记                 |

| 1408 |                          |

TOP VIEW

32-PIN (3mm x 5mm) PLASTIC QFN

$T_{JMAX} = 125^{\circ}\text{C}$ ,  $\theta_{JA} = 34^{\circ}\text{C/W}$

EXPOSED PIN IS GND (PAD 33)

MUST BE SOLDERED TO PCB

## 订购选项 卷带：加 #TR

无铅型：加 #PBF 无铅型卷带：加 #TRPBF

无铅型器件标记：<http://www.linear.com/leadfree/>

对于规定工作温度范围更宽的器件，请咨询凌力尔特公司。

电特性 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^{\circ}\text{C}$ 。采用内部基准， $V_{DD} = 3\text{V}$ ，

$V_{DD} = V_{CC} = 3\text{V}$ 。

| 参数                | 条件                | 最小值    | 典型值       | 最大值 | 单位                                                 |

|-------------------|-------------------|--------|-----------|-----|----------------------------------------------------|

| 分辨率(无漏失码)         |                   | ● 14   |           |     | 位                                                  |

| 积分线性误差            | (注 5)             | ● -3   | $\pm 0.5$ | 3   | LSB                                                |

| 失调误差              | (注 4)             | ● -4.5 | $\pm 1$   | 4.5 | mV                                                 |

| 从 CH0 至 CH5 的失调匹配 |                   | -3     | $\pm 0.5$ | 3   | mV                                                 |

| 范围误差              | (注 4)             | ● -12  | $\pm 2$   | 12  | mV                                                 |

| 从 CH0 至 CH5 的范围匹配 |                   | -5     | $\pm 1$   | 5   | mV                                                 |

| 范围温度系数            | 内部基准(注 4)<br>外部基准 |        | $\pm 15$  |     | ppm/ $^{\circ}\text{C}$<br>ppm/ $^{\circ}\text{C}$ |

模拟输入 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^{\circ}\text{C}$ 。采用内部基准， $V_{DD} = 3\text{V}$ ，

$V_{DD} = V_{CC} = 3\text{V}$ 。

| 符号           | 参数                  | 条件                                                                                                           | 最小值          | 典型值 | 最大值 | 单位            |

|--------------|---------------------|--------------------------------------------------------------------------------------------------------------|--------------|-----|-----|---------------|

| $V_{IN}$     | 模拟差分输入范围(注 3, 8, 9) | $2.7\text{V} \leq V_{DD} \leq 3.3\text{V}$                                                                   | 0 至 2.5      |     |     | V             |

| $V_{CM}$     | 模拟共模 + 差分输入范围       | (注 8)                                                                                                        | 0 至 $V_{DD}$ |     |     | V             |

| $I_{IN}$     | 模拟输入漏电流             |                                                                                                              | ● 1          |     |     | $\mu\text{A}$ |

| $C_{IN}$     | 模拟输入电容              |                                                                                                              |              | 13  |     | pF            |

| $t_{ACQ}$    | 采样及保持采集时间           | (注 6)                                                                                                        | ● 39         |     |     | ns            |

| $t_{AP}$     | 采样及保持孔径延迟时间         |                                                                                                              |              | 1   |     | ns            |

| $t_{JITTER}$ | 采样及保持孔径延迟时间抖动       |                                                                                                              |              | 0.3 |     | ps            |

| $t_{SK}$     | 通道至通道孔径时滞           |                                                                                                              |              | 200 |     | ps            |

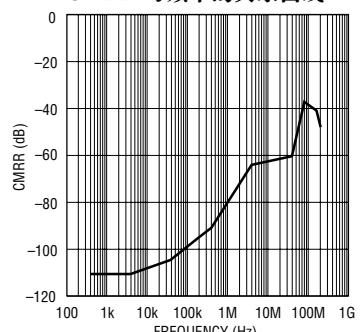

| CMRR         | 模拟输入共模抑制比           | $f_{IN} = 100\text{kHz}$ , $V_{IN} = 0\text{V}$ 至 3V<br>$f_{IN} = 100\text{kHz}$ , $V_{IN} = 0\text{V}$ 至 3V | -83<br>-67   |     |     | dB<br>dB      |

**动态精度** 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。采用内部基准， $V_{DD} = 3\text{V}$ ， $V_{DD} = V_{CC} = 3\text{V}$ 。

| 符号    | 参数         | 条件                                                                                             | 最小值 | 典型值 | 最大值 | 单位     |

|-------|------------|------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| SINAD | 信号与噪声加失真之比 | 100kHz 输入信号                                                                                    | ●   | 73  | 76  | dB     |

|       |            | 300kHz 输入信号                                                                                    |     | 76  | 76  | dB     |

|       |            | 100kHz 输入信号，外部 $V_{REF} = 3.3\text{V}$ ， $V_{DD} \geq 3.3\text{V}$                             |     | 79  | 79  | dB     |

|       |            | 300kHz 输入信号，外部 $V_{REF} = 3.3\text{V}$ ， $V_{DD} \geq 3.3\text{V}$                             |     | 79  | 79  | dB     |

| THD   | 总谐波失真      | 100kHz 首 5 个谐波                                                                                 | ●   | -80 | -90 | dB     |

|       |            | 300kHz 首 5 个谐波                                                                                 |     |     | -86 | dB     |

| SFDR  | 无寄生动态范围    | 100kHz 输入信号                                                                                    |     | 90  | 90  | dB     |

|       |            | 300kHz 输入信号                                                                                    |     | 86  | 86  | dB     |

| IMD   | 交调失真       | 0.625V <sub>P-P</sub> ，833kHz 信号输入 CH0+；0.625V <sub>P-P</sub> ，841kHz 信号输入 CH0-。双极模式。同样适用于其他通道 |     | -80 | -80 | dB     |

|       |            | 代码至代码转换噪声                                                                                      |     | 0.7 | 0.7 | LSBRMS |

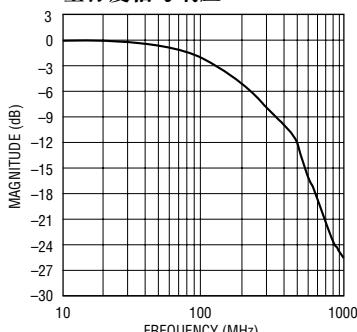

|       | 满功率带宽      | $V_{IN} = 2.5\text{V}_{P-P}$ ， $SD0 = 11585\text{LSB}_{P-P}$ (-3dBFS) (注 15)                   |     | 50  | 50  | MHz    |

|       |            | $S/(N + D) \geq 68\text{dB}$ ，双极差分输入                                                           |     | 5   | 5   | MHz    |

**内部基准特性**  $T_A = 25^\circ\text{C}$ 。 $V_{DD} = V_{CC} = 3\text{V}$ 。

| 参数               | 条件                                                               | 最小值 | 典型值 | 最大值 | 单位     |

|------------------|------------------------------------------------------------------|-----|-----|-----|--------|

| $V_{REF}$ 输出电压   | $I_{OUT} = 0$                                                    | 2.5 | 2.5 | 2.5 | V      |

| $V_{REF}$ 输出温度系数 |                                                                  | 15  | 15  | 15  | ppm/°C |

| $V_{REF}$ 电压调节   | $V_{DD} = 2.7\text{V}$ 至 $3.6\text{V}$ ， $V_{REF} = 2.5\text{V}$ | 600 | 600 | 600 | μV/V   |

| $V_{REF}$ 输出电阻   | 负载电流 = 0.5mA                                                     | 0.2 | 0.2 | 0.2 | Ω      |

| $V_{REF}$ 稳定时间   |                                                                  | 2   | 2   | 2   | ms     |

**数字输入和数字输出** 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。

$V_{DD} = V_{CC} = 3\text{V}$ 。

| 符号           | 参数                 | 条件                                                                                                     | 最小值 | 典型值  | 最大值 | 单位 |

|--------------|--------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|----|

| $V_{IH}$     | 高电平输入电压            | $V_{DD} = 3.3\text{V}$                                                                                 | ●   | 2.4  | 2.4 | V  |

| $V_{IL}$     | 低电平输入电压            | $V_{DD} = 2.7\text{V}$                                                                                 | ●   | 0.6  | 0.6 | V  |

| $I_{IN}$     | 数字输入电流             | $V_{IN} = 0\text{V}$ 至 $V_{DD}$                                                                        | ●   | ±10  | ±10 | μA |

| $C_{IN}$     | 数字输入电容             |                                                                                                        |     | 5    | 5   | pF |

| $V_{OH}$     | 高电平输出电压            | $V_{DD} = 3\text{V}$ ， $I_{OUT} = -200\text{μA}$                                                       | ●   | 2.5  | 2.9 | V  |

| $V_{OL}$     | 低电平输出电压            | $V_{DD} = 2.7\text{V}$ ， $I_{OUT} = 160\text{μA}$<br>$V_{DD} = 2.7\text{V}$ ， $I_{OUT} = 1.6\text{mA}$ | ●   | 0.05 | 0.4 | V  |

| $I_{OZ}$     | 高阻抗输出漏电流 $D_{OUT}$ | $V_{OUT} = 0\text{V}$ 和 $V_{DD}$                                                                       | ●   | ±10  | ±10 | μA |

| $C_{OZ}$     | 高阻抗输出电容 $D_{OUT}$  |                                                                                                        |     | 1    | 1   | pF |

| $I_{SOURCE}$ | 输出短路供电电流           | $V_{OUT} = 0\text{V}$ ， $V_{DD} = 3\text{V}$                                                           |     | 20   | 20  | mA |

| $I_{SINK}$   | 输出短路吸收电流           | $V_{OUT} = V_{DD} = 3\text{V}$                                                                         |     | 15   | 15  | mA |

**功率要求** 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。采用内部基准， $V_{DD} = V_{CC} = 3\text{V}$ 。

| 符号                | 参数   | 条件                                         | 最小值 | 典型值 | 最大值 | 单位            |

|-------------------|------|--------------------------------------------|-----|-----|-----|---------------|

| $V_{DD}, V_{CC}$  | 电源电压 |                                            | 2.7 | 3.6 |     | V             |

| $I_{DD} + I_{CC}$ | 电源电流 | 运行模式， $f_{SAMPLE} = 600\text{ksps}$        | ●   | 5   | 7   | mA            |

|                   |      | 打盹模式                                       |     | 1.1 | 1.9 | mA            |

|                   |      | 睡眠模式                                       |     | 2.0 | 15  | $\mu\text{A}$ |

| PD                | 功耗   | 具 SCK 的运行模式， $f_{SAMPLE} = 600\text{ksps}$ |     | 15  |     | mW            |

**定时特性** 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。 $V_{DD} = 3\text{V}$ 。

| 符号                | 参数                                                  | 条件           | 最小值 | 典型值 | 最大值   | 单位      |

|-------------------|-----------------------------------------------------|--------------|-----|-----|-------|---------|

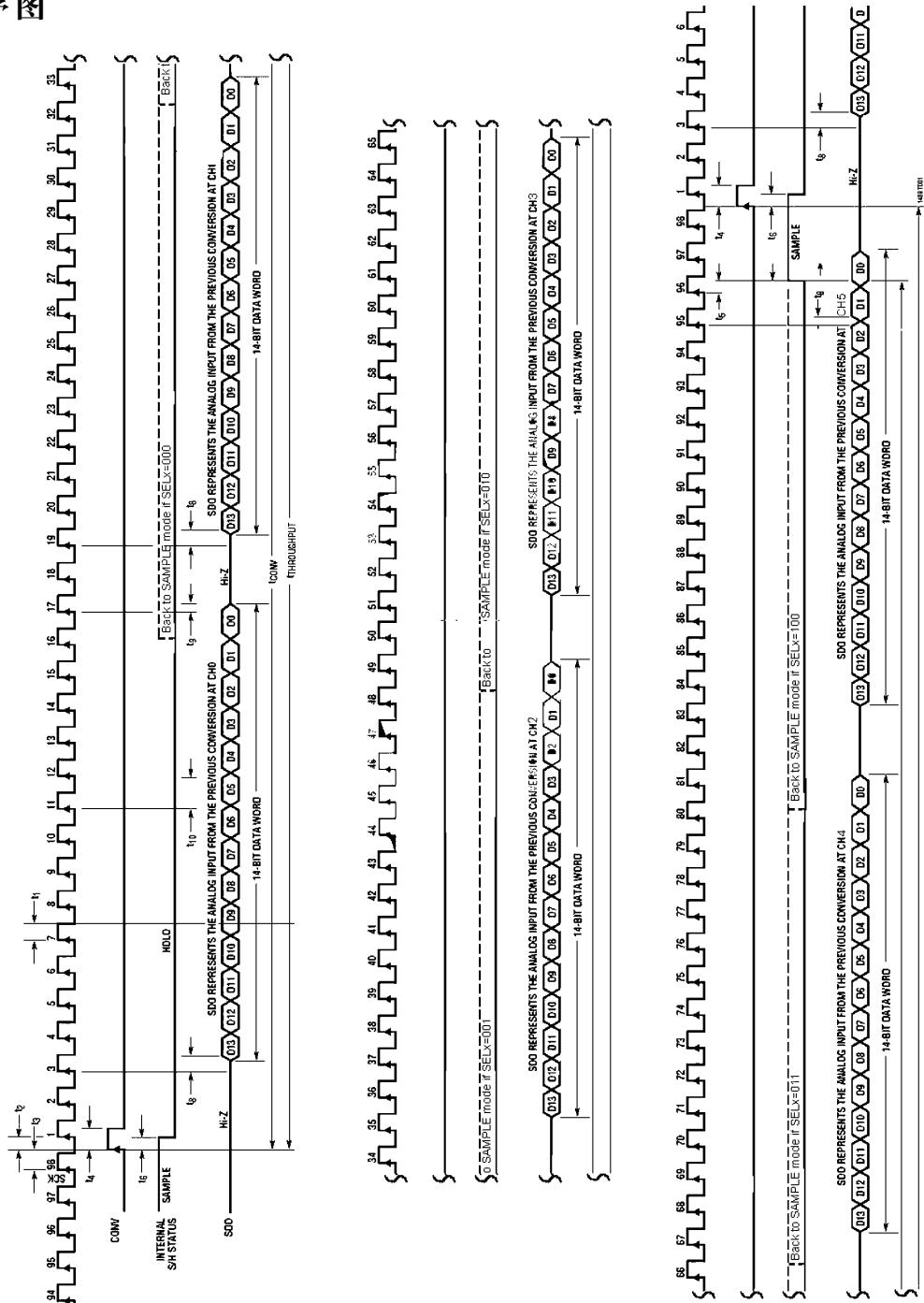

| $f_{SAMPLE(MAX)}$ | 每个通道的最大采样频率<br>(转换速率)                               |              | ●   | 100 |       | kHz     |

| $t_{THROUGHPUT}$  | 最小采样频率(转换 + 采集周期)                                   |              | ●   | 667 |       | ns      |

| $t_{SCK}$         | 时钟周期                                                | (注 16)       | ●   | 100 | 10000 | ns      |

| $t_{CONV}$        | 转换时间                                                | (注 6, 17)    |     | 96  |       | SCLK 周期 |

| $t_1$             | 最小正或负 SCLK 脉冲宽度                                     | (注 6)        |     | 2   |       | ns      |

| $t_2$             | CONV 至 SCK 建立时间                                     | (注 6, 10)    |     | 3   | 10000 | ns      |

| $t_3$             | SCK 早于 CONV                                         | (注 6)        |     | 0   |       | ns      |

| $t_4$             | 最小正或负 CONV 脉冲宽度                                     | (注 6)        |     | 4   |       | ns      |

| $t_5$             | SCK 至采样模式                                           | (注 6)        |     | 4   |       | ns      |

| $t_6$             | CONV 至保持模式                                          | (注 6, 11)    |     | 1.2 |       | ns      |

| $t_7$             | 第 96 个 SCK $\uparrow$ 至 CONV $\uparrow$ 的间隔(影响采集周期) | (注 6, 7, 13) |     | 45  |       | ns      |

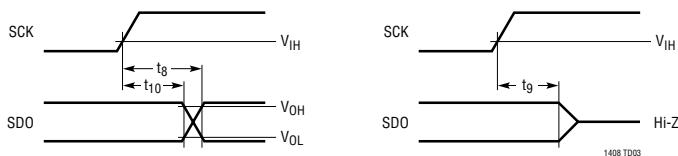

| $t_8$             | 从 SCK 至有效位 0 ~ 11 的最小延迟                             | (注 6, 12)    |     | 8   |       | ns      |

| $t_9$             | SCK 至 SDO 上的高阻抗状态                                   | (注 6, 12)    |     | 6   |       | ns      |

| $t_{10}$          | 前面的 SDO 位在 SCK 之后保持有效                               | (注 6, 12)    |     | 2   |       | ns      |

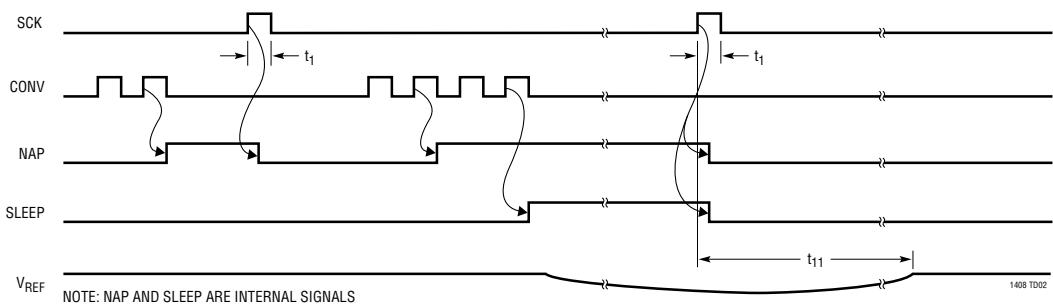

| $t_{11}$          | 睡眠至唤醒转换之后的 $V_{REF}$ 稳定时间                           | (注 6, 14)    |     | 2   |       | ms      |

**注 1：**高于“绝对最大额定值”部分所列数值的应力有可能对器件造成永久性的损害。在任何绝对最大额定值条件下暴露的时间过长都有可能影响器件的可靠性和使用寿命。

**注 2：**所有电压值均以地 (GND) 为基准。

**注 3：**当这些引脚的电平被拉至 GND 以下或  $V_{DD}$  以上时，它们将被内部二极管所箝位。该产品能够在低于 GND 或高于  $V_{DD}$  的电压条件下处理 100mA 以上的输入电流，而不会引发锁断。

**注 4：**失调和范围规格适用于一个单端  $\text{CH}0^+ \sim \text{CH}0^+$  输入 ( $\text{CH}0^- \sim \text{CH}5^-$  引脚接地并采用 2.5V 内部基准)。

**注 5：**积分线性度利用一个 2.55V 外部基准来测试，并被定义为一个代码相对一根穿越转移函数曲线实际端点的直线的偏离程度。该偏离是以量化频带的中心为起点进行测量的。仅对  $\text{CH}0$  引脚进行线性度测试。

**注 6：**由设计提供保证，未经测试。

**注 7：**推荐的工作条件。

**注 8：**模拟输入范围是针对  $\text{CH}x^+$  和  $\text{CH}x^-$  之间的电压差来定义的， $x = 0 \sim 5$ 。

**注 9：** $\text{CH}x^+$  和  $\text{CH}x^-$  上的绝对电压必须在该范围之内。

**注 10：**如果允许小于 3ns 的建立时间，则输出数据将在一个时钟周期之后出现。当以额定速度来运行时钟时，CONV 最好在 SCK 之前半个时钟周期上升。

**注 11：**与孔径延迟不同。孔径延迟 (1ns) 是通过采样及保持电路的 2.2ns 延迟与 CONV 至 HOLD 模式的 1.2ns 延迟之差。

**注 12：**SCK 的上升沿保证与输出至锁存器中的数据同步。

**注 13：**用于采集输入信号的时段由第 96 个上升时钟来起动，并由 CONV 的上升沿来终止。

**注 14：**内部基准在被从睡眠模式唤醒之后 2ms 实现稳定(利用 SCK 引脚上的一个或多个周期和一个  $10\mu\text{F}$  的容性负载)。

**注 15：**满功率带宽是指输出代码摆幅下降了 3dB 时的频率(当采用一个 2.5V<sub>P-P</sub> 输入正弦波时)。

**注 16：**最大时钟周期确保了转换操作期间的模拟性能。输出数据可利用一个任意长的时钟周期来读取。

**注 17：**对于每个被使能的通道，其转换过程需要 16 个时钟周期，因此，全部 6 个通道的转换过程将需要多达 96 个时钟周期。

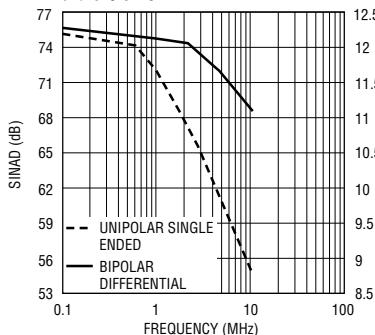

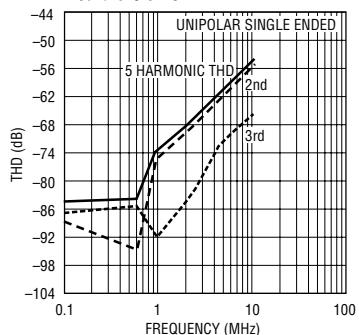

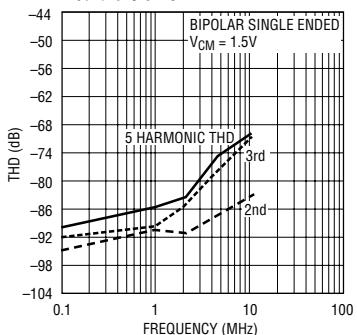

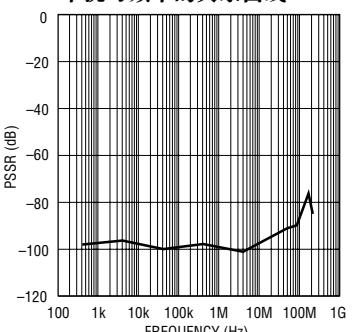

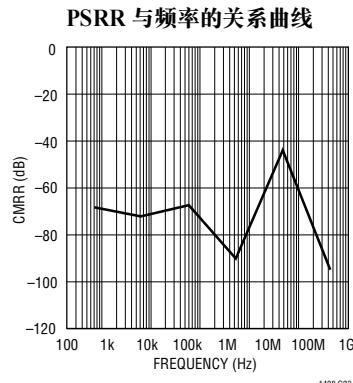

## 典型性能特征 $V_{DD} = 3V$ , $T_A = 25^\circ C$

SINAD, ENOB 与频率的关系曲线

1408 G01

二阶和三阶 THD 与输入频率的关系曲线

1408 G02

二阶和三阶 THD 与输入频率的关系曲线

1408 G03

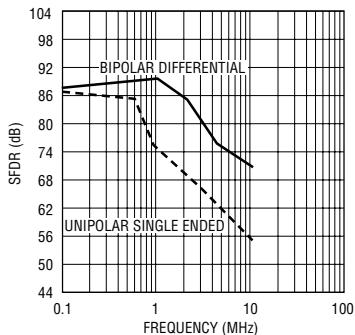

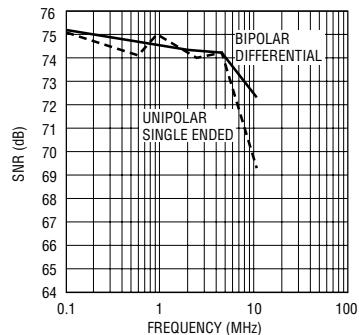

SFDR 与输入频率的关系曲线

1408 G04

SNR 与输入频率的关系曲线

1408 G05

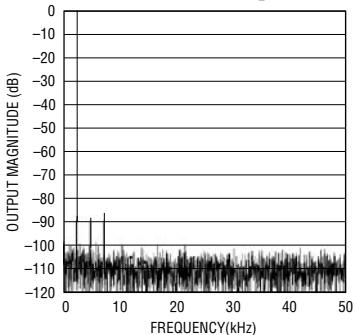

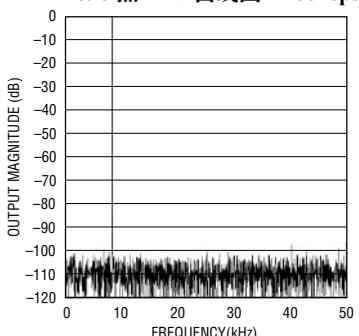

98kHz 单极正弦波 4096 点 FFT 曲线图, 100ksps

1408 G06

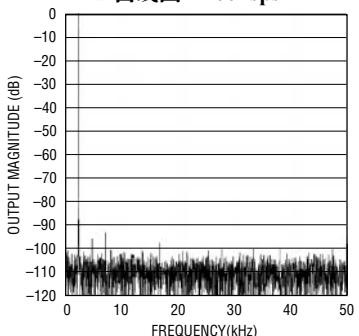

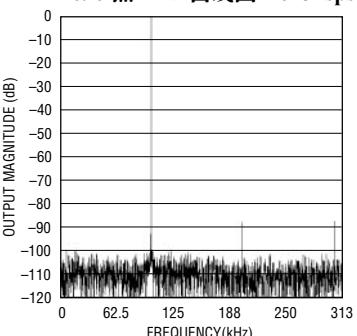

98kHz 双极正弦波 4096 点 FFT 曲线图, 100ksps

1408 G07

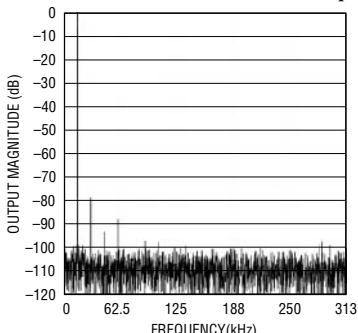

591kHz 双极差分正弦波 4096 点 FFT 曲线图, 100ksps

1408 G08

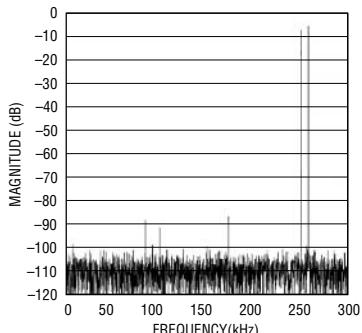

101kHz 单极单端正弦波 4096 点 FFT 曲线图, 625ksps

1408 G09

## 典型性能特征 $V_{DD} = 3V$ , $T_A = 25^\circ C$

610kHz 单极单端输入正弦波

4096 点 FFT 曲线图, 625ksps

1408 G10

CH0<sup>+</sup> 的输入信号频率为

833kHz, CH0<sup>-</sup> 的输入信号

频率为 841kHz, 588ksps 双极

模式 4096 点 FFT

1408 G11

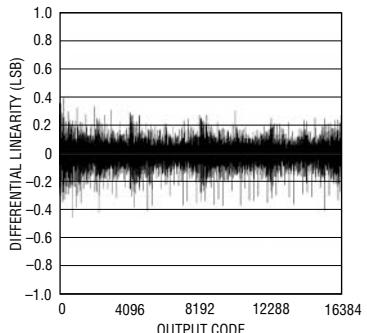

采用 2.5V 内部基准时的 CH0

微分线性度, 单极模式

1408 G12

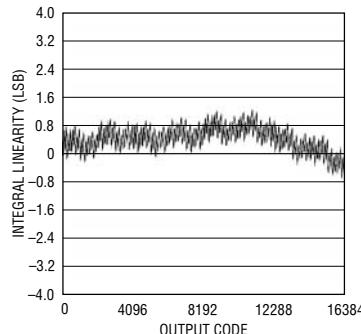

采用 2.5V 内部基准时的 CH0

积分线性端点拟合, 单极模式

1408 G13

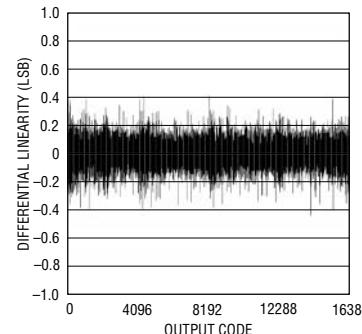

采用 2.5V 内部基准时的

CH0 微分线性, 双极模式中

的差分输入

1408 G14

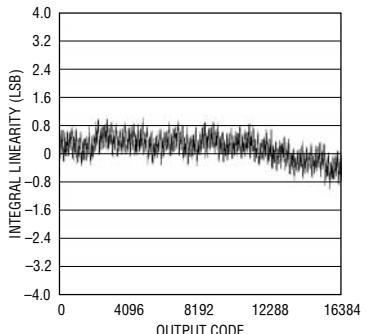

积分线性端点拟合

1408 G15

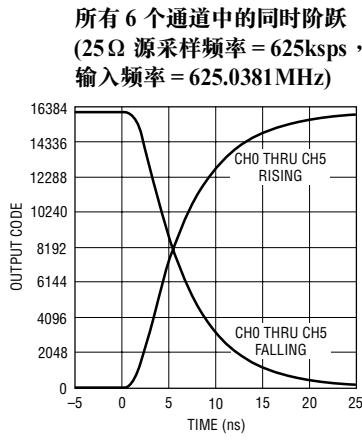

全标度信号响应

1408 G16

CMRR 与频率的关系曲线

1408 G21

串扰与频率的关系曲线

1408fa

## 典型性能特征 $V_{DD} = 3V$ , $T_A = 25^\circ C$

## 引脚功能

**SDO (引脚 1)**：三态串行数据输出。每组 (6 个) 输出数据字代表前一个转换操作始端的 6 个模拟输入通道。用于 CH0 的数据最先输出，而用于 CH5 的数据最后输出。每个数据字首先输出 MSB。

**OGND (引脚 2)**：用于 SDO 电流的接地回线。该衬垫必须始终处于接地平面电位的 300mV 以内。

**OV<sub>DD</sub> (引脚 3)**：用于 SDO 引脚的电源。OV<sub>DD</sub> 引脚电压高出 V<sub>DD</sub> 引脚电压的幅度一定不得超过 300mV，并可被拉至一个较低的电压，以与低电压逻辑器件系列相连。SDO 引脚上的无载高态处于 OV<sub>DD</sub> 的电位。

**CH0<sup>+</sup> (引脚 4)**：同相通道 0。CH0<sup>+</sup> 相对于 CH0<sup>-</sup> 进行全差分操作，并具有一个 0V 至 2.5V 或  $\pm 1.25V$  的差分摆幅和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH0<sup>-</sup> (引脚 5)**：反相通道 0。CH0<sup>-</sup> 相对于 CH0<sup>+</sup> 进行全差分操作，并具有一个 -2.5V 至 0V 或  $\pm 1.25V$  的差分摆幅和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**GND (引脚 6、9、12、13、16、19)**：模拟地。这些接地引脚必须直接连接至位于器件下方的整体接地平面。模拟信号电流流过这些接线。

**CH1<sup>+</sup> (引脚 7)**：同相通道 1。CH1<sup>+</sup> 相对于 CH1<sup>-</sup> 进行全差分操作，并具有一个 0V 至 2.5V 或  $\pm 1.25V$  的差分摆幅和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH1<sup>-</sup> (引脚 8)**：反相通道 1。CH1<sup>-</sup> 相对于 CH1<sup>+</sup> 进行全差分操作，并具有一个 -2.5V 至 0V 或  $\pm 1.25V$  的差分摆幅和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH2<sup>+</sup> (引脚 10)**：同相通道 2。CH2<sup>+</sup> 相对于 CH2<sup>-</sup> 进行全差分操作，并具有一个 0V 至 2.5V 或  $\pm 1.25V$  的差分摆幅和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH2<sup>-</sup> (引脚 11)**：反相通道 2。CH2<sup>-</sup> 相对于 CH2<sup>+</sup> 进行全差分操作，并具有一个 -2.5V 至 0V 或  $\pm 1.25V$  的差分摆幅和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH3<sup>+</sup> (引脚 14)**：同相通道 3。CH3<sup>+</sup> 相对于 CH3<sup>-</sup> 进行完全差分操作，并具有一个 0V 至 2.5V 或  $\pm 1.25V$  的差分摆幅，和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

## 引脚功能

**CH3<sup>-</sup> (引脚 15) :** 反相通道 3。CH3<sup>-</sup> 相对于 CH3<sup>+</sup> 进行完全差分操作，并具有一个 -2.5V 至 0V 或  $\pm 1.25V$  的差分摆幅，和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH4<sup>+</sup> (引脚 17) :** 同相通道 4。CH4<sup>+</sup> 相对于 CH4<sup>-</sup> 进行完全差分操作，并具有一个 0V 至 2.5V 或  $\pm 1.25V$  的差分摆幅，和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH4<sup>-</sup> (引脚 18) :** 反相通道 4。CH4<sup>-</sup> 相对于 CH4<sup>+</sup> 进行完全差分操作，并具有一个 -2.5V 至 0V 或  $\pm 1.25V$  的差分摆幅，和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH5<sup>+</sup> (引脚 20) :** 同相通道 5。CH5<sup>+</sup> 相对于 CH5<sup>-</sup> 进行完全差分操作，并具有一个 0V 至 2.5V 或  $\pm 1.25V$  的差分摆幅，和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**CH5<sup>-</sup> (引脚 21) :** 反相通道 5。CH5<sup>-</sup> 相对于 CH5<sup>+</sup> 进行完全差分操作，并具有一个 -2.5V 至 0V 或  $\pm 1.25V$  的差分摆幅，和一个 0V 至 V<sub>DD</sub> 的绝对输入范围。

**GND (引脚 22) :** 用于基准的模拟地。必须把模拟地直接连接至位于器件下方的连续接地平面。模拟信号电流流过该连接线。10 $\mu$ F 的基准旁路电容器应回接至该衬垫。

**V<sub>REF</sub> (引脚 23) :** 2.5V 内部基准。通过一个 10 $\mu$ F 陶瓷电容器(或与 0.1 $\mu$ F 陶瓷电容器并联的 10 $\mu$ F 钽电容器)将该引脚旁路至 GND 和一个连续的模拟接地平面。可由一个位于 2.55% 和 V<sub>DD</sub>、V<sub>CC</sub> 之间的外部基准电压对该引脚进行过驱动。

**V<sub>CC</sub> (引脚 24) :** 正模拟电源。该引脚向模拟电路部分提供 3V 电压。通过一个与 0.1 $\mu$ F 陶瓷电容器并联的 10 $\mu$ F 陶瓷电容器(或 10 $\mu$ F 钽电容器)将该引脚旁路至整体模拟接地平面。应谨慎地把 0.1 $\mu$ F 旁路电容器布设于尽可能靠近引脚 24 的地方。引脚 24 必须连接至引脚 25。

**V<sub>DD</sub> (引脚 25) :** 3V 正数字电源。该引脚向逻辑电路部分提供 3V 电压。通过一个 10 $\mu$ F 陶瓷电容器(或与

0.1 $\mu$ F 陶瓷电容器并联的 10 $\mu$ F 钽电容器)将该引脚旁路至 DGND 引脚和整体模拟接地平面。请牢记：内部数字输出信号电流将流过该引脚。应谨慎地把 0.1 $\mu$ F 旁路电容器布设于尽可能靠近引脚 25 的地方。引脚 25 必须连接至引脚 24。

**SEL2 (引脚 26) :** 负责控制被转换通道数目的最高有效位。与 SEL1 和 SEL0 引脚结合起来使用，000 仅选择把第一个通道 (CH0) 用于转换。增加 SELx 将选择用于转换的附加通道 (CH0 ~ CH5)。101、110 或 111 选择把全部 6 个通道用于转换。在转换期间以及用于读出数据的后续转换期间，必须把该引脚保持在一个固定状态。

**SEL1 (引脚 27) :** 负责控制被转换通道数目的中等有效位。与 SEL0 和 SEL2 引脚结合起来使用，000 仅选择把第一个通道 (CH0) 用于转换。增加 SELx 将选择用于转换的附加通道。101、110 或 111 选择把全部 6 个通道 (CH0 ~ CH5) 用于转换。在转换期间以及用于读出数据的后续转换期间，必须把该引脚保持在一个固定状态。

**SEL0 (引脚 28) :** 负责控制被转换通道数目的最低有效位。与 SEL1 和 SEL2 引脚结合起来使用，000 仅选择把第一个通道 (CH0) 用于转换。增加 SELx 将选择用于转换的附加通道。101、110 或 111 选择把全部 6 个通道 (CH0 ~ CH5) 用于转换。在转换期间以及用于读出数据的后续转换期间，必须把该引脚保持在一个固定状态。

**BIP (引脚 29) :** 双极/单极模式。当 BIP 引脚为低电平时，输入差分范围为 0V 至 2.5V；当 BIP 引脚为高电平时，输入差分范围为  $\pm 1.25V$ 。在转换期间以及用于读出数据的后续转换期间，必须把该引脚保持在一个固定状态。当在转换操作之间改变 BIP 时，在起动下一个转换操作之前必须提供满采集时间。对于双极模式，输出数据采用二进制补码格式；而对于单极模式，则采用直接二进制格式。

## 引脚功能

**CONV (引脚 30)**：转换起动。保存 6 个模拟输入信号，并在上升沿上起动转换。SCK 处于固定高态或固定低态的两个脉冲将起动打盹模式。SCK 处于固定高态或固定低态的 4 个或更多的脉冲将起动睡眠模式。

**DGND (引脚 31)**：数字地。该接地引脚必须直接连接至整体接地平面。数字输入信号电流流过该引脚。

**SCK (引脚 32)**：外部时钟输入。推进转换操作过程并在上升沿上对 SD0 (引脚 1) 上的输出数据进行排序。一个或多个脉冲从节能的睡眠或打盹模式中被唤醒。每个由 SELx (引脚 26、27、28) 启动的通道需要 16 个时钟周期，因而完成全部 6 个通道的转换和数据读出总共需要多达 96 个时钟周期。

**裸露衬垫 (引脚 33)**：GND。必须直接连接至整体接地平面。

## 方框图

## 时序图

LTC1408 时序图

## 时序图

打盹模式和睡眠模式波形

SCK 至 SDO 延迟

## 应用信息

### 选择被转换通道的数目 (SEL2、SEL1、SEL0)

这三个控制引脚负责选择被转换通道的数目。000 仅选择把第一个通道 (CH0) 用于转换。增加 SELx 将选择用于转换的附加通道 (多达 6 个)。101、110 或 111 选择把全部 6 个通道用于转换。在转换期间以及用于读出数据的后续转换期间，必须把这些引脚保持在一个固定状态。当在转换操作之间改变模式时，应牢记：一个特定通道的输出数据将保持不变，直到该通道被再次转换之后为止。例如：利用  $SELx = 011$  来转换一个 4 通道序列 (CH0、CH1、CH2、CH3)，那么，在这些通道被转换之后，把  $SELx$  变为 001，以仅对 CH0 和 CH1 进行转换。见表 1。在第一组 (两个) 通道的转换期间，您将能够从作为前一组 (4 个) 通道的一部分而被转换的相同的两个通道读出数据。随后，您可以对 4 个或更多的通道进行转换，以对在第一组 (4 个) 通道中转换的未读 CH2 和 CH3 数据进行回读。这些引脚常常是硬连线的，旨在针对某一特定的应用来使能数目正确的通道。

### 双极/单极模式

每个  $CH_x$  输入差分对的输入电压范围均为单极 0V 至 2.5V (当 BIP 引脚为低电平时) 和双极  $\pm 1.25V$  (当 BIP 引脚为高电平时)。在转换期间以及用于读出数据的后续转换期间，必须把该引脚保持在一个固

定状态。当在转换操作之间改变 BIP 时，在起动下一个转换操作之前必须提供满采集时间。在把模式从双极改为单极或从单极改为双极之后，您仍能以新的模式对第一组通道进行读操作，采取的方法是使 MSB 反相，以便利用这些通道先前进行转换的模式来读出其数据。

### 驱动模拟输入

LTC1408 的差分模拟输入易于驱动。输入可被差分驱动，或者被作为一个单端输入 (即： $CH0^-$  输入接地) 来驱动。所有 6 个差分模拟输入对 ( $CH0^+$  和  $CH0^-$ 、 $CH1^+$  和  $CH1^-$ 、 $CH2^+$  和  $CH2^-$ 、 $CH3^+$  和  $CH3^-$ 、 $CH4^+$  和  $CH4^-$  以及  $CH5^+$  和  $CH5^-$ ) 的全部 12 个模拟输入在同一瞬间进行采样。采样及保持电路的共模抑制功能将减少每对输入的两个输入所共有的任何无用信号。当在转换结束时对采样及保持电容进行充电时，输入仅吸收一个小电流尖峰。在转换操作期间，模拟输入仅吸收一个很小的漏电流。如果驱动电路的源阻抗很低，则可直接驱动 LTC1408 输入。当源阻抗增加时，采集时间也将增加。为了在高源阻抗条件下获得最小的采集时间，必须采用一个缓冲放大器。主要的要求是：驱动模拟输入的放大器必须在下一个转换操作开始之前的一个小电流尖峰之后实现稳定 (在满吞吐速率条件下，可供实现稳定之用的时间必须至少为 39ns)。另外，在选择输入放大器时，还需紧记由放大器所导致的噪声和失真量的增加。

表 1：转换顺序控制

(“acquire” 代表所有通道的同时采样； $CH_x$  代表通道的转换)

| SEL2 | SEL1 | SEL0 | 通道采集和转换顺序                                                                       |

|------|------|------|---------------------------------------------------------------------------------|

| 0    | 0    | 1    | acquire, CH0, acquire, CH0...                                                   |

| 0    | 0    | 1    | acquire, CH0, CH1, acquire, CH0, CH1...                                         |

| 0    | 1    | 0    | acquire, CH0, CH1, CH2, acquire, CH0, CH1, CH2...                               |

| 0    | 1    | 1    | acquire, CH0, CH1, CH2, CH3, acquire, CH0, CH1, CH2, CH3...                     |

| 1    | 0    | 0    | acquire, CH0, CH1, CH2, CH3, CH4, acquire, CH0, CH1, CH2, CH3, CH4...           |

| 1    | 0    | 1    | acquire, CH0, CH1, CH2, CH3, CH4, CH5, acquire, CH0, CH1, CH2, CH3, CH4, CH5... |

| 1    | 1    | 0    | acquire, CH0, CH1, CH2, CH3, CH4, CH5, acquire, CH0, CH1, CH2, CH3, CH4, CH5... |

| 1    | 1    | 1    | acquire, CH0, CH1, CH2, CH3, CH4, CH5, acquire, CH0, CH1, CH2, CH3, CH4, CH5... |

## 应用信息

### 选择一个输入放大器

如果把几项要求考虑在内，则选择一个输入放大器是很容易的。首先，为了限制放大器所承受的电压尖峰幅度对采样电容器进行充电，应选择一个在闭环带宽频率上具有低输出阻抗( $<100\Omega$ )的放大器。例如，如果一个放大器的工作增益为1并具有一个50MHz的单位增益带宽，则50MHz频率条件下的输出阻抗必须小于 $100\Omega$ 。第二项要求是闭环带宽必须大于40MHz，以确保在满吞吐速率条件下获得合适的小信号稳定时间。如果采用的是低速运算放大器，则可通过增加转换操作之间的时间来为实现稳定提供更多的时间。用于驱动LTC1408的运算放大器的最佳选择取决于应用。应用一般分为两类，即：AC应用(这里，动态规格最为关键)和时域应用(这里，DC准确度和稳定时间最为重要)。下面列出了适合于驱动LTC1408的运算放大器概要。(更加详细的信息可查阅凌力尔特公司的数据手册，也可登录[www.linear.com.cn](http://www.linear.com.cn)网站查询。)

LinearView是凌力尔特公司的商标。

**LTC1566-1**：低噪声2.3MHz连续时间低通滤波器。

**LT<sup>®</sup>1630**：双通道30MHz轨至轨电压FB放大器。2.7V至 $\pm 15$ V电源。具有非常高的 $A_{VOL}$ 、 $500\mu V$ 失调，对于一个4V摆幅，至0.5LSB的稳定时间为520ns。当 $A_V=1$ 、 $1k\Omega$ 负载的供电电压为 $2V_{P-P}$ 、 $V_S=5V$ 时，THD和噪声为-93dB(至40kHz)和1LSB以下(至320kHz)，从而使得该器件成为那些需要轨至轨性能的AC应用(至1/3奈奎斯特频率)的理想选择。可提供四通道版本，即LT1631。

**LT1632**：双通道45MHz轨至轨电压FB放大器。2.7V至 $\pm 15$ V电源。具有非常高的 $A_{VOL}$ 、 $1.5mV$ 失调，对于一个4V摆幅，至0.5LSB的稳定时间为400ns。它适合于采用单5V电源的应用。当 $A_V=1$ 、 $1k\Omega$ 负载的供电电压为 $2V_{P-P}$ 、 $V_S=5V$ 时，THD和噪声为-93dB(至40kHz)和1LSB以下(至800kHz)，从而使得该器件成为那些需要轨至轨性能的AC应用的理想选择。可提供四通道版本，即LT1633。

**LT1801**：80MHzGBWP，-75dBc(在500kHz)，每个放大器的供电电流为2mA， $8.5nV/\sqrt{Hz}$ 。

**LT1806/LT1807**：325MHzGBWP，-80dBc失真(在5MHz)，稳定的单位增益，轨至轨输入和输出，每个放大器的供电电流为10mA， $3.5nV/\sqrt{Hz}$ 。

**LT1810**：180MHzGBWP，-90dBc失真(在5MHz)，稳定的单位增益，轨至轨输入和输出，每个放大器的供电电流为15mA， $16nV/\sqrt{Hz}$ 。

**LT1818/LT1819**：400MHz， $2500V/\mu s$ ，9mA，单通道/双通道电压模式运算放大器。

**LT6200**：165MHzGBWP，-85dBc失真(在1MHz)，稳定的单位增益，轨至轨输入和输出，每个放大器的供电电流为15mA， $0.95nV/\sqrt{Hz}$ 。

**LT6203**：100MHzGBWP，-80dBc失真(在1MHz)，稳定的单位增益，轨至轨输入和输出，每个放大器的供电电流为3mA， $1.9nV/\sqrt{Hz}$ 。

**LT6600**：具有10MHz截止频率的放大器/滤波器差分输入/输出。

## 应用信息

### 输入滤波和源阻抗

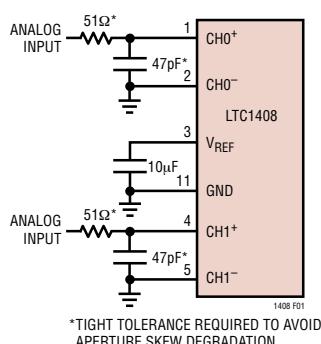

必须对输入放大器和其他电路的噪声和失真加以考虑，因为它们将使 LTC1408 的噪声和失真有所增加。采样及保持电路的小信号带宽为 50MHz。存在于模拟输入端上的所有噪声或失真分量将在这整个带宽上相加。应在模拟输入之前对噪声输入电路进行滤波处理，以最大限度地降低噪声。对于许多应用而言，采用一个简单的单极点 RC 滤波器便足够了。例如，图 1 示出了用于把净输入带宽限制于 30MHz 的一个 47pF 电容器(连接在  $\text{CH0}^+$  引脚和地之间)和一个  $51\Omega$  源电阻器。该 47pF 电容器还起到了输入采样及保持电路的电荷储存器的作用，并将 ADC 输入与对采样干扰敏感的电路隔离开来。应采用高质量的电容器和电阻器，因为这些元件会使失真增加。NPO 和银云母型介质电容器具有卓越的线性。炭质表面贴装型电阻器会因为自发热以及焊接过程中可能受到的损害而产生失真。这两个问题对金属膜表面贴装型电阻器的影响都要小得多。当高幅度无用信号的频率靠近所需的信号频率时，应采用一个多极点滤波器。

高外部源电阻、再加上  $13\text{pF}$  的输入电容，将降低额定的 50MHz 输入带宽，并使采集时间增加至 39ns 以上。

图 1：RC 输入滤波器

### 输入范围

可利用一个单电源对 LTC1408 的模拟输入进行全差分驱动。任一个输入均可摆动至高达  $\text{V}_{\text{CC}}$ ，前提是差分摆幅不大于 2.5V 而 BIP(引脚 29) 为低电平或  $\pm 1.25\text{V}$  而 BIP(引脚 29) 为高电平。0V 至 2.5V 范围还非常适合于单端输入和单电源应用。输入的共模范围从地扩展至电源电压  $\text{V}_{\text{CC}}$ 。如果任何输入对上的  $\text{CH}^+$  和  $\text{CH}^-$  之电压差超过 2.5V(单极)或 1.25V(双极)，则输出代码将固定于正全标度值，而如果该电压差变至 0V(单极)或  $-1.25\text{V}$ (双极)以下，则输出代码将固定于负全标度值。

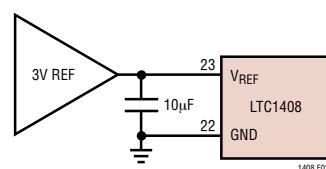

### 内部基准

LTC1408 具有一个在出厂时被修整于 2.5V 附近(以获得一个精确的 2.5V 输入跨度)的片内、温度补偿型带隙基准。必须采用一个接地的电容器对基准误差放大器输出  $\text{V}_{\text{REF}}$ (引脚 23) 进行旁路。基准放大器可在采用  $1\mu\text{F}$  或更大数值电容器的情况下保持稳定。为了获得最佳的噪声性能，建议将一个  $10\mu\text{F}$  陶瓷电容器(或  $10\mu\text{F}$  钽电容器)与一个  $0.1\mu\text{F}$  陶瓷电容器相并联。如图 2 所示，可利用一个外部基准对  $\text{V}_{\text{REF}}$  引脚进行过驱动。外部基准的电压必须高于内部基准的漏极开路 P 沟道输出的 2.5V。外部基准的推荐范围为 2.55V 至  $\text{V}_{\text{DD}}$ 。在转换操作期间，一个 2.55V 的外部基准将承受一个 0.75mA 的 DC 静态负载以及转换操作期间高达 3mA 的工作负载。

图 2：外部基准

## 应用信息

### 输入跨度与基准电压的关系

差分输入范围具有一个单极电压跨度，该跨度与基准缓冲器输出  $V_{REF}$  (引脚 23) 上的电压和接地点上的电压之差相等。当采用内部基准时，ADC 的差分输入范围为 0V 至 2.5V。内部 ADC 以这两个节点为基准。当采用一个外部基准时，这种关系同样适用。

### 差分输入

ADC 将始终对  $CH^+ - CH^-$  之电压差进行转换，而不受任何输入对上的共模电压的影响。共模抑制上举在高频上 (见图 3)。唯一的要求是两个输入均不得走至地电位以下或超过  $V_{DD}$ 。

图 3 : CMRR 与频率的关系曲线

积分非线性误差 (INL) 和微分非线性误差 (DNL) 与共模电压的相关度很小。然而，失调误差将发生变化。DC CMRR 通常优于 -90dB。

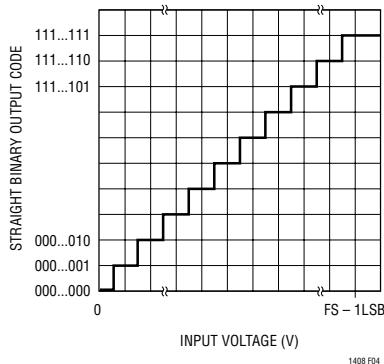

图 4 示出了 LTC1408 在单极模式 (BIP 引脚 = 低电平) 中的理想输入/输出特性。代码转换出现于连续整数 LSB 值的中间 (即 : 0.5LSB、1.5LSB、2.5LSB、FS - 1.5LSB)。输出代码为直接二进制，对于

LTC1408 而言，1LSB =  $2.5V/16384 = 153\mu V$ 。

LTC1408 具有 0.7LSB RMS 的高斯白噪声。

图 4 : LTC1408 在单极模式中的传输特性

(BIP 引脚 = 低电平)

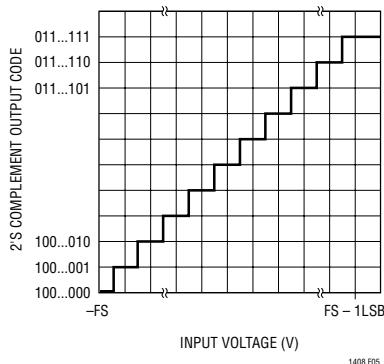

图 5 示出了 LTC1408 在双极模式 (BIP 引脚 = 高电平) 中的理想输入 / 输出特性。代码转换出现于连续整数 LSB 值的中间 (即 : 0.5LSB、1.5LSB、2.5LSB、FS - 1.5LSB)。输出代码为二进制补码，对于 LTC1408 而言，1LSB =  $2.5V/16384 = 153\mu V$ 。LTC1408 具有 0.7LSB RMS 的高斯白噪声。

图 5 : LTC1408 在双极模式中的传输特性

(BIP 引脚 = 高电平)

## 应用信息

### 断电模式

上电时，LTC1408 被初始化为运行状态，并随时可以进行转换操作。打盹和睡眠模式波形示出了 LTC1408 的断电模式。SCK 和 CONV 输入负责控制断电模式(见“时序图”)。CONV 上的两个上升沿(在 SCK 上没有任何的插入上升沿)将 LTC1408 置于打盹模式，而且，功率消耗从 15mW 降至 3.3mW。在打盹模式中，内部基准仍然处于受电状态。SCK 上的一个或多个上升沿可唤醒 LTC1408(以使之非常迅速地进入运行状态)，而且，CONV 能够在一个时钟周期之内起动一个准确的转换。CONV 上的 4 个上升沿(在 SCK 上没有任何的插入上升沿)将 LTC1408 置于睡眠模式，而且，功率消耗从 15mW 降至 10 $\mu$ W。SCK 上的一个或多个上升沿可唤醒 LTC1408(以使之进入运作状态)。当采用一个 10 $\mu$ F 负载时，内部基准( $V_{REF}$ )将需要 2ms 的时间来实现转换和稳定。如果睡眠模式的使用频度较高，则输出数据的准确度将有所下降。请注意，对于较低的转换速率，可采用打盹或睡眠模式来大幅度地降低功耗。

### 数字接口

LTC1408 具有一个三线式 SPI(串行外设接口)接口。SCK 和 CONV 输入及 SDO 输出实现了该接口。如果逻辑电源摆幅不超过  $V_{DD}$ ，则 SCK 和 CONV 输入将接受 3V 逻辑电源摆幅，并与 TTL 相兼容。三个串行端口信号的详细描述如下：

#### 转换起动输入 (CONV)

CONV 的上升沿起动一个转换，但是，CONV 上的后续上升沿将被 LTC1408 忽略，直到后面的 96 个 SCK 上升沿出现为止。CONV 的占空比可随意选择，以被用作处理器串行端口的帧同步信号。生成 CONV 的一种简单的方法是：产生一个宽度为 1SCK 的脉冲信号(用于驱动 LTC1408)，然后对该信号进行缓冲(以驱动处理器串行端口的帧同步输入)。一个上佳的惯例是：首先驱动 LTC1408 的 CONV 输入，以消除采样至保持转换(由 CONV 在转换操作的始端所触发)期间的数字噪声干扰。另一种良好的习惯做法是：使 CONV 信号的低电平部分的宽度大于 15ns，以避免刚好在采样及保持电路在 CONV 的上升沿进入保持模式之前把干扰引入 ADC 的前端。

## 应用信息

### 最大限度地减小 CONV 输入上的抖动

在对高于 100kHz 的高幅度正弦波进行采样的高速应用中，CONV 信号必须具有尽可能小的抖动 (10ps 或更小)。一个共用晶体时钟模块的方波输出常常能够轻松地满足该要求。难题是如何在不遭受来自系统中其他数字电路的抖动干扰的情况下从该晶体时钟生成一个 CONV 信号。位于从该晶体时钟至 CONV 输入的信号通路中的时钟分频器和任何逻辑门均不得与系统的其他部分共用同一个集成电路。应首先驱动 SCK 和 CONV 输入，并采用数字缓冲器来驱动串行端口接口。还需注意，DSP 中的主时钟有可能已经被抖动所破坏，即使它直接取自 DSP 晶体也于事无补。高速处理器时钟的另一个问题是它们经常采用低成本、低速晶体 (即：10MHz) 来生成一个快速 (但具有抖动的) 锁相环系统时钟 (即：40MHz)。这些由 PLL 生成的高速时钟中的抖动可达几纳秒 (ns)。请注意，如果您选择使用由 DSP 端口所生成的帧同步信号，则该信号将具有与 DSP 的主时钟相同的抖动。

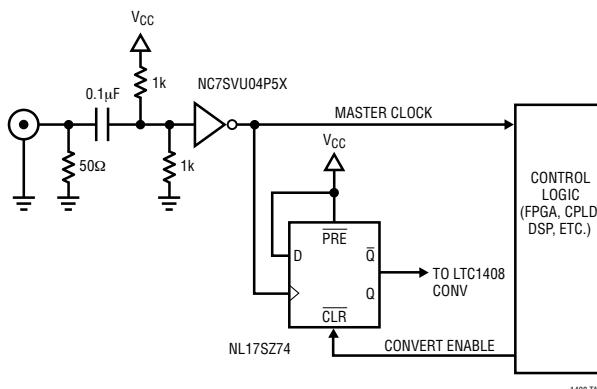

第 20 页上的典型应用插图示出了一种用于对来自一个 RF 信号发生器或其他低抖动信号源的输出进行电平移位和方波整形的电路。采用了一个 D 型触发器来生成至 LTC1408 的 CONV 信号。对主时钟信号进行再定时将消除由控制器件 (DSP、FPGA 等) 所引起的时钟抖动。必须把反相器和触发器作为模拟元件来处理，并应采用一个干净的模拟电源来给它们供电。

### 串行时钟输入 (SCK)

SCK 的上升沿负责推进转换过程，并对 SDO 数据流中的每个位进行更新。在 CONV 上升之后，SCK 的第 3 个上升沿将发送多达 6 组 14 位数据，并首先发送 MSB。一种简单的方法是生成 SCK 信号 (以首先驱动 LTC1408)，然后利用数目合适的反相器来对该信号进行缓冲 (以驱动处理器端口的串行时钟输入)。采用时钟信号的下降沿把来自串行数据输出 (SDO) 的数据锁存至您的处理器串行端口中。接收到的 14 位串行数据将是右对齐的 (以 6 个 16 位字的形式)，每个帧同步脉冲具有 96 个或更多的时钟信号。如果 SEL0~SEL2 引脚所选择的用于转换操作的通道数目少于 6 个，则每个通道将需要 16 个时钟，以对模拟输入进行转换，并在下一个转换脉冲之后读出合成数据。上佳的惯例是：首先驱动 LTC1408 SCK 输入，以避免在内部高速比较器做出内部位比较结果判定期间产生数字噪声干扰。与 CONV 输入不同，SCK 输入不容易遭受抖动的影响，因为输入信号已经被采样并保持恒定。

### 串行数据输出 (SDO)

上电时，SDO 输出被自动复位至高阻抗状态。SDO 输出将维持在高阻抗状态，直到一个新的转换被起动为止。在 CONV 的上升沿起动转换操作之后，SDO 将在 SCK 的第 3 个上升沿之后通过输出数据流来发送多达 6 组 14 位数据。在高阻抗模式中，6 个 (或较少的) 14 位字被两个时钟周期所分离。请注意从 SCK 至一个有效 SDO 的延迟规格。SDO 始终由 SCK 的下一个上升沿来保证有效。16~96 位输出数据流与大多数处理器的 16 位或 32 位串行端口兼容。

## 应用信息

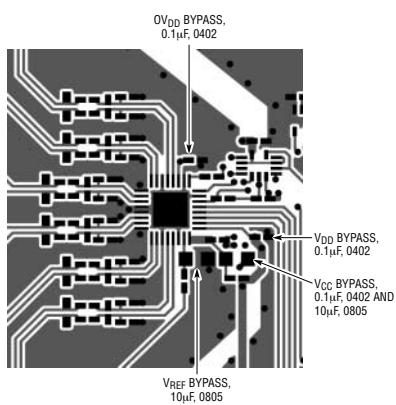

### 电路板布局和旁路

对于高分辨率和/或高速 A/D 转换器而言，建议不要采用绕接板。为了获得 LTC1408 的最佳性能，需要一个具有接地平面的印刷电路板。印刷电路板的布局应确保数字和模拟信号线被尽可能地分开。特别地，应注意不要沿著模拟信号印制线布设任何的数字信号印制线。如果需要在输入之间实现最佳的相位匹配，6 个输入通道的 12 根输入导线的长度应保持匹配。但是，应通过一根接地走线来把至 6 个输入通道的每对输入导线加以分离，以消除通道之间的高频串扰。

如本数据表首页上的方框图所示，应在  $V_{CC}$ 、 $V_{DD}$  和  $V_{REF}$  引脚上使用高质量的钽或陶瓷旁路电容器。为了实现最佳的性能，建议在  $V_{CC}$ 、 $V_{DD}$  和  $V_{REF}$  引脚上采用一个  $10\mu F$  表面贴装钽电容器和一个  $0.1\mu F$  陶瓷电容器。或者，也可采用诸如 X5R 或 X7R 型陶瓷片式电容器。必须把电容器布设在尽可能靠近器件引脚的地方。连接引脚和旁路电容器的走线必须保持简短，并应尽可能地宽。 $V_{CC}$  和  $V_{DD}$  旁路电容器返回接地平面，而  $V_{REF}$  旁路电容器则返回至引脚 22。应谨慎地把  $0.1\mu F$  的  $V_{CC}$  和  $V_{DD}$  旁路电容器布设在尽可能靠近引脚 24 和引脚 25 的地方。

图 6：推荐的布局

图 6 示出了推荐的系统接地线路。所有的模拟电路地均应终接于 LTC1408 的裸露衬垫。从 LTC1408 至电源的接地回线应为低阻抗，以实现无噪声操作。32 引脚 QFN 封装的裸露衬垫也在内部与接地衬垫相连。裸露衬垫应被焊接在 PC 板上，以减小接地线路电感。所有的接地引脚 (GND、DGND、OGND) 都必须被直接连接至位于 LTC1408 下方的同一个接地平面。

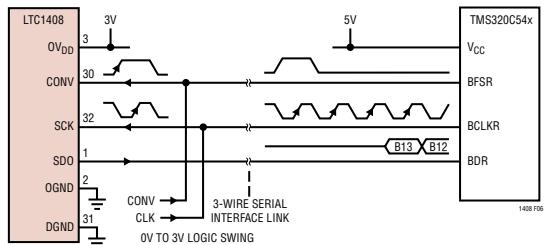

### 至 TMS320C54x 的硬件接口

LTC1408 是一款串行输出 ADC，其接口是专门针对高速数字信号处理器 (DSP) 中的高速缓冲串行端口而设计的。图 7 示出了采用一个 TMS320C54x 的该接口的实例。

TMS320C54x 中的缓冲串行端口可直接使用一个 2kB 存储段。ADC 的串行数据能够以 LTC1408 的满转换速率 (600ksps) 在两个交替的 1kB 存储段中进行实时收集。DSP 汇编码设定 BFSR 引脚上的帧同步模式 (以接受一个外部负向脉冲) 和 BCLKR 引脚上的串行时钟 (以接受一个外部正边沿时钟)。可以在靠近 LTC1408 的地方增设缓冲器，用于驱动至 DSP 的长印制线，以防止至 LTC1408 的信号遭到破坏。这种配置足以穿越一个标准的系统板，但是，可能需要在缓冲器输出端和 DSP 上分别使用源电阻器和终接电阻器，以便与非常长的传输线的特征阻抗相匹配。如果您需要终接 SDO 传输线，则首先采用一个或两个 74ACxx 逻辑门对其进行缓冲。DSP 端口的 TTL 门限输入可对和 LTC1408 一起使用的 3V 摆幅做出正确的响应。

图 7：至 TMS320C54x 的 DSP 串行接口

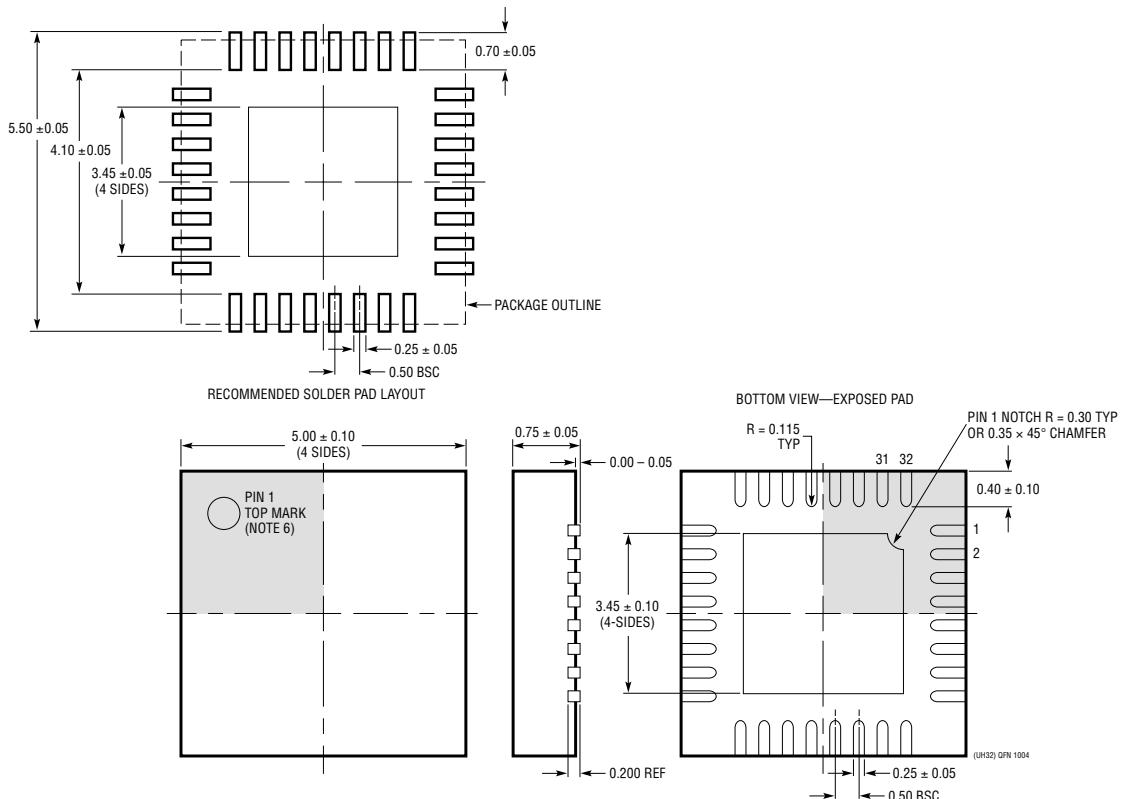

## 封装描述

**UH 封装**

**32 引脚塑料 QFN (5mm × 5mm)**

(参考 LTC DWG # 05-08-1693)

## NOTE:

1. DRAWING PROPOSED TO BE A JEDEC PACKAGE OUTLINE

MO-220 VARIATION WHHD-(X) (TO BE APPROVED)

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.20mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON THE TOP AND BOTTOM OF PACKAGE

LTC1408

## 相关器件

| 器件型号                                 | 描述                               | 备注                                         |

|--------------------------------------|----------------------------------|--------------------------------------------|

| <b>ADC</b>                           |                                  |                                            |

| LTC1402                              | 12 位, 2.2Msps 串行 ADC             | 5V 或 $\pm 5$ V 电源, 4.096V 或 $\pm 2.5$ V 跨度 |

| LTC1403/LTC1403A                     | 12 位/14 位, 2.8Msps 串行 ADC        | 3V, 15mW, 单极输入, MSOP 封装                    |

| LTC1403-1/LTC1403A-1                 | 12 位/14 位, 2.8Msps 串行 ADC        | 3V, 15mW, 双极输入, MSOP 封装                    |

| LTC1405                              | 12 位, 5Msps 并行 ADC               | 5V, 可选跨度, 115mW                            |

| LTC1407/LTC1407A                     | 12 位/14 位, 3Msps 同时采样 ADC        | 3V, 14mW, 两通道单极输入范围                        |

| LTC1407-1/LTC1407A-1                 | 12 位/14 位, 3Msps 同时采样 ADC        | 3V, 14mW, 两通道双极输入范围                        |

| LTC1411                              | 14 位, 2.5Msps 并行 ADC             | 5V, 可选跨度, 80dB SINAD                       |

| LTC1412                              | 12 位, 3Msps 并行 ADC               | $\pm 5$ V 电源, $\pm 2.5$ V 跨度, 72dB SINAD   |

| LTC1420                              | 12 位, 10Msps 并行 ADC              | 5V, 可选跨度, 72dB SINAD                       |

| LTC1608                              | 16 位, 500ksps 并行 ADC             | $\pm 5$ V 电源, $\pm 2.5$ V 跨度, 90dB SINAD   |

| LTC1609                              | 16 位, 250ksps 并行 ADC             | 5V 可配置单极/双极输入                              |

| LTC1864/LTC1865<br>LTC1864L/LTC1865L | 16 位, 250ksps 单通道/两通道串行 ADC      | 5V 或 3V(L 版本), 微功率, MSOP 封装                |

| <b>DAC</b>                           |                                  |                                            |

| LTC1592                              | 16 位, 串行 SoftSpan™ $I_{OUT}$ DAC | $\pm 1$ LSB INL/DNL, 软件可选跨度                |

| LTC1666/LTC1667<br>LTC1668           | 12 位 / 14 位 / 16 位, 50Msps DAC   | 87dB SFDR, 20ns 稳定时间                       |

| <b>基准</b>                            |                                  |                                            |

| LT1460-2.5                           | 微功率串联电压基准                        | 0.10% 初始准确度, 10ppm 漂移                      |

| LT1461-2.5                           | 精密型电压基准                          | 0.04% 初始准确度, 3ppm 漂移                       |

| LT1790-2.5                           | 采用 SOT-23 封装的微功率串联基准             | 0.05% 初始准确度, 10ppm 漂移                      |

SoftSpan 是凌力尔特公司的商标。

## 典型应用

时钟方波整形/电平移位电路允许采用 RF 正弦波发生器进行测试。

转换再定时触发器可保持低抖动时钟定时

1408 TAD