# Micropower Quad 10-Bit DAC

### **FEATURES**

- Tiny: 4 DACs in the Board Space of an SO-8

- Micropower: 59μA per DAC Plus

1μA Sleep Mode for Extended Battery Life

- Wide 2.7V to 5.5V Supply Range

- Rail-to-Rail Voltage Outputs Drive 1000pF

- Reference Range Includes Supply for Ratiometric 0V to V<sub>CC</sub> Output

- Reference Input Impedance is Code-Independent

Eliminates External Reference Buffer

- Individually Addressable DACs

- Differential Nonlinearity: ≤ ±0.75LSB Max

- Pin-Compatible Octal Version Available (LTC1660)

### **APPLICATIONS**

- Mobile Communications

- Remote Industrial Devices

- Automatic Calibration for Manufacturing

- Portable Battery-Powered Instruments

- Trim/Adjust Applications

### DESCRIPTION

The LTC®1664 integrates four accurate, serially addressable 10-bit digital-to-analog converters (DACs) in a tiny 16-pin narrow SSOP package. Each buffered DAC draws just  $59\mu A$  total supply current, yet is capable of supplying DC output currents in excess of 5mA and reliably driving capacitive loads of up to 1000pF. Sleep mode further reduces total supply current to  $1\mu A$ .

Linear Technology's proprietary, inherently monotonic voltage interpolation architecture provides excellent linearity while allowing for an exceptionally small external form factor.

Ultralow supply current, power-saving sleep mode and extremely compact size make the LTC1664 ideal for battery-powered applications, while its ease of use, high performance and wide supply range make it an excellent choice as a general-purpose converter.

$\mathcal{L}$ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

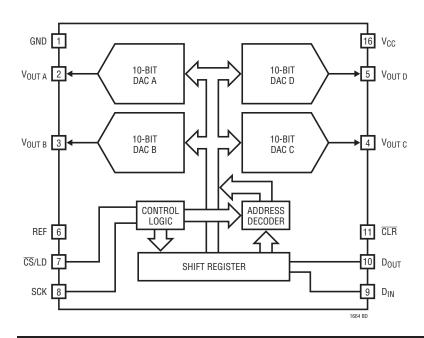

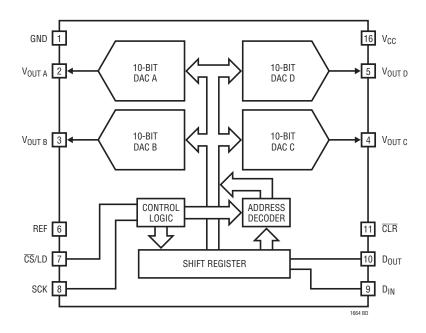

# **BLOCK DIAGRAM**

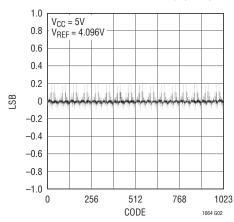

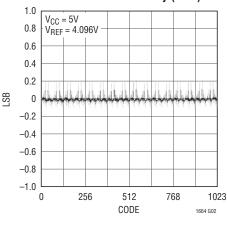

### Differential Nonlinearity (DNL)

1664fa

## **ABSOLUTE MAXIMUM RATINGS**

### (Note 1)

| V <sub>CC</sub> to GND                                       | 0.3V to 7.5V                     |

|--------------------------------------------------------------|----------------------------------|

| Logic Inputs to GND                                          | 0.3V to 7.5V                     |

| V <sub>OUT A</sub> , V <sub>OUT B</sub> V <sub>OUT D</sub> , |                                  |

| REF to GND0.3                                                | $3V \text{ to } (V_{CC} + 0.3V)$ |

| Maximum Junction Temperature                                 | 125°C                            |

| Operating Temperature Range                                  |                                  |

| LTC1664C                                                     | 0°C to 70°C                      |

| LTC1664I                                                     | 40°C to 85°C                     |

| Storage Temperature Range                                    | 65°C to 150°C                    |

| Lead Temperature (Soldering, 10 sec)                         | 300°C                            |

|                                                              |                                  |

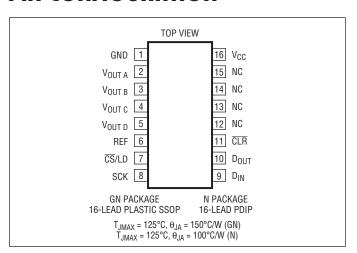

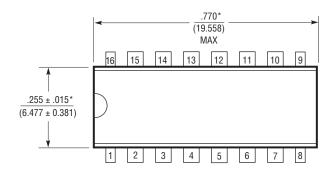

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL    | PART MARKING | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|-------------------|------------------|--------------|----------------------|-------------------|

| LTC1664CGN#PBF    | LTC1664CGN#TRPBF | 1664         | 16-Lead Plastic SSOP | 0°C to 70°C       |

| LTC1664CN#PBF     | LTC1664CN#TRPBF  | LTC1664CN    | 16-Lead PDIP         | 0°C to 70°C       |

| LTC1664IGN#PBF    | LTC1664IGN#TRPBF | 16641        | 16-Lead Plastic SSOP | -40°C to 85°C     |

| LTC1664IN#PBF     | LTC1664IN#TRPBF  | LTC1664IN    | 16-Lead PDIP         | -40°C to 85°C     |

| LEAD BASED FINISH | TAPE AND REEL    | PART MARKING | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

| LTC1664CGN        | LTC1664CGN#TR    | 1664         | 16-Lead Plastic SSOP | 0°C to 70°C       |

| LTC1664CN         | LTC1664CN#TR     | LTC1664CN    | 16-Lead PDIP         | 0°C to 70°C       |

| LTC1664IGN        | LTC1664IGN#TR    | 16641        | 16-Lead Plastic SSOP | -40°C to 85°C     |

| LTC1664IN         | LTC1664IN#TR     | LTC1664IN    | 16-Lead PDIP         | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

#

| SYMBOL           | PARAMETER                                |                                                                         | MIN | TYP                 | MAX          | UNITS           |              |

|------------------|------------------------------------------|-------------------------------------------------------------------------|-----|---------------------|--------------|-----------------|--------------|

| Accuracy         |                                          |                                                                         |     |                     |              | ,               |              |

|                  | Resolution                               |                                                                         | •   | 10                  |              |                 | Bits         |

|                  | Monotonicity                             | (Notes 2, 4)                                                            | •   | 10                  |              |                 | Bits         |

| DNL              | Differential Nonlinearity                | (Notes 2, 4)                                                            | •   |                     | ±0.2         | ±0.75           | LSB          |

| INL              | Integral Nonlinearity                    | (Notes 2, 4)                                                            | •   |                     | ±0.6         | ±2.5            | LSB          |

| V <sub>OS</sub>  | Offset Error                             | (Note 7)                                                                | •   |                     | ±10          | ±30             | mV           |

|                  | V <sub>OS</sub> Temperature Coefficient  |                                                                         | •   |                     | ±15          |                 | μV/°C        |

| FSE              | Full-Scale Error                         | V <sub>CC</sub> = 5V, V <sub>REF</sub> = 4.096V (Note 4)                | •   |                     | ±3           | ±15             | LSB          |

|                  | Full-Scale Error Temperature Coefficient |                                                                         | •   |                     | ±30          |                 | μV/°C        |

| PSR              | Power Supply Rejection                   | V <sub>REF</sub> = 2.5V                                                 |     |                     | 0.18         |                 | LSB/V        |

| Reference I      | Input                                    |                                                                         |     |                     |              |                 |              |

|                  | Input Voltage Range                      |                                                                         | •   | 0                   |              | V <sub>CC</sub> | V            |

|                  | Resistance                               | Not in Sleep Mode                                                       | •   | 70                  | 130          |                 | kΩ           |

|                  | Capacitance                              |                                                                         |     |                     | 12           |                 | pF           |

| I <sub>REF</sub> | Reference Current                        | Sleep Mode                                                              | •   |                     | 0.001        | 1               | μА           |

| Power Supp       | oly                                      |                                                                         |     |                     |              |                 |              |

| V <sub>CC</sub>  | Positive Supply Voltage                  |                                                                         | •   | 2.7                 |              | 5.5             | V            |

| I <sub>CC</sub>  | Supply Current                           | V <sub>CC</sub> = 5V (Note 3)                                           | •   |                     | 236          | 380             | μА           |

|                  |                                          | V <sub>CC</sub> = 3V (Note 3)<br>Sleep Mode (Note 3)                    |     |                     | 186<br>1     | 290<br>3        | μA<br>μA     |

| DC Perform       | ance                                     | olech Mode (Mote 9)                                                     |     |                     | '            | 0               | μΛ           |

| DO 1 01101111    | Short-Circuit Current Low                | V <sub>OUT</sub> = 0V, V <sub>CC</sub> = 5.5V, V <sub>REF</sub> = 5.1V, |     | 10                  | 30           | 100             | mA           |

|                  | Chort Ghoute Gurrent Low                 | Code = 1023 (Note 9)                                                    |     | 10                  | 00           | 100             | 1117         |

|                  | Short-Circuit Current High               | $V_{OUT} = V_{CC} = 5.5V$ , $V_{REF} = 5.1V$ ,                          | •   | 10                  | 27           | 120             | mA           |

|                  |                                          | Code = 0 (Note 9)                                                       |     |                     |              |                 |              |

| AC Perform       |                                          | 1                                                                       | 1   |                     |              |                 |              |

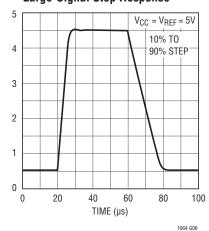

|                  | Voltage Output Slew Rate                 | Rising (Notes 4, 5)<br>Falling (Notes 4, 5)                             |     |                     | 0.60<br>0.25 |                 | V/µs<br>V/µs |

|                  | Voltage Output Settling Time             | Rising 0.1V <sub>FS</sub> to 0.9V <sub>FS</sub> ±0.5LSB (Notes 4, 5)    |     |                     | 6            |                 | μs           |

|                  | 0 " 1 10"                                | Falling 0.9V <sub>FS</sub> to 0.1V <sub>FS</sub> ± 0.5LSB (Notes 4, 5)  |     |                     | 19           |                 | μs           |

| D: :: 11/0       | Capacitive Load Driving                  |                                                                         |     |                     | 1000         |                 | pF           |

| Digital I/O      | 1                                        | T., 2                                                                   | 1   |                     |              |                 |              |

| V <sub>IH</sub>  | Digital Input High Voltage               | V <sub>CC</sub> = 2.7V to 5.5V<br>V <sub>CC</sub> = 2.7V to 3.6V        | •   | 2.4<br>2.0          |              |                 | V<br>V       |

| $V_{IL}$         | Digital Input Low Voltage                | V <sub>CC</sub> = 4.5V to 5.5V<br>V <sub>CC</sub> = 2.7V to 5.5V        | •   |                     |              | 0.8<br>0.6      | V            |

| V <sub>OH</sub>  | Digital Output High Voltage              | I <sub>OUT</sub> = −1mA, D <sub>OUT</sub> Only                          | •   | V <sub>CC</sub> - 1 |              |                 | V            |

| $V_{OL}$         | Digital Output Low Voltage               | I <sub>OUT</sub> = 1mA, D <sub>OUT</sub> Only                           | •   |                     |              | 0.4             | V            |

| $I_{LK}$         | Digital Input Leakage                    | V <sub>IN</sub> = GND to V <sub>CC</sub>                                | •   |                     | 0.05         | ±10             | μΑ           |

| C <sub>IN</sub>  | Digital Input Capacitance                |                                                                         |     |                     | 2            |                 | pF           |

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \, ^{\circ}\text{C}$ . (Figure 1)

| SYMBOL                        | PARAMETER                          | CONDITIONS                        |   | MIN | TYP | MAX  | UNITS |

|-------------------------------|------------------------------------|-----------------------------------|---|-----|-----|------|-------|

| $V_{CC} = 4.5V \text{ to } 5$ | 5.5V                               | -                                 |   |     |     |      |       |

| t <sub>1</sub>                | D <sub>IN</sub> Valid to SCK Setup |                                   | • | 40  |     |      | ns    |

| $\overline{t_2}$              | D <sub>IN</sub> Valid to SCK Hold  |                                   | • | 0   |     |      | ns    |

| t <sub>3</sub>                | SCK High Time                      | (Note 6)                          | • | 30  |     |      | ns    |

| $\overline{t_4}$              | SCK Low Time                       | (Note 6)                          | • | 30  |     |      | ns    |

| t <sub>5</sub>                | CS/LD Pulse Width                  | (Note 6)                          | • | 80  |     |      | ns    |

| $\overline{t_6}$              | LSB SCK High to CS/LD High         | (Note 6)                          | • | 30  |     |      | ns    |

| t <sub>7</sub>                | CS/LD Low to SCK High              | (Note 6)                          | • | 80  |     |      | ns    |

| t <sub>8</sub>                | D <sub>OUT</sub> Propagation Delay | C <sub>LOAD</sub> = 15pF (Note 6) | • | 5   |     | 80   | ns    |

| t <sub>9</sub>                | SCK Low to CS/LD Low               | (Note 6)                          | • | 20  |     |      | ns    |

| t <sub>10</sub>               | CLR Pulse Width                    | (Note 6)                          | • | 100 |     |      | ns    |

| t <sub>11</sub>               | CS/LD High to SCK Positive Edge    | (Note 6)                          | • | 30  |     |      | ns    |

|                               | SCK Frequency                      | (Notes 6 and 8)                   | • |     |     | 16.7 | MHz   |

| $V_{CC} = 2.7V \text{ to } 5$ | 5.5V                               |                                   |   |     |     |      |       |

| t <sub>1</sub>                | D <sub>IN</sub> Valid to SCK Setup | (Note 6)                          | • | 60  |     |      | ns    |

| $\overline{t_2}$              | D <sub>IN</sub> Valid to SCK Hold  | (Note 6)                          | • | 0   |     |      | ns    |

| t <sub>3</sub>                | SCK High Time                      | (Note 6)                          | • | 50  |     |      | ns    |

| t <sub>4</sub>                | SCK Low Time                       | (Note 6)                          | • | 50  |     |      | ns    |

| $\overline{t_5}$              | CS/LD Pulse Width                  | (Note 6)                          | • | 100 |     |      | ns    |

| $\overline{t_6}$              | LSB SCK High to CS/LD High         | (Note 6)                          | • | 50  |     |      | ns    |

| $\overline{t_7}$              | CS/LD Low to SCK High              | (Note 6)                          | • | 100 |     |      | ns    |

| t <sub>8</sub>                | D <sub>OUT</sub> Propagation Delay | C <sub>LOAD</sub> = 15pF (Note 6) | • | 5   |     | 150  | ns    |

| t <sub>9</sub>                | SCK Low to CS/LD Low               | (Note 6)                          | • | 30  |     |      | ns    |

| t <sub>10</sub>               | CLR Pulse Width                    | (Note 6)                          | • | 120 |     |      | ns    |

| t <sub>11</sub>               | CS/LD High to SCK Positive Edge    | (Note 6)                          | • | 30  |     |      | ns    |

|                               | SCK Frequency                      | (Notes 6 and 8)                   | • |     |     | 10   | MHz   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Nonlinearity and monotonicity are defined and tested at  $V_{CC}$  = 5V,  $V_{REF}$  = 4.096V, from code 20 to code 1023. See the Rail-to-Rail Output Considerations section.

Note 3: Digital inputs at 0V or V<sub>CC</sub>.

**Note 4:** Load is  $10k\Omega$  in parallel with 100pE

**Note 5:**  $V_{CC} = V_{REF} = 5V$ .

Note 6: Guaranteed by design and not subject to test.

Note 7: Measured at code 20.

**Note 8:** If a continuous clock is used,  $\overline{\text{CS}}/\text{LD}$  timing (t<sub>7</sub> and t<sub>9</sub>) will limit the maximum clock frequency to 5MHz at 4.5V to 5.5V (3.85MHz at 2.7V to 5.5V).

Note 9: Any output shorted.

## TYPICAL PERFORMANCE CHARACTERISTICS

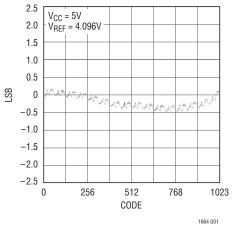

## Integral Nonlinearity (INL)

#### Differential Nonlinearity (DNL)

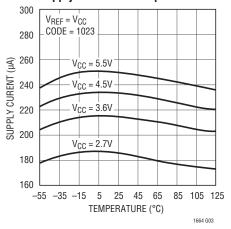

#### Supply Current vs Temperature

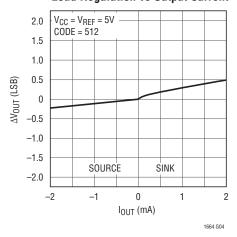

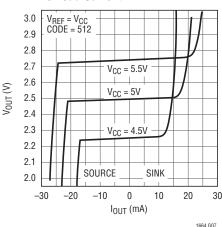

#### **Load Regulation vs Output Current**

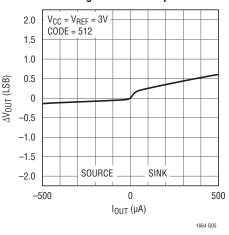

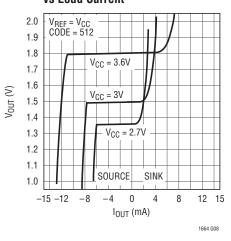

#### Load Regulation vs Output Current

Large-Signal Step Response

V<sub>0UT</sub> (V)

# Mid-Scale Output Voltage vs Load Current

# Mid-Scale Output Voltage vs Load Current

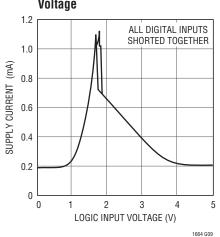

#### Supply Current vs Logic Input Voltage

1664fa

# TYPICAL PERFORMANCE CHARACTERISTICS

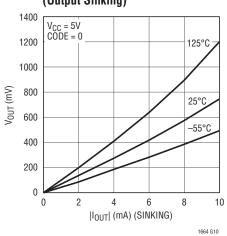

Minimum V<sub>OUT</sub> vs Load Current (Output Sinking)

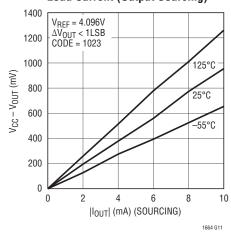

### Minimum Supply Headroom vs Load Current (Output Sourcing)

# PIN FUNCTIONS

GND (Pin 1): System Ground.

$V_{OUT\,A}$  to  $V_{OUT\,D}$  (Pins 2–5): DAC Analog Voltage Outputs. The output range is:

0 to

$$\left(\frac{1023}{1024}\right)$$

V<sub>REF</sub>

**REF (Pin 6):** Reference Voltage Input.  $0V \le V_{REF} \le V_{CC}$ .

$\overline{\text{CS}/\text{LD}}$  (Pin 7): Serial Interface Chip Select/Load Input. When  $\overline{\text{CS}}/\text{LD}$  is low, SCK is enabled for shifting data on D<sub>IN</sub> into the register. When  $\overline{\text{CS}}/\text{LD}$  is pulled high, SCK is disabled and data is loaded from the shift register into the specified DAC register(s), updating the analog output(s). CMOS and TTL compatible.

**SCK (Pin 8):** Serial Interface Clock Input. CMOS and TTL compatible.

$D_{IN}$  (Pin 9): Serial Interface Data Input. Data on the  $D_{IN}$  pin is shifted into the 16-bit register on the rising edge of SCK. CMOS and TTL compatible.

$D_{OUT}$  (Pin 10): Serial Interface Data Output. Data appears on  $D_{OUT}$  16 positive SCK edges after being applied to  $D_{IN}$ . May be tied to  $D_{IN}$  of another serial device for daisy-chain operation. CMOS and TTL compatible.

**CLR** (**Pin 11**): Asynchronous Clear Input. All internal shift and DAC registers are cleared to zero at the falling edge of the  $\overline{\text{CLR}}$  signal, forcing the analog outputs to zero-scale. CMOS and TTL compatible.

**NC (Pins 12–15):** Make no electrical connection to these pins.

**V<sub>CC</sub>** (**Pin 16**): Supply Voltage Input.  $2.7V \le V_{CC} \le 5.5V$ .

LINEAR TECHNOLOGY

# **BLOCK DIAGRAM**

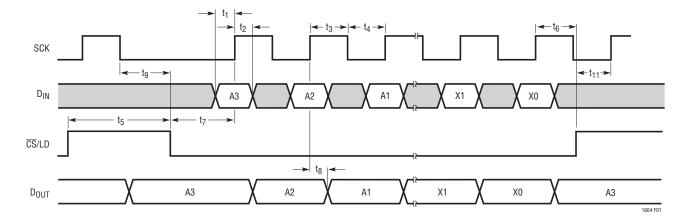

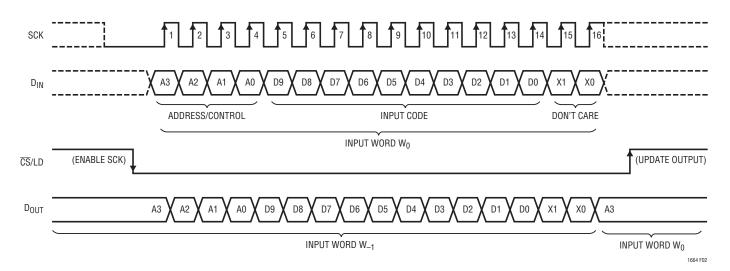

# **TIMING DIAGRAM**

Figure 1

### **OPERATION**

#### **Transfer Function**

The transfer function is

$$V_{OUT(IDEAL)} = \left(\frac{k}{1024}\right) V_{REF}$$

where k is the decimal equivalent of the binary DAC input code and  $V_{REF}$  is the voltage at REF (Pin 6).

### Power-On Reset

The LTC1664 clears the outputs to zero-scale when power is first applied, making system initialization consistent and repeatable.

### **Power Supply Sequencing**

The voltage at REF (Pin 6) should be kept within the range  $-0.3V \le V_{REF} \le V_{CC} + 0.3V$  (see Absolute Maximum Ratings). Particular care should be taken to observe these limits during power supply turn-on and turn-off sequences, when the voltage at  $V_{CC}$  (Pin 16) is in transition. If it is not possible to sequence the supplies, connect a Schottky diode from REF (anode) to  $V_{CC}$  (cathode).

#### **Serial Interface**

Referring to Figure 2: With  $\overline{\text{CS}}/\text{LD}$  held low, data on the D<sub>IN</sub> input is shifted into the 16-bit shift register on the positive edge of SCK. The 4-bit DAC address, A3-A0, is loaded first (see Table 2), then the 10-bit input code, D9-D0, ordered MSB-to-LSB in each case. Two don't-care bits, X1-X0, are loaded last. When the full 16-bit input word has been shifted in,  $\overline{\text{CS}}/\text{LD}$  is pulled high, loading the DAC register with the word and causing the addressed DAC output(s) to update. The clock is disabled internally when  $\overline{\text{CS}}/\text{LD}$  is high. Note: SCK must be low before  $\overline{\text{CS}}/\text{LD}$  is pulled low.

The buffered serial output of the shift register is available on the  $D_{OUT}$  pin, which swings from GND to  $V_{CC}$ . Data appears on  $D_{OUT}$  16 positive SCK edges after being applied to  $D_{IN}$ .

Multiple LTC1664's can be controlled from a single 3-wire serial port (i.e., SCK,  $D_{IN}$  and  $\overline{CS}/LD$ ) by using the included daisychain facility. A series of m chips is configured by connecting each  $D_{OUT}$  (except the last) to  $D_{IN}$  of the next chip, forming a single 16m-bit shift register. The SCK and  $\overline{CS}/LD$  signals are common to all chips in the chain. In use,  $\overline{CS}/LD$  is held low while m 16-bit words are clocked to  $D_{IN}$  of the first chip;  $\overline{CS}/LD$  is then pulled high, updating all of them simultaneously.

### Sleep Mode

DAC address 1110<sub>b</sub> is reserved for the special sleep instruction (see Table 2). In this mode, the digital interface stays active while the analog circuits are disabled; static power consumption is thus virtually eliminated. The reference input and analog outputs are set in a high impedance state and all DAC settings are retained in memory so that when sleep mode is exited, the outputs of DACs not updated by the Wake command are restored to their last active state.

Sleep mode is initiated by performing a load sequence to address  $1110_b$  (the DAC input word D9-D0 is ignored). Once in sleep mode, a load sequence to any other address (including "No Change" address  $0000_b$ ) causes the LTC1664 to Wake. It is possible to keep one or more chips of a daisy chain in continuous sleep mode by giving the sleep instruction to these chips each time the active chips in the chain are updated.

### **Voltage Outputs**

Each of the four rail-to-rail output amplifiers contained in the LTC1664 can source or sink up to 5mA. The outputs swing to within a few millivolts of either supply rail when unloaded and have an equivalent output resistance of  $85\Omega$  when driving a load to the rails. The output amplifiers are stable driving capacitive loads of up to 1000pF.

A small resistor placed in series with the output can be used to achieve stability for any load capacitance. A  $1\mu F$

Table 1. LTC1664 Input Word

|                 | А3 | A2 | A1 | A0 | D9  | D8   | D7  | D6 | D5 | D4 | D3 | D2   | D1  | D0      | X1 | Х0 |  |

|-----------------|----|----|----|----|-----|------|-----|----|----|----|----|------|-----|---------|----|----|--|

|                 |    |    |    |    |     |      |     |    | _  |    |    |      |     | <u></u> | _  |    |  |

| ADDRESS/CONTROL |    |    |    |    | II\ | IPUT | COI | DE |    |    | D( | ON'T | CAF | ₹E      |    |    |  |

LINEAD TECHNOLOGY

# **OPERATION**

Figure 2. LTC1664 Register Loading Sequence

**Table 2. DAC Address/Control Functions**

|    | ADDRESS/ | CONTROL |    |                                                  |              |  |  |

|----|----------|---------|----|--------------------------------------------------|--------------|--|--|

| А3 | A2       | A1      | A0 | DAC STATUS                                       | SLEEP STATUS |  |  |

| 0  | 0        | 0       | 0  | No Change                                        | Wake         |  |  |

| 0  | 0        | 0       | 1  | Load DAC A                                       | Wake         |  |  |

| 0  | 0        | 1       | 0  | Load DAC B                                       | Wake         |  |  |

| 0  | 0        | 1       | 1  | Load DAC C                                       | Wake         |  |  |

| 0  | 1        | 0       | 0  | Load DAC D                                       | Wake         |  |  |

| 0  | 1        | 0       | 1  | Reser                                            | ved          |  |  |

| 0  | 1        | 1       | 0  | Reserved                                         |              |  |  |

| 0  | 1        | 1       | 1  | Reserved                                         |              |  |  |

| 1  | 0        | 0       | 0  | Reserved                                         |              |  |  |

| 1  | 0        | 0       | 1  | Reserved                                         |              |  |  |

| 1  | 0        | 1       | 0  | Reserved                                         |              |  |  |

| 1  | 0        | 1       | 1  | Reserved                                         |              |  |  |

| 1  | 1        | 0       | 0  | Reserved                                         |              |  |  |

| 1  | 1        | 0       | 1  | Reserved                                         |              |  |  |

| 1  | 1        | 1       | 0  | No Change                                        | Sleep        |  |  |

| 1  | 1        | 1       | 1  | Load <b>ALL</b> DACs<br>with Same<br>10-Bit Code | Wake         |  |  |

### **OPERATION**

load can be successfully driven by inserting a  $20\Omega$  resistor; a  $2.2\mu F$  load needs only a  $10\Omega$  resistor. In either case, larger values of resistance, capacitance or both may be safely substituted for the values given.

### Rail-to-Rail Output Considerations

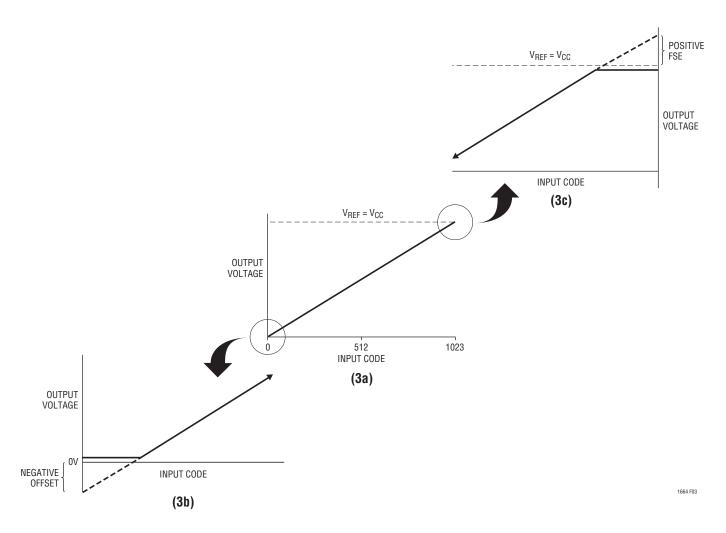

In any rail-to-rail voltage output DAC, the output is limited to voltages within the supply range.

If the DAC offset is negative, the output for the lowest codes limits at 0V as shown in Figure 3b.

Similarly, limiting can occur near full-scale when the REF pin is tied to  $V_{CC}$ . If  $V_{REF} = V_{CC}$  and the DAC full-scale error (FSE) is positive, the output for the highest codes limits at  $V_{CC}$  as shown in Figure 3c. No full-scale limiting can occur if  $V_{RFF}$  is less than  $V_{CC}$  – FSE.

Offset and linearity are defined and tested over the region of the DAC transfer function where no output limiting can occur.

Figure 3. Effects of Rail-to-Rail Operation On a DAC Transfer Curve. (a) Overall Transfer Function (b) Effect of Negative Offset for Codes Near Zero-Scale (c) Effect of Positive Full-Scale Error for Input Codes Near Full-Scale When  $V_{REF} = V_{CC}$

LINEAR TECHNOLOGY

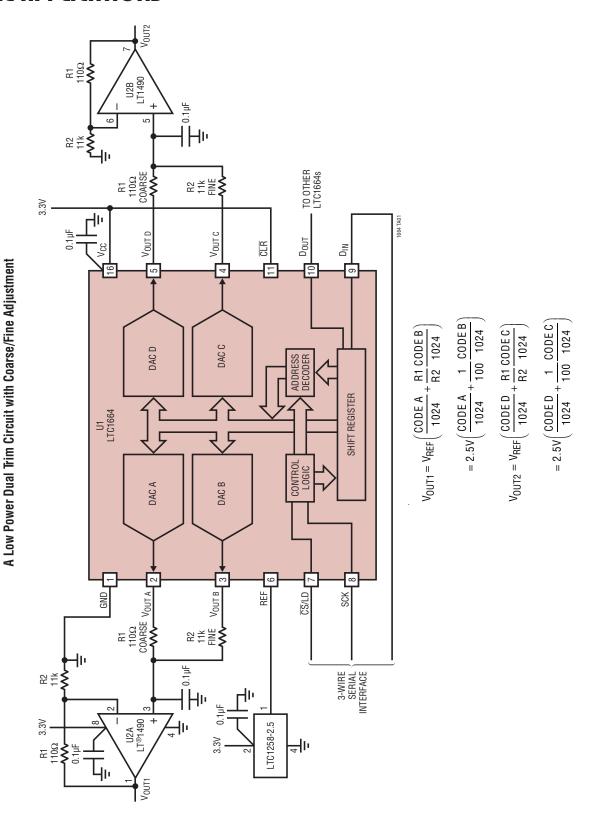

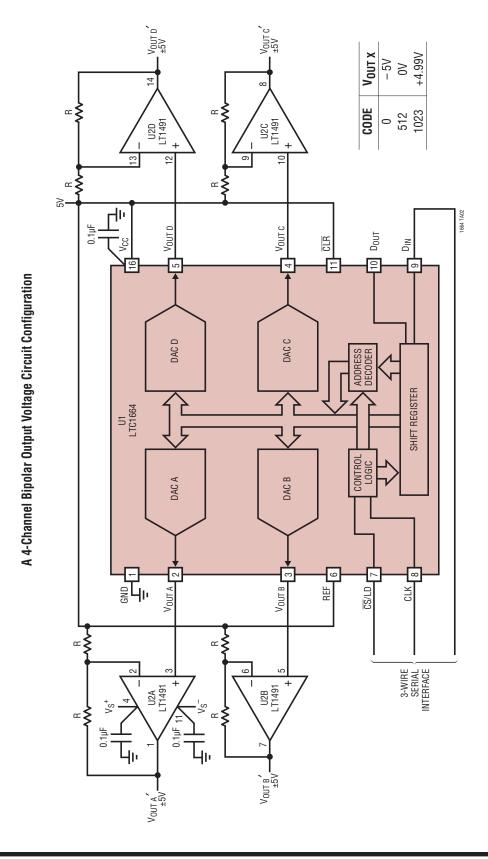

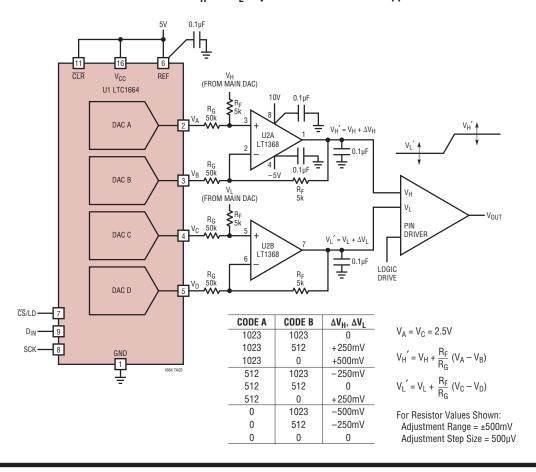

# TYPICAL APPLICATIONS

# TYPICAL APPLICATIONS

TECHNOLOGY TECHNOLOGY

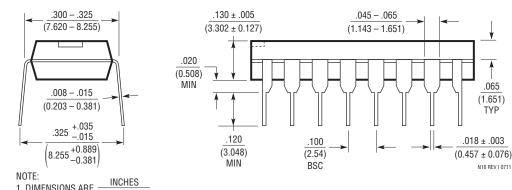

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

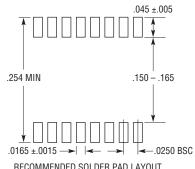

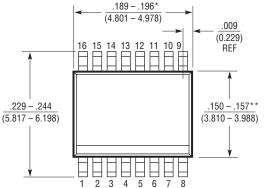

### GN Package 16-Lead Plastic SSOP (Narrow 0.150)

(LTC DWG # 05-08-1641)

NOTE:

1. CONTROLLING DIMENSION: INCHES

.016 - .050

(0.406 - 1.270)

- 2. DIMENSIONS ARE IN  $\frac{\text{INCHES}}{(\text{MILLIMETERS})}$

- 3. DRAWING NOT TO SCALE

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

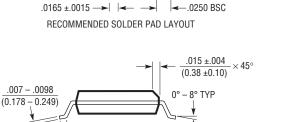

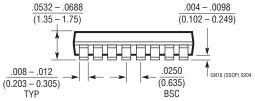

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

### N Package 16-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

<sup>1.</sup> DIMENSIONS ARE INCHES

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

.065

(1.651)

TYP

N16 REV I 0711

# **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                   | PAGE NUMBER |  |  |

|-----|-------|---------------------------------------------------------------|-------------|--|--|

| Α   | 01/12 | Removed Typical values in the Timing Characteristics section. | 4           |  |  |

|     |       | Forrected Related Parts listing for LTC1659.                  |             |  |  |

# TYPICAL APPLICATION

### An 11-Bit Pin Driver $V_H$ and $V_L$ Adjustment Circuit for ATE Applications

# **RELATED PARTS**

| PART NUMBER      | DESCRIPTION                                                                 | COMMENTS                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC1665/LTC1660  | Octal 8-/10-Bit V <sub>OUT</sub> DAC in 16-Pin Narrow SSOP                  | V <sub>CC</sub> = 2.7V to 5.5V, 60μA per DAC, Rail-to-Rail Output                                                                                   |

| LTC1661          | Dual 10-Bit V <sub>OUT</sub> DAC in 8-Pin MSOP Package                      | V <sub>CC</sub> = 2.7V to 5.5V, 60μA per DAC, Rail-to-Rail Output                                                                                   |

| LTC1662          | Ultra Low Power Dual 10-Bit V <sub>OUT</sub> DAC in 8-Pin MSOP Package      | V <sub>CC</sub> = 2.7V to 5.5V, 1.5μA per DAC, Rail-to-Rail Output                                                                                  |

| LTC1663          | Single 10-Bit V <sub>OUT</sub> DAC with 2-Wire Interface in SOT-23 Package  | V <sub>CC</sub> = 2.7V to 5.5V, Internal Reference, 60μA                                                                                            |

| LTC1446/LTC1446L | Dual 12-Bit V <sub>OUT</sub> DACs in SO-8 Package with Internal Reference   | LTC1446: V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V to 4.095V<br>LTC1446L: V <sub>CC</sub> = 2.7V to 5.5V, V <sub>OUT</sub> = 0V to 2.5V |

| LTC1448          | Dual 12-Bit V <sub>OUT</sub> DAC in SO-8 Package                            | $V_{CC}$ = 2.7V to 5.5V, External Reference Can Be Tied to $V_{CC}$                                                                                 |

| LTC1454/LTC1454L | Dual 12-Bit V <sub>OUT</sub> DACs in SO-16 Package with Added Functionality | LTC1454: V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V to 4.095V<br>LTC1454L: V <sub>CC</sub> = 2.7V to 5.5V, V <sub>OUT</sub> = 0V to 2.5V |

| LTC1458/LTC1458L | Quad 12-Bit Rail-to-Rail Output DACs with Added Functionality               | LTC1458: V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V to 4.095V<br>LTC1458L: V <sub>CC</sub> = 2.7V to 5.5V, V <sub>OUT</sub> = 0V to 2.5V |

| LT1460           | Micropower Precision Series Reference, 2.5V, 5V, 10V Versions               | 0.075% Max, 10ppm/°C Max, Only 130μA Supply Current                                                                                                 |

| LTC1590          | Dual 12-Bit I <sub>OUT</sub> DAC in SO-16 Package                           | V <sub>CC</sub> = 4.5V to 5.5V, 4-Quadrant Multiplication                                                                                           |

| LTC1654          | Dual 14-Bit DAC in SO-8 Footprint                                           | 1LBS DNL, Selectable Speed/Power                                                                                                                    |

| LTC1659          | Single Rail-to-Rail 12-Bit V <sub>OUT</sub> DAC in 8-Lead MSOP Package      | $V_{CC}$ = 2.7V to 5.5V, Low Power Multiplying $V_{OUT}$ DAC. Output Swings from GND to REF. REF Input Can Be Tied to $V_{CC}$                      |

LT 0112 REV A · PRINTED IN USA

LITEAN

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2000

1664fa