## 特点

- 采样率：50Msps

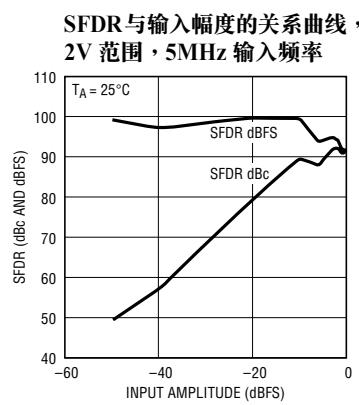

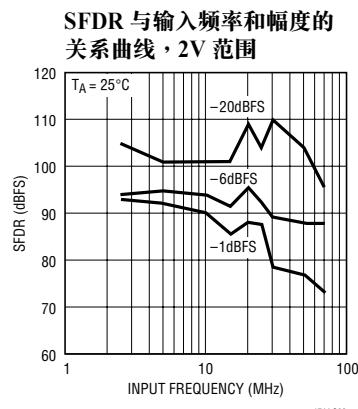

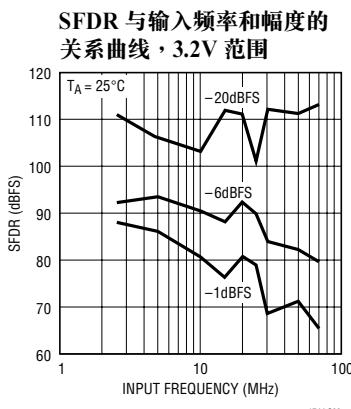

- 77dB SNR 和 87dB SFDR (3.2V 范围)

- 73.5dB SNR 和 90dB SFDR (2V 范围)

- 无漏失码

- 单 5V 电源

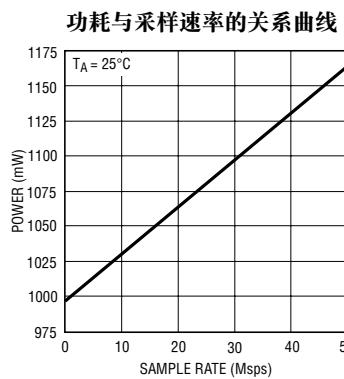

- 功耗：1.2W

- 可选输入范围：±1V 或 ±1.6V

- 150MHz 满功率带宽 S/H

- 引脚兼容系列

- 25 Msps：LTC1746 (14 位), LTC1745 (12 位)

- 50 Msps：LTC1744 (14 位), LTC1743 (12 位)

- 65 Msps：LTC1742 (14 位), LTC1741 (12 位)

- 80 Msps：LTC1748 (14 位), LTC1747 (12 位)

- 48 引脚 TSSOP 封装

## 应用

- 电信

- 接收器

- 蜂窝通信基站

- 频谱分析仪

- 成像系统

**L**、**LTC** 和 **LT** 是凌特公司的注册商标。

No Latency  $\Delta$  是凌特公司的商标。

## 描述

LTC<sup>®</sup>1744 是一款专为对高频、宽动态范围信号进行数字化处理而设计的 50Msps 采样率 14 位 A/D 转换器。±1V 和 ±1.6V 的引脚可选输入范围以及电容可设置模式的运用使得 LTC1744 能够对各种应用进行优化。

对于要求严谨的电信应用而言，LTC1744 是一种完美的选择。在 AC 特性方面，其 SNR 和无寄生动态范围分别达到了 77dB 和 87dB。0.3ps<sub>RMS</sub> 的超低抖动允许 IF 频率进行欠采样，并获得卓越的噪声特性。DC 规格包括 ±4LSB 最大值 INL 和在整个工作温度范围无漏码特性。

数字接口与 5V、3V 和 2V 逻辑系统相兼容。可由 PECL、GTL 和其他的低摆幅逻辑器件系列或单端 TTL 或 CMOS 对 ENC 和  $\overline{ENC}$  进行差分驱动。也可利用一个正弦信号对低噪声、高增益的  $\overline{ENC}$  和 ENC 输入进行驱动，且不会使性能发生劣化。一个单独的输出电源可在 0.5V 至 5V 的范围内工作，使得它能够容易地与任何的低压 DSP 或 FIFO 直接相连。

具有直通式引出脚型的 TSSOP 封装简化了电路板布局。

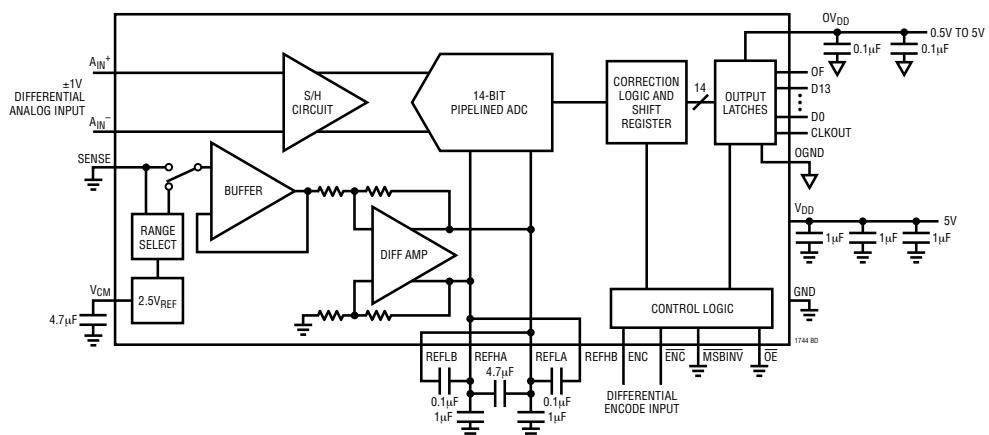

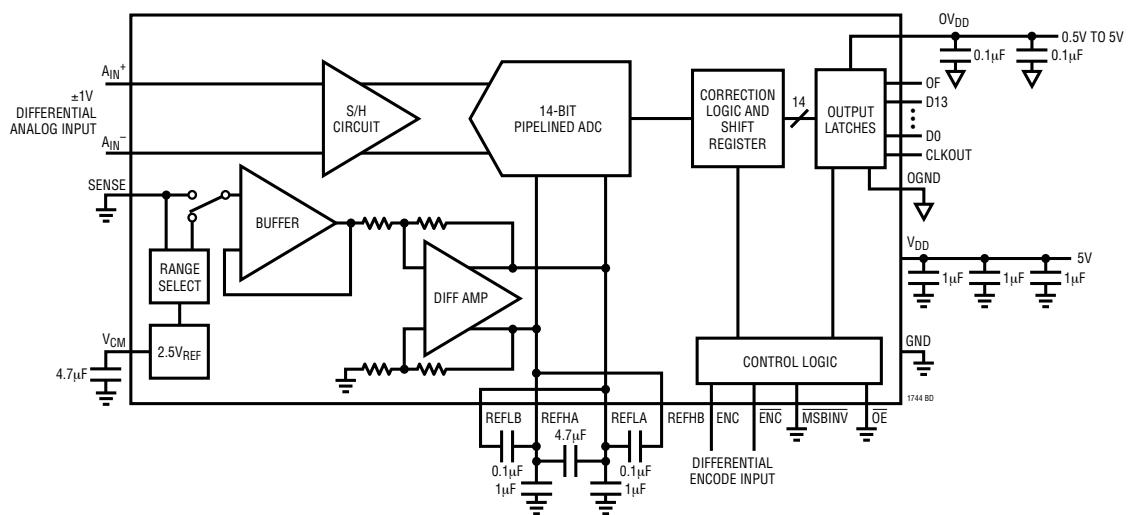

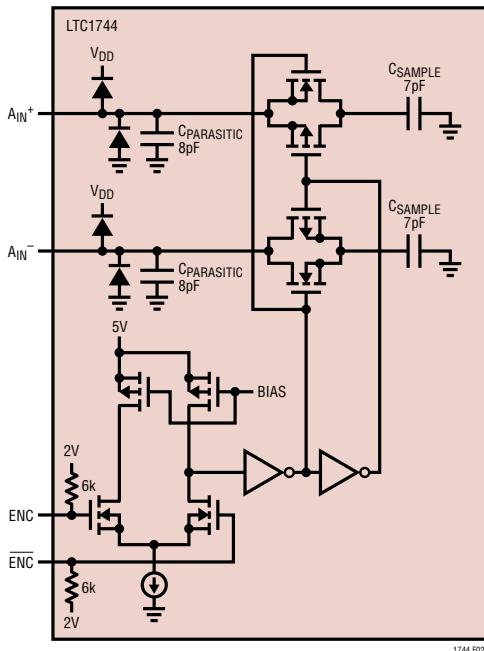

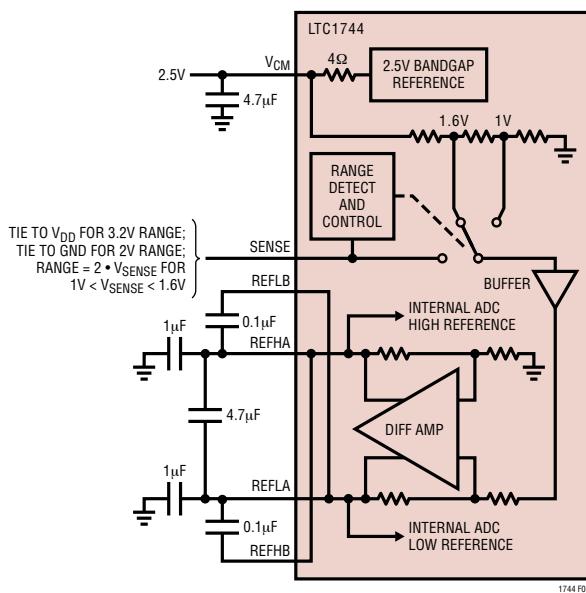

## 方框图

具有一个 ±1V 差分输入范围的 50Msps、14 位 ADC

绝对最大额定值  $OV_{DD} = V_{DD}$  (注 1、2)

## 封装/订购信息

|                   |                             |

|-------------------|-----------------------------|

| 供电电压 ( $V_{DD}$ ) | 6V                          |

| 模拟输入电压 (注 3)      | -0.3V 至 ( $V_{DD} + 0.3V$ ) |

| 数字输入电压 (注 4)      | -0.3V 至 ( $V_{DD} + 0.3V$ ) |

| 数字输出电压            | -0.3V 至 ( $V_{DD} + 0.3V$ ) |

| OGND 电压           | -0.3V 至 1V                  |

| 功耗                | 2000mW                      |

| 工作温度范围            |                             |

| LTC1744C          | 0°C 至 70°C                  |

| LTC1744I          | -40°C 至 85°C                |

| 贮存温度范围            | -65°C 至 150°C               |

| 引脚温度 (焊接时间 10 秒)  | 300°C                       |

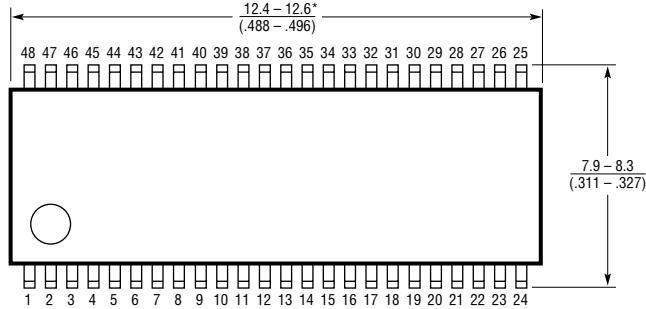

| TOP VIEW     |              | 产品型号       |

|--------------|--------------|------------|

| SENSE 1      | 48 OF        | LTC1744CFW |

| $V_{CM}$ 2   | 47 OGND      | LTC1744IFW |

| GND 3        | 46 D13       |            |

| $A_{IN}^+$ 4 | 45 D12       |            |

| $A_{IN}^-$ 5 | 44 D11       |            |

| GND 6        | 43 $OV_{DD}$ |            |

| $V_{DD}$ 7   | 42 D10       |            |

| $V_{DD}$ 8   | 41 D9        |            |

| GND 9        | 40 D8        |            |

| REFLB 10     | 39 D7        |            |

| REFHA 11     | 38 OGND      |            |

| GND 12       | 37 GND       |            |

| GND 13       | 36 GND       |            |

| REFLA 14     | 35 D6        |            |

| REFHB 15     | 34 D5        |            |

| GND 16       | 33 D4        |            |

| $V_{DD}$ 17  | 32 $OV_{DD}$ |            |

| $V_{DD}$ 18  | 31 D3        |            |

| GND 19       | 30 D2        |            |

| $V_{DD}$ 20  | 29 D1        |            |

| GND 21       | 28 D0        |            |

| MSBINV 22    | 27 OGND      |            |

| ENC 23       | 26 CLKOUT    |            |

| ENC 24       | 25 OE        |            |

FW PACKAGE

48-LEAD PLASTIC TSSOP

$T_{JMAX} = 150^\circ\text{C}$ ,  $\theta_{JA} = 35^\circ\text{C}/\text{W}$

对于规定工作温度范围更宽的器件，请咨询凌特公司。

转换器特性 凡标注 ● 表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。(注 5)

| 参数         | 条件                      | 最小值  | 典型值       | 最大值      | 单位                    |

|------------|-------------------------|------|-----------|----------|-----------------------|

| 分辨率 (无漏失码) |                         | ● 14 |           |          | 位                     |

| 积分线性误差     | (注 6)                   | ● -4 | $\pm 1$   | 4        | LSB                   |

| 差分线性误差     |                         | ● -1 | $\pm 0.5$ | 1.5      | LSB                   |

| 偏移误差       | (注 7)                   |      | -20       | $\pm 5$  | mV                    |

| 增益误差       | 外部基准 ( $SENSE = 1.6V$ ) |      | -3        | $\pm 1$  | %FS                   |

| 全标度温度系数    | $I_{OUT(REF)} = 0$      |      |           | $\pm 40$ | ppm/ $^\circ\text{C}$ |

模拟输入 凡标注 ● 表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。(注 5)

| 符号           | 参数            | 条件                                               | 最小值 | 典型值                 | 最大值 | 单位    |

|--------------|---------------|--------------------------------------------------|-----|---------------------|-----|-------|

| $V_{IN}$     | 模拟输入范围 (注 8)  | $4.75V \leq V_{DD} \leq 5.25V$                   | ●   | $\pm 1$ 至 $\pm 1.6$ |     | V     |

| $I_{IN}$     | 模拟输入漏电流       |                                                  |     | 10                  |     | nA    |

| $C_{IN}$     | 模拟输入电容        | 采样模式 $ENC < \bar{ENC}$<br>保持模式 $ENC > \bar{ENC}$ |     | 15                  |     | pF    |

| $t_{ACQ}$    | 采样及保持采集时间     |                                                  | ●   | 7.5                 | 9.5 | ns    |

| $t_{AP}$     | 采样及保持采集延迟时间   |                                                  |     | 0                   |     | ns    |

| $t_{JITTER}$ | 采样及保持采集延迟时间抖动 |                                                  |     | 0.3                 |     | pSRMS |

| CMRR         | 模拟输入共模抑制比     | $1.0V < (A_{IN}^- = A_{IN}^+) < 3.5$             |     | 80                  |     | dB    |

## 动态准确度 凡标注●表示该指标适合整个工作温度范围，否则仅指 $T_A = 25^\circ\text{C}$ , $A_{IN} = -1\text{dBFS}$ 。(注5)

| 符号        | 参数         | 条件                                                               | 最小值 | 典型值  | 最大值  | 单位   |

|-----------|------------|------------------------------------------------------------------|-----|------|------|------|

| SNR       | 信噪比        | 5MHz 输入信号 (2V 范围)                                                | ●   | 73.5 | 77   | dBFS |

|           |            | 5MHz 输入信号 (3.2V 范围)                                              |     | 75.5 | 77   | dBFS |

|           |            | 25MHz 输入信号 (2V 范围)                                               |     | 72.5 | 75.5 | dBFS |

|           |            | 25MHz 输入信号 (3.2V 范围)                                             |     | 75.5 | 77   | dBFS |

| SFDR      | 无寄生动态范围    | 70MHz 输入信号 (2V 范围)                                               |     | 70   | 71.5 | dBFS |

|           |            | 70MHz 输入信号 (3.2V 范围)                                             |     | 71.5 | 73   | dBFS |

|           |            | 5MHz 输入信号 (2V 范围)                                                | ●   | 92   | 87   | dB   |

|           |            | 5MHz 输入信号 (3.2V 范围)                                              |     | 76   | 79   | dB   |

| S/(N + D) | 信号与噪声加失真之比 | 25MHz 输入信号 (2V 范围)                                               |     | 87   | 87   | dB   |

|           |            | 25MHz 输入信号 (3.2V 范围)                                             |     | 79   | 79   | dB   |

|           |            | 70MHz 输入信号 (2V 范围)                                               |     | 73   | 73   | dB   |

|           |            | 70MHz 输入信号 (3.2V 范围)                                             |     | 66   | 66   | dB   |

| THD       | 总谐波失真      | 5MHz 输入信号 (2V 范围)                                                | ●   | 73   | 76   | dBFS |

|           |            | 5MHz 输入信号 (3.2V 范围)                                              |     | 73   | 76   | dBFS |

|           |            | 25MHz 输入信号 (2V 范围)                                               |     | 72.5 | 73.5 | dBFS |

|           |            | 25MHz 输入信号 (3.2V 范围)                                             |     | 73.5 | 73.5 | dBFS |

| MD        | 交调失真       | 70MHz 输入信号 (2V 范围)                                               |     | 68   | 68   | dBFS |

|           |            | 70MHz 输入信号 (3.2V 范围)                                             |     | 64   | 64   | dBFS |

|           | 采样及保持带宽    | $f_{IN1} = 2.52\text{MHz}$ , $f_{IN2} = 5.2\text{MHz}$ (2V 范围)   |     | -90  | -90  | dBc  |

|           |            | $f_{IN1} = 2.52\text{MHz}$ , $f_{IN2} = 5.2\text{MHz}$ (3.2V 范围) |     | -80  | -80  | dBc  |

|           |            | $R_{SOURCE} = 50\Omega$                                          |     | 150  | 150  | MHz  |

## 内部基准特性 (注5)

| 参数              | 条件                                           | 最小值      | 典型值 | 最大值                   | 单位 |

|-----------------|----------------------------------------------|----------|-----|-----------------------|----|

| $V_{CM}$ 输出电压   | $I_{OUT} = 0$                                | 2.42     | 2.5 | 2.58                  | V  |

| $V_{CM}$ 输出温度系数 | $I_{OUT} = 0$                                | $\pm 30$ |     | ppm/ $^\circ\text{C}$ |    |

| $V_{CM}$ 电压调节   | $4.75\text{V} \leq V_{DD} \leq 5.25\text{V}$ | 3        |     | LSB/V                 |    |

| $V_{CM}$ 输出电阻   | $1\text{mA} \leq  I_{OUT}  \leq 1\text{mA}$  | 4        |     | $\Omega$              |    |

数字输入和数字输出 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。(注 5)

| 符号           | 参数                | 条件                                                                     | 最小值                     | 典型值 | 最大值      | 单位            |

|--------------|-------------------|------------------------------------------------------------------------|-------------------------|-----|----------|---------------|

| $V_{IH}$     | 高电平输入电压           | $V_{DD} = 5.25\text{V}$                                                | ●                       | 2.4 |          | V             |

| $V_{IL}$     | 低电平输入电压           | $V_{DD} = 4.75\text{V}$                                                | ●                       |     | 0.8      | V             |

| $I_{IN}$     | 数字输入电流            | $V_{IN} = 0\text{V}$ 至 $V_{DD}$                                        | ●                       |     | $\pm 10$ | $\mu\text{A}$ |

| $C_{IN}$     | 数字输入电容            | 仅 $\overline{\text{MSB}}\text{IN}$ 和 $\overline{\text{OE}}$            |                         | 1.5 |          | pF            |

| $V_{OH}$     | 高电平输出电压           | $0V_{DD} = 4.75\text{V}$                                               | $I_Q = -10\mu\text{A}$  |     | 4.74     | V             |

|              |                   |                                                                        | $I_Q = -200\mu\text{A}$ | ●   | 4        | V             |

| $V_{OL}$     | 低电平输出电压           | $0V_{DD} = 4.75\text{V}$                                               | $I_Q = 160\mu\text{A}$  |     | 0.05     | V             |

|              |                   |                                                                        | $I_Q = 1.6\text{mA}$    | ●   | 0.1 0.4  | V             |

| $I_{OZ}$     | 高阻抗输出漏电流 D13 至 D0 | $V_{OUT} = 0\text{V}$ 至 $V_{DD}$ , $\overline{\text{OE}} = \text{高电平}$ | ●                       |     | $\pm 10$ | $\mu\text{A}$ |

| $C_{OZ}$     | 高阻抗输出电容 D13 至 D0  | $\overline{\text{OE}} = \text{高电平}$ (注 8)                              | ●                       |     | 15       | pF            |

| $I_{SOURCE}$ | 输出源电流             | $V_{OUT} = 0\text{V}$                                                  |                         |     | -50      | mA            |

| $I_{SINK}$   | 输出吸收电流            | $V_{OUT} = 5\text{V}$                                                  |                         |     | 50       | mA            |

功率要求 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。(注 5)

| 符号        | 参数       | 条件 | 最小值 | 典型值  | 最大值      | 单位 |

|-----------|----------|----|-----|------|----------|----|

| $V_{DD}$  | 正电源电压    |    |     | 4.75 | 5.25     | V  |

| $I_{DD}$  | 正电源电流    |    | ●   | 245  | 300      | mA |

| $P_{DIS}$ | 功耗       |    | ●   | 1.2  | 1.5      | W  |

| $0V_{DD}$ | 数字输出电源电压 |    |     | 0.5  | $V_{DD}$ | V  |

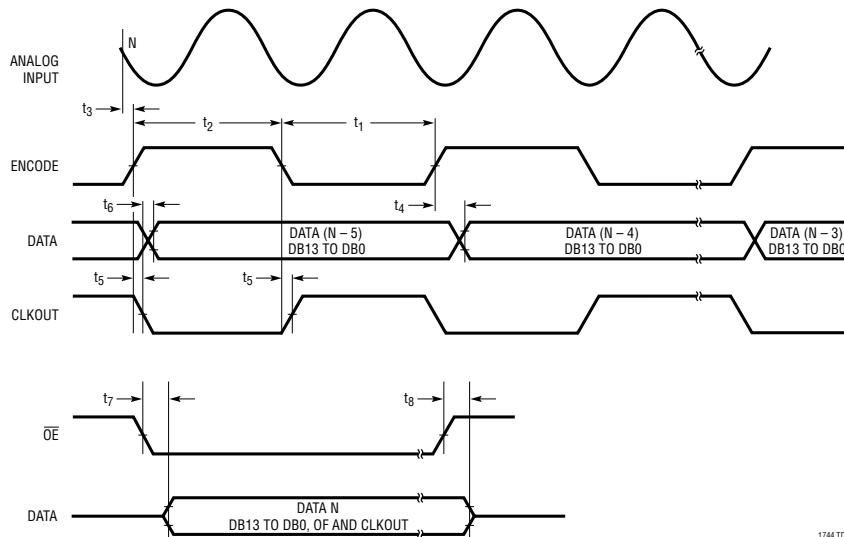

定时特性 凡标注●表示该指标适合整个工作温度范围，否则仅指  $T_A = 25^\circ\text{C}$ 。(注 5)

| 符号                       | 参数                                             | 条件                        | 最小值 | 典型值 | 最大值     | 单位  |

|--------------------------|------------------------------------------------|---------------------------|-----|-----|---------|-----|

| $t_{\text{SAMPLE(MAX)}}$ | 最大采样频率                                         |                           | ●   | 50  |         | MHz |

| $t_1$                    | ENC 低电平时间                                      | (注 9)                     | ●   | 9.5 | 10 1000 | ns  |

| $t_2$                    | ENC 高电平时间                                      | (注 9)                     | ●   | 9.5 | 10 1000 | ns  |

| $t_3$                    | 采样及保持的孔径延迟                                     |                           |     | 0   |         | ns  |

| $t_4$                    | ENC 至数据延迟                                      | $C_L = 10\text{pF}$ (注 8) | ●   | 1.4 | 4.5 8   | ns  |

| $t_5$                    | ENC 至 $\overline{\text{CLKOUT}}$ 延迟            | $C_L = 10\text{pF}$ (注 8) | ●   | 0.5 | 2.3 5   | ns  |

| $t_6$                    | $\overline{\text{CLKOUT}}$ 至数据延迟               | $C_L = 10\text{pF}$ (注 8) | ●   | 0   | 2.2     | ns  |

| $t_7$                    | $\overline{\text{OE}} \downarrow$ 后的 DATA 存取时间 | $C_L = 10\text{pF}$ (注 8) |     |     | 10 25   | ns  |

| $t_8$                    | BUS 释放时间                                       | (注 8)                     |     |     | 10 25   | ns  |

|                          | 数据延时                                           |                           |     |     | 5       | 周期  |

注 1：绝对最大额定值是指超出该值则器件的寿命可能会受损。

注 2：所有的电压值均以标有 GND 的地电位为基准 (除非另外注明)。

注 3：当这些引脚电压在 GND 以下或在  $V_{DD}$  以上时，它们将被内部二极管所箝位。在 GND 以下或在  $V_{DD}$  以上，本产品能处理大于 100mA 的输入电流，且不会发生闭锁。

注 4：当这些引脚的电压低于 GND 时，它们将被内部二极管所箝位。在 GND 以下，本产品能在不发生闭锁的情况下处理大于 100mA 的输入电流。这些引脚未被箝位至  $V_{DD}$ 。

注 5： $V_{DD} = 5\text{V}$ ,  $f_{\text{SAMPLE}} = 50\text{MHz}$ , 差分  $\text{ENC}/\overline{\text{ENC}} = 2V_{\text{PP}} 50\text{MHz}$  正弦波，输入范围 =  $\pm 1.6\text{V}$  差分，除非特别注明。

注 6：积分非线性被定义为一个代码相对一根穿过转移函数曲线实际端点的直线的偏离程度。该偏离是以量化频带的中心为起点进行测量的。

注 7：双极偏移是输出代码在 00 0000 0000 0000 和 11 1111 1111 1111 之间摆动时从 -0.5LSB 所测得的偏移电压。

注 8：由设计提供保证，未经测试。

注 9：推荐的工作条件。

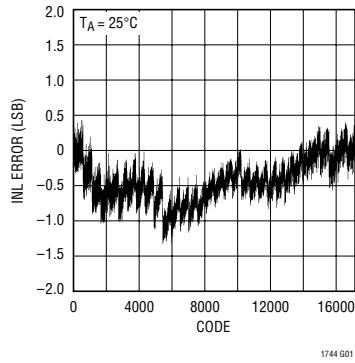

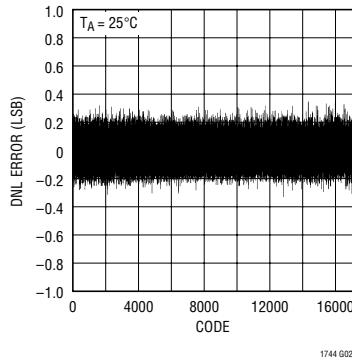

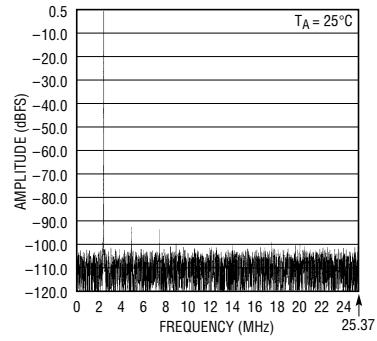

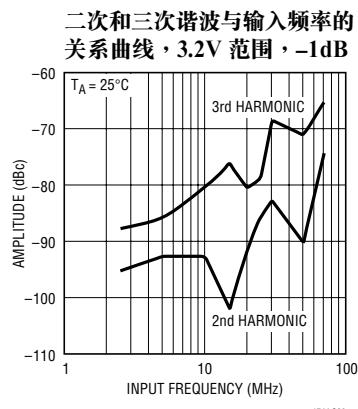

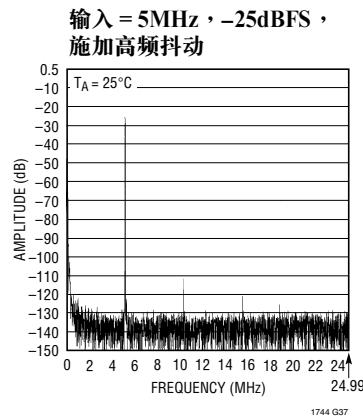

## 典型性能特征 (注5)

典型 INL, 3.2V 范围

典型 DNL, 3.2V 范围

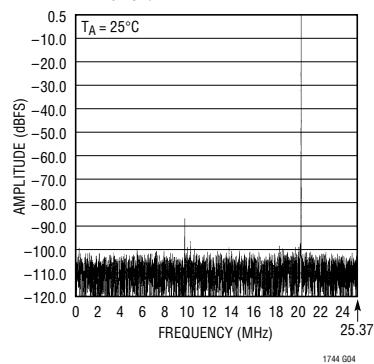

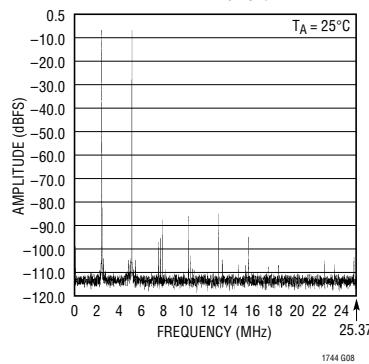

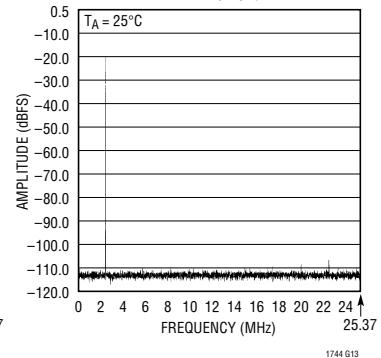

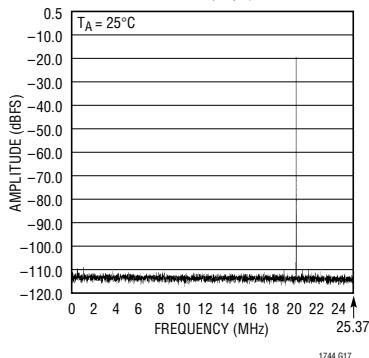

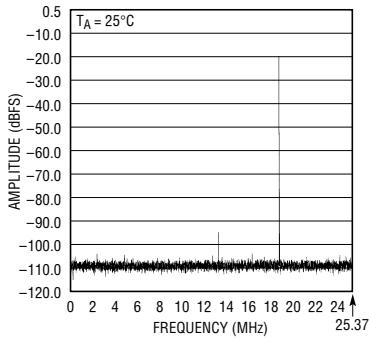

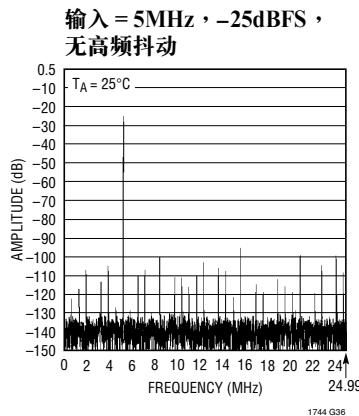

非平均, 8192 点 FFT,

输入频率 = 2.5MHz, -1dB,

2V 范围

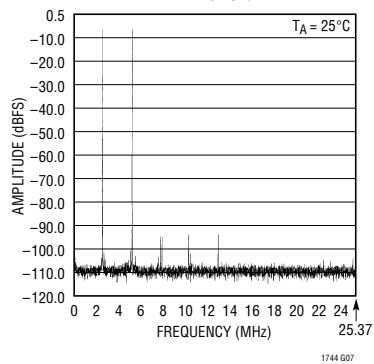

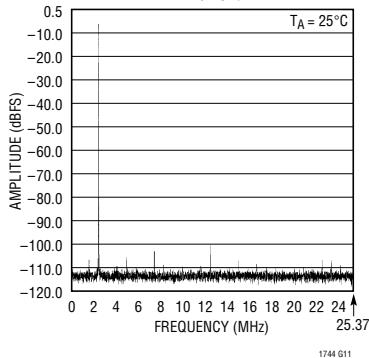

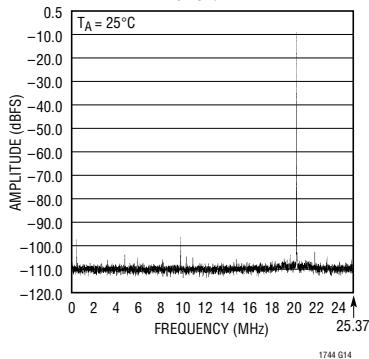

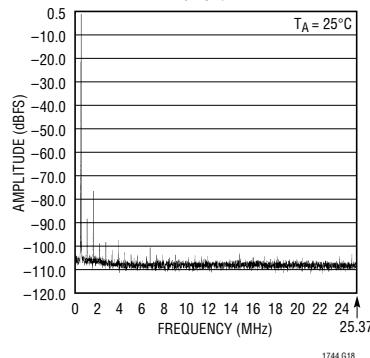

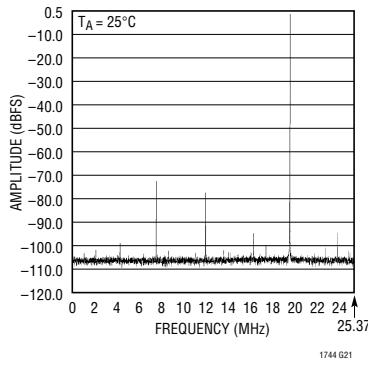

非平均, 8192 点 FFT,

输入频率 = 20MHz, -1 dB,

2V 范围

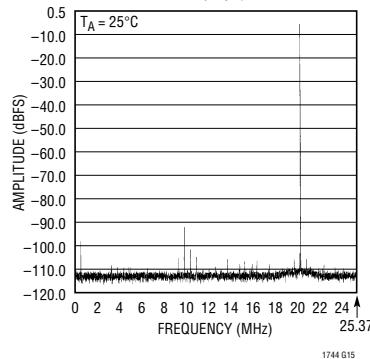

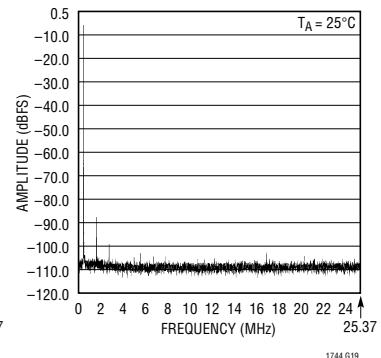

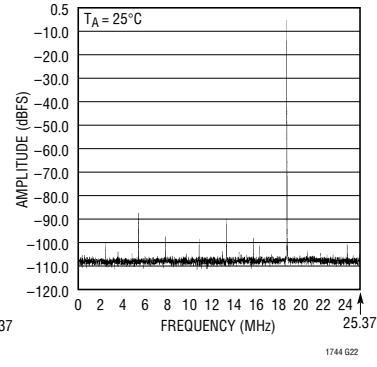

取平均, 8192 点双音 FFT,

输入频率 = 2.5MHz 和

5.2MHz, 2V 范围

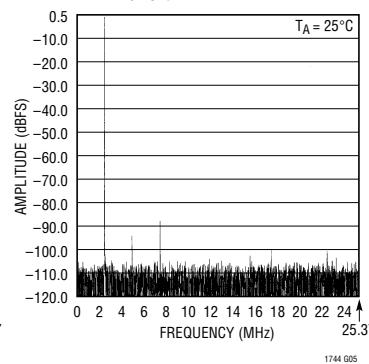

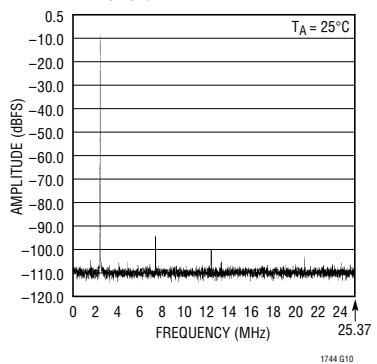

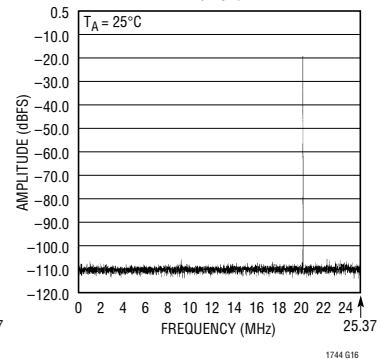

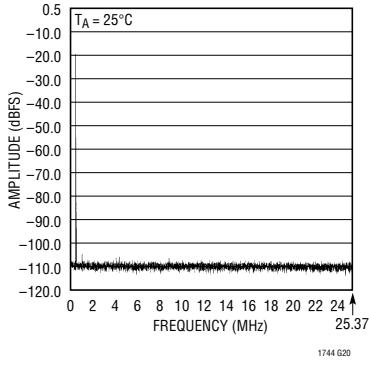

非平均, 8192 点 FFT,

输入频率 = 2.5MHz, -1 dB,

3.2V 范围

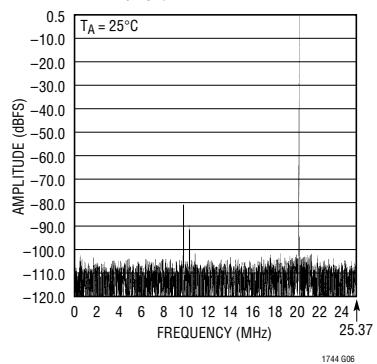

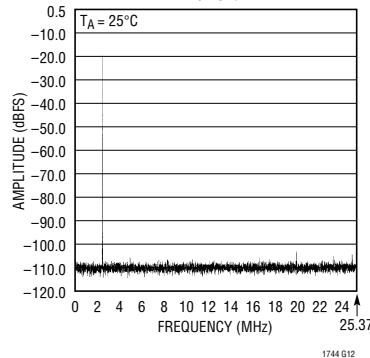

非平均, 8192 点 FFT,

输入频率 = 20MHz, -1 dB,

3.2V 范围

取平均, 8192 点双音 FFT,

输入频率 = 2.5MHz 和

5.2MHz, 3.2V 范围

取平均, 8192 点 FFT,

输入频率 = 2.5MHz, -6dB,

2V 范围

## 典型性能特征 (注5)

取平均, 8192 点 FFT,

输入频率 = 2.5MHz,

-6dB, 3.2V 范围

取平均, 8192 点 FFT,

输入频率 = 2.5MHz,

-20dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 2.5MHz,

-20dB, 3.2V 范围

取平均, 8192 点 FFT,

输入频率 = 20MHz,

-6dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 20MHz,

-6dB, 3.2V 范围

取平均, 8192 点 FFT,

输入频率 = 20MHz,

-20dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 20MHz,

-20dB, 3.2V 范围

取平均, 8192 点 FFT,

输入频率 = 51MHz,

-1dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 51MHz,

-6dB, 2V 范围

## 典型性能特征 (注5)

取平均, 8192 点 FFT,

输入频率 = 51MHz,

-20dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 70MHz,

-20dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 70MHz,

-1dB, 2V 范围

取平均, 8192 点 FFT,

输入频率 = 70MHz,

-6dB, 2V 范围

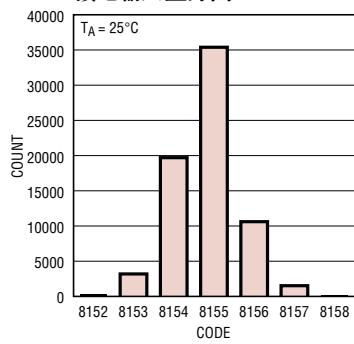

### 接地输入直方图

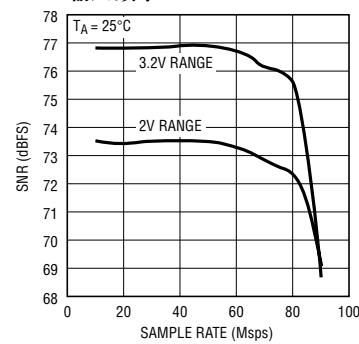

SNR 与采样率的关系曲线,

输入频率 = 5MHz, -1dB

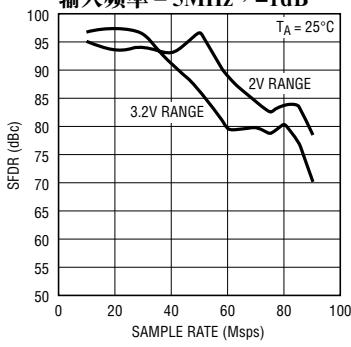

SFDR 与采样率的关系曲线,

输入频率 = 5MHz, -1dB

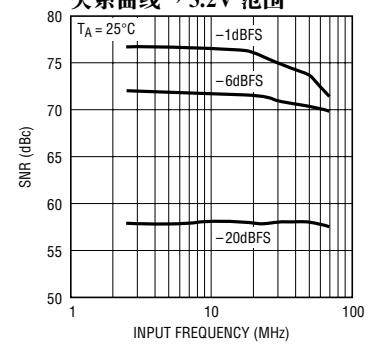

SNR 与输入频率和幅度的

关系曲线, 3.2V 范围

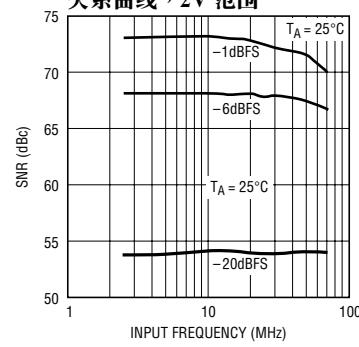

SNR 与输入频率和幅度的

关系曲线, 2V 范围

## 典型性能特征 (注5)

## 典型性能特征 (注5)

## 引脚功能

**SENSE (引脚 1)**：基准检测引脚。地选择  $\pm 1V$ 。 $V_{DD}$  选择  $\pm 1.6V$ 。当加在 SENSE 引脚上的电压高于  $1V$  且低于  $1.6V$  时，选择  $\pm V_{SENSE}$  的输入范围， $\pm 1.6V$  为最大有效输入范围。

**$V_{CM}$  (引脚 2)**：2.5V 输出和输入共模偏压。通过  $4.7\mu F$  陶瓷片式电容器旁路至地。

**GND (引脚 3、6、9、12、13、16、19、21、36、37)**：ADC 电源地。

**$A_{IN}^+$  (引脚 4)**：正差分模拟输入。

**$A_{IN}^-$  (引脚 5)**：负差分模拟输入。

**$V_{DD}$  (引脚 7、8、17、18、20)**：5V 电源。通过  $1\mu F$  陶瓷片式电容器旁路至 AGND。

**REFLB (引脚 10)**：ADC 低电平基准。通过  $0.1\mu F$  陶瓷片式电容器旁路至引脚 11。不要连接至引脚 14。

**REFHA (引脚 11)**：ADC 高电平基准。通过  $0.1\mu F$  陶瓷片式电容器旁路至引脚 10、通过一个  $4.7\mu F$  陶瓷电容器旁路至引脚 14，并通过  $1\mu F$  陶瓷电容器旁路至地。

**REFLA (引脚 14)**：ADC 低电平基准。通过  $0.1\mu F$  陶瓷片式电容器旁路至引脚 15、通过一个  $4.7\mu F$  陶瓷电容器旁路至引脚 11，并通过  $1\mu F$  陶瓷电容器旁路至地。

**REFHB (引脚 15)**：ADC 高电平基准。通过  $0.1\mu F$

陶瓷片式电容器旁路至引脚 14。不要连接至引脚 11。

**MSBINV (引脚 22)**：MSB 反转控制。低电平使 MSB 发生反转，这是二进制补码输出格式。高电平不会使 MSB 发生反转，这是偏移二进制输出格式。

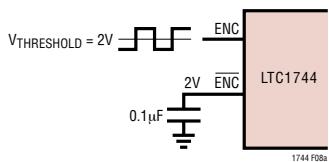

**ENC (引脚 23)**：编码输入。输入采样始自正边沿。

**$\overline{ENC}$  (引脚 24)**：编码补码输入。转换操作始自负边沿。对于单端编码信号，通过  $0.1\mu F$  陶瓷电容器旁路至地。

**$\overline{OE}$  (引脚 25)**：输出使能。低电平使能输出。逻辑高电平使输出呈高阻抗。

**CLKOUT (引脚 26)**：数据有效输出。将数据锁定于 CLKOUT 的上升沿。

**OGND (引脚 27、38、47)**：输出驱动器的地。

**D0 至 D3 (引脚 28 至 31)**：数字输出。D0 是 LSB。

**$OV_{DD}$  (引脚 32、43)**：输出驱动器的正电源。通过  $0.1\mu F$  陶瓷片式电容器旁路至地。

**D4 至 D6 (引脚 33 至 35)**：数字输出。

**D7 至 D10 (引脚 39 至 42)**：数字输出。

**D11 至 D13 (引脚 44 至 46)**：数字输出。D13 是 MSB。

**OF (引脚 48)**：溢出/下溢输出。出现溢出或下溢时为高电平。

## 时序图

1744 TD

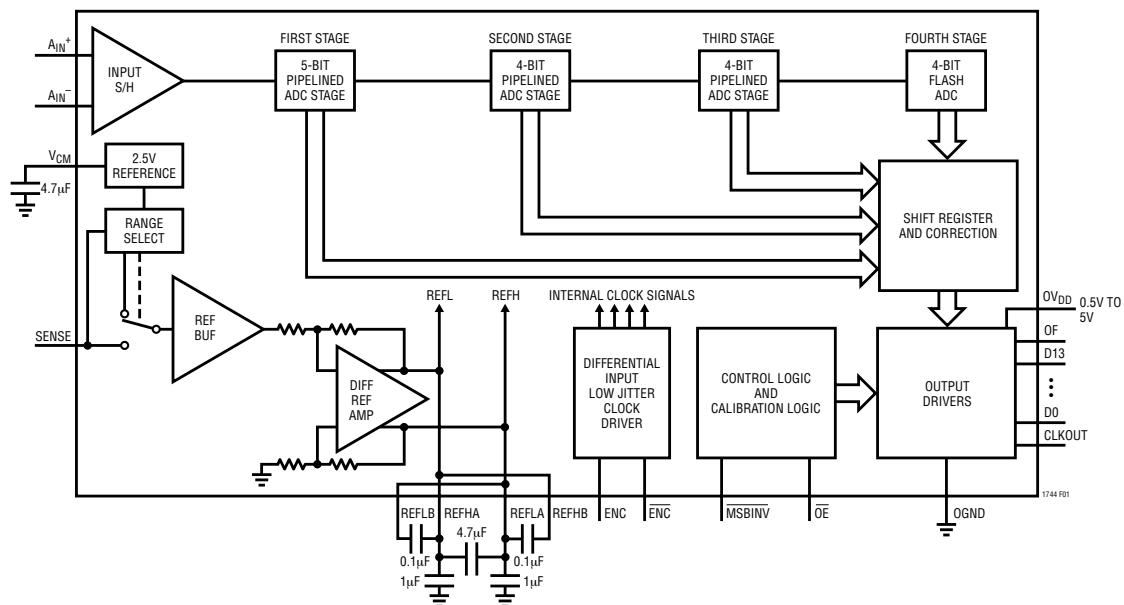

## 功能方框图

## 应用信息

### 动态特性

#### 信号与噪声加失真之比

信号与噪声加失真之比 [S/(N + D)] 是输入基频的 RMS 幅度与 ADC 输出端上所有其他频率分量的 RMS 幅度之比。输出被带限于 DC 至半采样频率之间的范围内。

#### 信噪比

信噪比 (SNR) 是输入基频的 RMS 幅度与除了前五个谐波和 DC 之外的所有其他分量的 RMS 幅度之比。

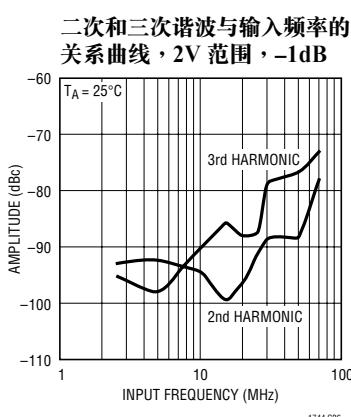

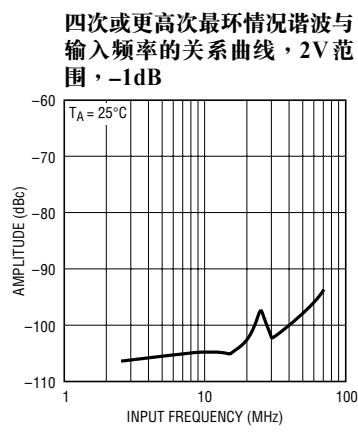

#### 总谐波失真

总谐波失真是输入信号所有谐波的 RMS 之和与基频自身之比。带外谐波混入 DC 与半采样频率之间的频带。THD 由下式来表示：

$$\text{THD} = 20 \log \frac{\sqrt{V2^2 + V3^2 + V4^2 + \dots + Vn^2}}{V1}$$

其中 V1 为基频的 RMS 幅度，V2 至 Vn 为二次至 n 次谐波的幅度。在本数据手册中，THD 的计算采用了高达五次的所有谐波。

#### 交调失真

如果 ADC 输入信号包括一个以上的频谱分量，则除了 THD 之外，ADC 转移函数非线性还有可能产生交调失真 (IMD)。IMD 是在一个正弦输入的改变，这在一个不同频率的另一个正弦输入存在所引起。

如果两个频率分别为  $f_a$  和  $f_b$  的纯正弦波被加到 ADC 输入端上，则 ADC 转移函数中的非线性能在和数频率和差值频率 (即  $m f_a \pm n f_b$ ，其中  $m$  和  $n = 0, 1, 2, 3$  等) 上产生失真分量结果。三阶交调失真分量为  $2f_a + f_b$ 、 $2f_b + f_a$ 、 $2f_a - f_b$  和  $2f_b - f_a$ 。交调失真被定义为其中一个输入音频的 RMS 值与最大的三阶交调失真产品分量的 RMS 值之比。

### 无寄生动态范围 (SFDR)

无寄生动态范围是指峰值谐波或作为除了输入信号和 DC 之外的最大频谱分量的寄生噪声。该数值相对于一个全标度输入信号的 RMS 值，单位为分贝 (dB)。

#### 输入带宽

输入带宽是指在重构基频的幅度减少了 3dB (于一个全标度输入信号) 时的输入频率。

#### 孔径延迟时间

它指的是从一个上升  $\overline{\text{ENC}}$  与 ENC 电压相等到输入信号被采样及保持电路进行保持的时间。

#### 孔径延迟抖动

它指的是各转换之间的孔径延迟时间的变化。当对一个 AC 输入进行采样时，该随机变化将引发噪声。仅存在由抖动所引起的信噪比为：

$$\text{SNR}_{\text{JITTER}} = -20 \log (2\pi) \cdot F_{\text{IN}} \cdot T_{\text{JITTER}}$$

#### 转换操作

如图 1 所示，LTC1744 是一种 CMOS 流水线多级转换器。该转换器具有 4 个流水线 ADC 级；一个采样模拟输入将在 5 个周期之后产生一个数字化值，请参见“时序图”部分。为了提高共模噪声免疫力并使输入范围最大化，采用了差分模拟输入。此外，差分输入驱动将减少采样及保持电路的偶次谐波。为了改善共模噪声免疫力，编码输入也是差分的。

LTC1744 具有两个工作相位，由差分  $\overline{\text{ENC}}/\text{ENC}$  输入引脚的状态所决定。为简短起见，当  $\overline{\text{ENC}}$  为高电平时，本文将参考高于  $\overline{\text{ENC}}$  的 ENC；和当  $\overline{\text{ENC}}$  为低电平时，可参考低于  $\overline{\text{ENC}}$  的 ENC。

图 1 所示的每个流水线级包括一个 ADC、一个重构 DAC 和一个级间余数放大器。在操作中，ADC 对流水线级的输入进行量化，并由 DAC 将量化值从

## 应用信息

输入中减去以生成一个余数。余数由余数放大器来放大并输出。连续级异相操作，这样，当奇数级输出其余数时，偶数级则获取该余数，反之亦然。

当 ENC 为低电平时，模拟输入被直接差分采样至方框图示出的“INPUT S/H”中的输入采样及保持电容器。在 ENC 从低电平瞬变至高电平的瞬间，采样输入被保持。当 ENC 为高电平时，由驱动第一个流水线 ADC 级的 S/H 放大器对保持输入电压进行缓冲。在 ENC 为高电平期间，第一级获得 S/H 的输出。当 ENC 回降至低电平时，第一级产生其余数，该余数被第二级所获得。同时，输入 S/H 返回获取模拟输入的状态。当 ENC 回升至高电平时，第二级产生其余数，该余数被第三级所得。对第三级重复一个相同的过程，生成一个传送至第四级 ADC 以进行最终评估的三级差值信号。

第一级之后的每一个 ADC 级其电压范围都有所增加，以适应强脉冲和放大器失调误差。对产生自所有 ADC 级的结果都进行了数字延迟，以便使这些结果能在被传送至输出缓冲器之前在校正逻辑电路中进行正确的组合。

### 采样/保持操作和输入驱动

#### 采样保持操作

图 2 示出了 LTC1744 CMOS 差分采样及保持的等效电路。差分模拟输入通过 CMOS 传输栅极直接采样至采样电容器 ( $C_{SAMPLE}$ )。对于给定的采样电容器尺寸，这种电容器直接采样能够获得可能的最低噪声水平。图中示出与每个输入端相连的电容器 ( $C_{PARASITIC}$ ) 数值是与每个输入相关联的所有其他电容之和。

在 ENC/ENC 为低电平的采样过程中，传输栅极

图 1：方框图

## 应用信息

图 2：等效输入电路

将模拟输入与采样电容器相连，这些电容器被充电和追踪至差分输入电压，并保持在此电压上。当  $\text{ENC}/\overline{\text{ENC}}$  从低电平瞬变至高电平时，采样输入电压保持在采样电容器。在保持期间，当  $\text{ENC}/\overline{\text{ENC}}$  为高电平时，将采样电容器与输入端断接，保持电压被传送至 ADC 内核以进行处理。当  $\text{ENC}/\overline{\text{ENC}}$  从高电平瞬变至低电平时，输入被重新连接至采样电容器，以获取一个新的采样。由于采样电容器仍然保留著先前的采样，所以此时会产生一个与采样之间的电压变化成正比的充电干扰信号。如果上一个采样和新采样之间的变化不大，则出现于该输入端的充电干扰将较小。如果输入变化很大（例如在输入频率接近奈奎斯特频率时发生的变化），则会产生一个较大的充电干扰。

### 共模偏压

ADC 采样及保持电路要求采用差分驱动来实现规定的性能。对于 3.2V 和 2V 范围，每个输入的摆幅应分别为  $\pm 0.8V$  和  $\pm 0.5V$ （以 2.5V 的共模电压为中心）。 $V_{\text{CM}}$  输出引脚（引脚 2）可被用来提供共模偏压。 $V_{\text{CM}}$  可直接连接至一个变压器中心抽头，以设置 DC 输入电平，或作为一个运放差分驱动器电路的基准电平。 $V_{\text{CM}}$  引脚必须在靠近 ADC 的地方通过  $4.7\mu\text{F}$  或数值更大的电容器旁路至地。

### 输入驱动阻抗

与所有的高性能、高速 ADC 一样，LTC1744 的动态特性也会受到输入驱动电路的影响，特别是二次和三次谐波。源阻抗和输入电抗有可能影响 SFDR。在编码的下降沿，采样及保持电路将把  $7\text{pF}$  采样电容器连接至输入引脚并起动采样周期。当编码上升时，采样周期结束，在采样电容器对采样输入进行保持。理想状况是输入电路的运行速度足够快，以便在  $1/(2F_{\text{ENCODE}})$  的采样周期里对采样电容器进行满充电；然而，并不能做到这一点，而且，不完全的稳定还有可能使 SFDR 特性发生劣化。采样干扰被设计为尽可能得线性，以最大限度地减轻因不完全稳定所带来的影响。

为了获得最佳性能，建议每个输入端具有  $100\Omega$  或更小的源阻抗。源阻抗应与差分输入匹配。如果匹配不良，则将导致产生较高的偶次谐波，尤其是二次谐波。

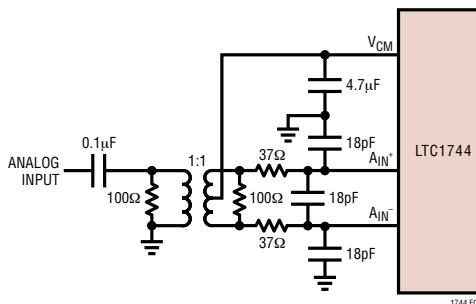

### 输入驱动电路

图 3 示出了采用具有一个带中心抽头的副端绕组的 RF 变压器对 LTC1744 进行驱动的情形。副端绕组的中心抽头上加有大小为  $V_{\text{CM}}$  的 DC 偏压，从而将 ADC 输入信号设定于其最佳 DC 电平上。图 3 示出了一种匝数比为 1:1 的变压器。对于每个 ADC 输

## 应用信息

入，如果 ADC 的源阻抗不超过  $100\Omega$ ，则可采用其他的匝数比。采用变压器的一个缺陷是低频响应的损失。在低于  $1\text{MHz}$  的频率条件下，大多数小型 RF 变压器的性能都很差。

图 3：采用一个变压器的单端至差分转换

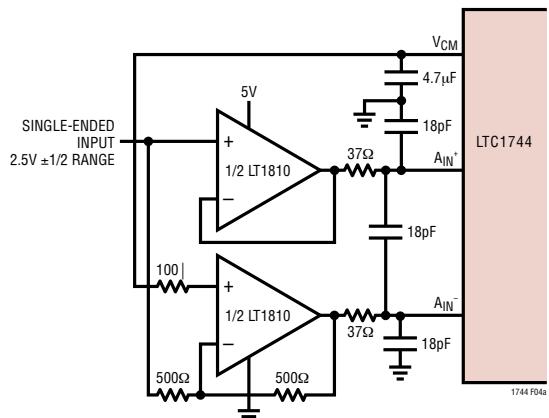

图 4a 示出了采用运算放大器来把一个单端输入信号转换为差分输入信号的情况。该方法的优点是提供了低频输入响应；然而，大多数运放所具有的有限增益带宽将在高输入频率条件下对 SFDR 产生制约。

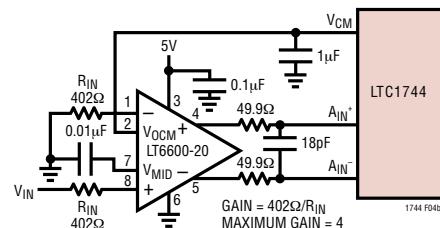

图 4b 示出了被用作一个输入驱动器的低噪声差分放大器和低通滤波器 LT6600。LT6600 具备两项功能：即 4 阶低通滤波器以及单端至差分转换器。此外，还可以通过一个外部电阻器来对其进行设置，以便提供一倍数值为 1 至 4 的增益。该器件有三个版本，分别具有  $2.5\text{MHz}$ 、 $10\text{MHz}$  或  $20\text{MHz}$  的低通滤波带宽。

模拟输入端上的  $37\Omega$  电阻器和  $18\text{pF}$  电容器有两个作用：即把驱动电路与采样及保持充电干扰隔离开，以及对转换器输入端上的宽带噪声进行限制。对于  $40\text{MHz}$  以上的输入频率，有可能需要减少电容器的数目以防止信号过大损失。

### 基准操作

如图 5 所示，LTC1744 的基准电路包括一个  $2.5\text{V}$

图 4a：采用运放的差分驱动

图 4b：采用 LT6600 作为一个差分驱动器

带隙基准、一个差分放大器以及开关和控制电路。内部电压基准可针对  $2\text{V}$  ( $\pm 1\text{V}$  差分) 或  $3.2\text{V}$  ( $\pm 1.6\text{V}$  差分) 这两种引脚可选输入范围进行配置。将 SENSE 引脚连接至地选择  $2\text{V}$  范围；而把 SENSE 引脚连接至  $V_{DD}$  则选择  $3.2\text{V}$  范围。

$2.5\text{V}$  带隙基准有两项作用：其输出提供了一个用于设定任何外部输入电路的共模电压 DC 偏压点；另外，该基准还与一个差分放大器一道被用来生成内部 ADC 电路所需的差分基准电平。

$2.5\text{V}$  基准输出  $V_{CM}$  需要一个  $4.7\mu\text{F}$  或更大的外部旁路电容器。它可为内部和外部电路提供一条通向地的高频低阻抗路径，同时也是用于该基准的补

## 应用信息

偿电容器。若没有此电容器，则不会稳定。

差分放大器为 ADC 生成高电平和低电平基准。高速开关电路与这些输出相连且必须被外部旁路。每个输出都有两个引脚：即用于高电平基准的 REFHA 和 REFHB，以及用于低电平基准的 REFLA 和 REFLB。需要两倍的输出引脚以减小封装电感。旁路电容器应按图 5 所示进行连接。

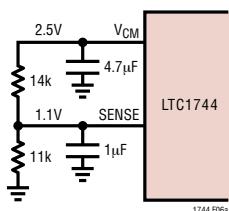

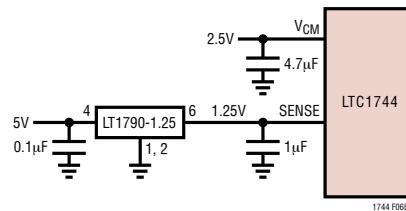

如图 6a 所示，可通过两个外部电阻器来设置介

于两个引脚可选输入范围之间的其他电压范围。可以采用一个外部基准，方法是将其输出直接或通过一个阻性分压器加至 SENSE 引脚。建议不要采用一个逻辑器件来驱动 SENSE 引脚，因为逻辑门限接近地电位和  $V_{DD}$ 。SENSE 引脚应与高电平或低电平相连，并尽可能地靠近转换器。如果 SENSE 引脚被外部驱动，则应在尽可能靠近器件的地方通过一个  $1\mu F$  陶瓷电容器旁路至地。

图5：等效的基准电路

图 6a : 2.2V 范围的 ADC

图 6b：采用一个外部基准的 2.5V 范围的 ADC

## 应用信息

### 输入范围

可根据具体应用来设定输入范围。对于输入频率较低(<10MHz)的过采样信号处理，采用最大输入范围能在保持优越的SFDR特性的同时实现最佳的信噪比性能。对于高输入频率(>10MHz)，采用2V输入范围将能够获得最佳的SFDR特性，但SNR将下降3.5dB。请参见“典型性能特征”部分。

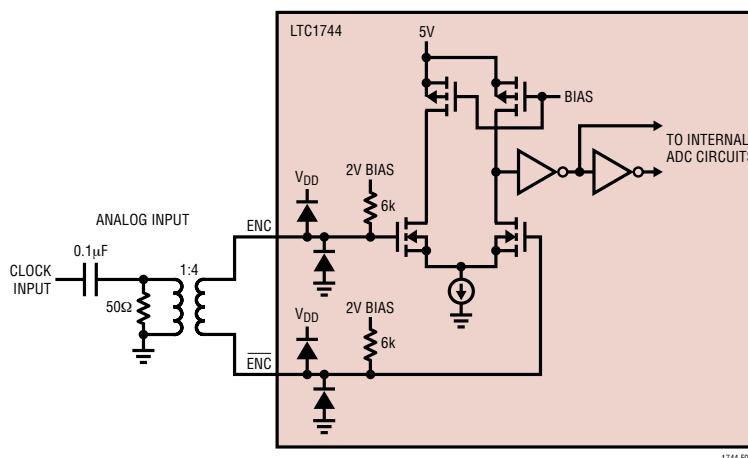

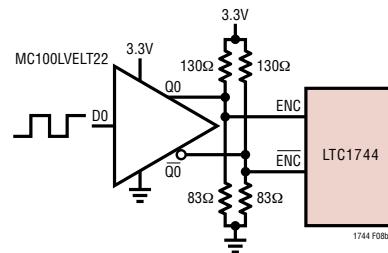

### 驱动编码输入

LTC1744的噪声特性对编码信号质量的依赖程度并不亚于在模拟输入。有意对ENC/ $\overline{ENC}$ 输入进行差分驱动，这样做主要是为了获得从共模噪声源的噪声免疫力。通过一个6k电阻器给每个输入施加一个2V偏压。该偏压电阻为变压器耦合驱动电路设定了DC工作点，并可为单端驱动电路设定逻辑门限。

图7：变压器驱动的ENC/ $\overline{ENC}$

## 应用信息

编码信号上的任何噪声都将产生额外的孔径抖动，这将与 ADC 固有孔径抖动进行 RMS 叠加。

在抖动至关重要的应用 (高输入频率) 中，应考虑下列事项：

1. 应采用差分驱动。

2. 采用尽可能大的幅度；如果耦合变压器采用较高的匝数比来增加幅度。

3. 如果 ADC 与一个正弦信号同步，则应对 ENCODE 信号进行滤波，以降低宽带噪声。

4. 使两个 ENCODE 输入端上的电容和串联电阻达到平衡，这样，任何耦合噪声都将以共模噪声出现于这两个输入端。

编码输入具有一个 1.8V 至  $V_{DD}$  的共模电压范围。对于单端驱动，可在地电位至  $V_{DD}$  的范围内对每个输入进行驱动。

图 8a：单端 ENCODE 驱动，建议不要在低抖动条件下使用

### 最大和最小编码率

LTC1744 的最大编码率为 50Msps。为使 ADC 正确操作，ENCODE 信号应具有一个 50% (±5%) 的占空比。每半个周期都必须有至少 9.5ns 的时间以使 ADC 内部电路能够获得足够的稳定时间，从而实现正确的操作。借助采用一个变压器或对称差分逻辑 (例如 PECL 或 LVDS) 的差分正弦驱动，即可容易地获得一个精准的 50% 占空比。当采用一个单端 ENCODE 信号时，不对称的上升和下降时间有可能产生与 50% 相去甚远的占空比。

在低于 50Msps 的采样率条件下，只要每半个周期的时间不少于 9.5ns，则占空比可以从 50% 改变。

LTC1744 采样率的下限由采样及保持电路的压降来决定。该 ADC 的流水线架构依靠在小值电容器上存储的模拟信号。结点泄漏将使电容器放电。LTC1744 规定的最小工作频率为 1Msps。

图 8b：采用一个 CMOS 至 PECL 变换器的 ENCODE 驱动

应用信息

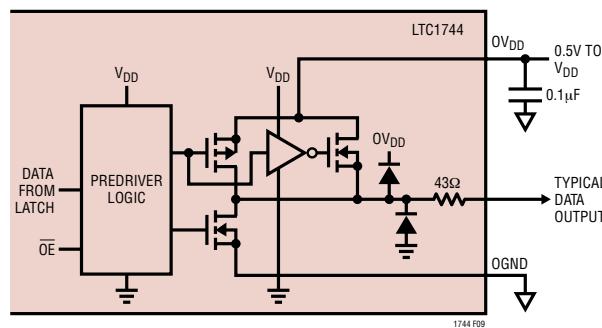

## 数字输出

## 数字输出缓冲器

图 9 示出了一个单输出缓冲器的等效电路。每个缓冲器由  $OV_{DD}$  和  $OGND$  来供电，并与 ADC 电源和地隔离。输出驱动器中的附加 N 沟道晶体管容许低电压条件下的操作。与输出相串联的内部电阻器使得输出表现为至外部电路的  $50\Omega$  电阻，并可免除增设外部阳尼申阻器之需。

## 输出加载

与所有的高速/高分辨率转换器一样，数字输出加载有可能对性能产生影响。LTC1744 的数字输出应驱动一个最小的容性负载，以避免数字输出和敏感输入电路之间可能发生的干扰。应采用一个诸如 ALVCH16373 CMOS 锁存器这样的器件来对输出进行缓冲。为实现全速操作，应将容性负载保持在  $10\text{pF}$  以下。可以采用一个与输出相串联的电阻器，但不是要求这样做，原因是该 ADC 具有一个  $43\Omega$  的片上串联阻尼器。

较低的 OV<sub>DD</sub> 电压还将有助于减轻来自数字输出的干扰。

## 格式

对于偏移二进制或二进制补码格式，可选择 LTC1744 并行数字输出。利用  $\overline{\text{MSBINV}}$  引脚来选择格式；当该引脚为高电平时，选择偏移二进制。

### 溢出位

一个溢出输出位指示何时转换器过范围或欠范围。当OF输出一个逻辑高电平信号时，转换器要么过范围，要么欠范围。

### 输出时钟

该 ADC 具有一个可作为数字输出的  $\overline{ENC}$  输入的延迟信号 CLKOUT。CLKOUT 引脚可被用来使转换器数据同步于数字系统。当采用一个正弦 ENCODE 信号时，这是必需的。数据将在 CLKOUT 下降之后立即被更新，且可被锁定于 CLKOUT 的上升沿。

图9：一个数字输出缓冲器的等效电路

## 应用信息

### 输出驱动器功率

分离的输出电源和接地引脚允许输出驱动器与模拟电路隔离。数字输出缓冲器的电源  $OV_{DD}$  应连接至驱动逻辑电路所用的同一电源。例如，若转换器正在驱动一个由 3V 电源供电的 DSP，则  $OV_{DD}$  应被连接至同一个 3V 电源。可采用高至 5V 的任何电压来为  $OV_{DD}$  供电。逻辑输出将 OGND 和  $OV_{DD}$  之间摆动。

### 输出使能

可采用输出使能引脚  $\overline{OE}$  来禁止输出。 $\overline{OE}$  引脚为低电平时，包括 OF 和 CLKOUT 在内的所有数据输出都被禁止。数据存取和总线释放时间过长，使得输出无法在全速操作期间被使能和禁止。输出高阻抗状态准备在长期的非工作状态下使用。

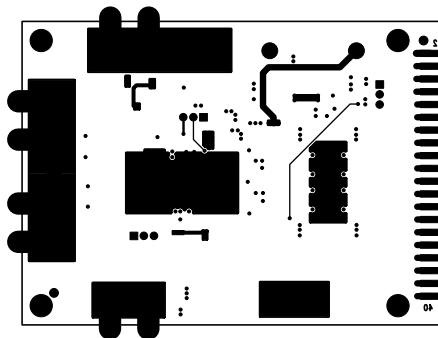

### 接地和旁路

LTC1744 要求采用一个具有干净、完整接地平面的印刷电路板。建议采用带有一个内部接地平面的多层电路板。LTC1744 的引脚专为一种直通式电路板布局进行了优化，从而最大限度地减轻了输入和数字输出之间的干扰。印刷电路板的布局应确保数字和模拟信号线是尽可能分开的。应特别注意不要沿著一条模拟信号迹线或在 ADC 的下方排布任何的数字信号走线。

如本数据手册首页上的方框图所示，应在  $V_{DD}$ 、 $V_{CM}$ 、REFHA、REFHB、REFLA 和 REFLB 引脚上采用高质量的陶瓷旁路电容器。旁路电容器必须放置在尽可能靠近器件引脚的地方。REFHA 和 REFLB 之间以及 REFHB 和 REFLA 之间的电容器尤其重要。

这些电容器应尽可能靠近器件放置(间距在 1.5mm 以内)。推荐使用 0402 型陶瓷电容器。REFHA 和 REFLA 之间的  $4.7\mu F$  大电容器可放置在离器件稍远一些的地方。连接各引脚与旁路电容器的走线必须简短且尽可能宽阔。

LTC1744 的差分输入应并行布置且彼此靠近。输入走线应尽可能简短以使电容最小化，并最大限度地减少噪声拾拾。

应采用一个与数字处理系统地分开的模拟接地平面。所有带 GND 标记的 ADC 地引脚应连接至该平面。ADC 的所有  $V_{DD}$  旁路电容器、基准旁路电容器和输入滤波电容器应连接至该模拟接地平面。LTC1744 具有三个输出驱动器接地引脚，标记为 OGND (引脚 27、38 和 47)。这些地应连接至数字处理系统地。输出驱动器电源  $OV_{DD}$  应连接至数字处理系统电源。 $OV_{DD}$  旁路电容器应旁路至数字系统地。数字处理系统地应连接至位于 ADC 的 OGND (引脚 38) 上的模拟平面。

### 热传递

LTC1744 产生的大部分热量都通过封装引脚从芯片传递到印刷电路板上。特别是接地引脚 12、13、36 和 37 与芯片固定衬垫之间采用了熔丝连接。这些引脚具有最低的芯片至外部环境热阻。关键是所有的接地引脚都应与一个面积足够大的接地平面相连。下一页所给出的评估电路板布局利用多个靠近接地引脚的通孔，获得了一条通往内部接地平面的低热阻通路。借助如此大小的接地平面可获得  $35^{\circ}C/W$  的芯片至环境热阻。若接地平面面积较小或接地引脚连接不良将导致热阻增加。

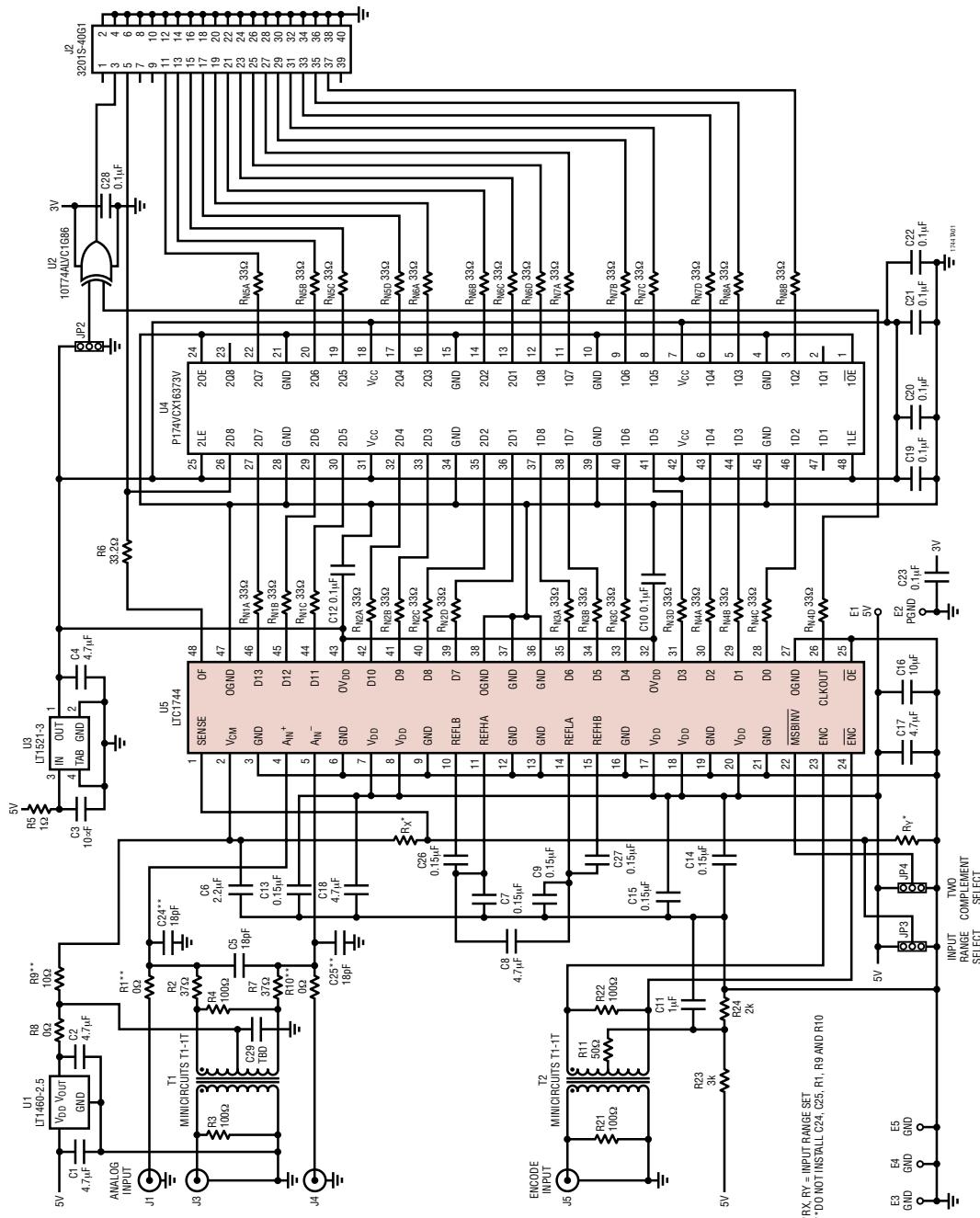

## 应用信息

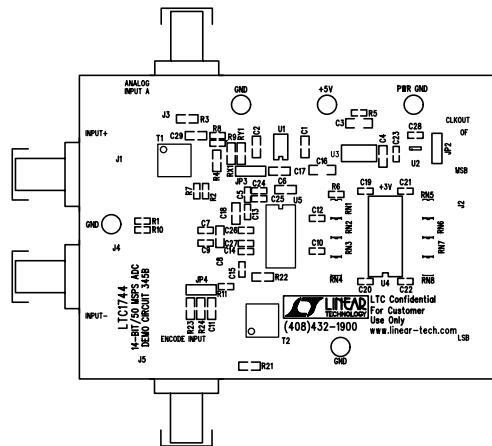

\*RX, RY = INPUT RANGE SET

\*\*DO NOT INSTALL C24, C25, R1, R9 AND R10

## 应用信息

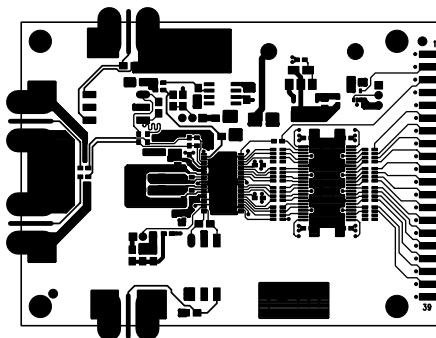

顶侧丝网印刷

顶侧铜板层

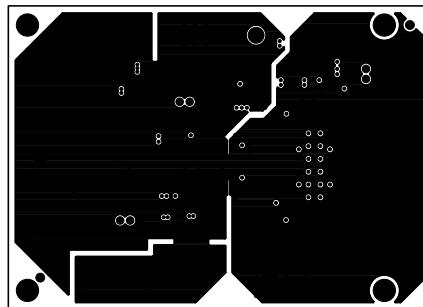

接地平面, 第二层

## 应用信息

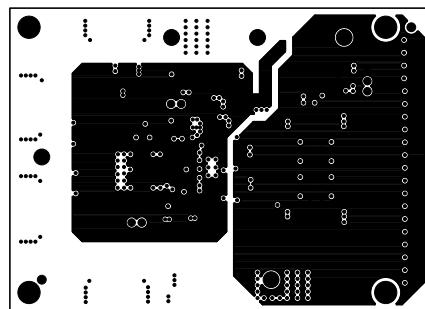

分离的电源平面，第三层

底侧铜板，第四层

## 应用信息

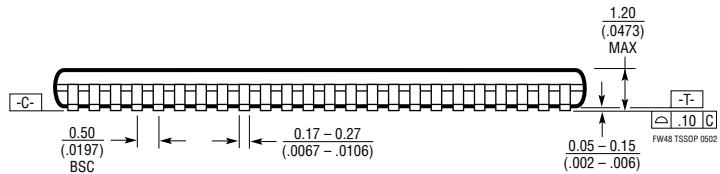

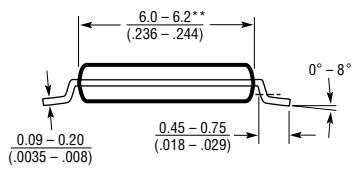

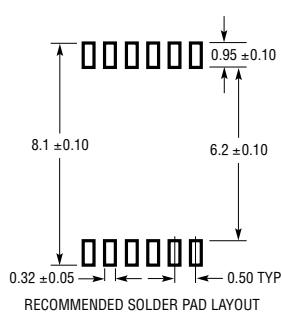

## FW 封装

## 48 引脚塑料 TSSOP 封装 (6.1mm)

(参考 LTC DWG # 05-08-1651)

## NOTE:

1. CONTROLLING DIMENSION: MILLIMETERS

2. DIMENSIONS ARE IN MILLIMETERS

(INCHES)

3. DRAWING NOT TO SCALE

\*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .152mm (.006") PER SIDE

\*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED .254mm (.010") PER SIDE

## 相关器件

| 器件型号                 | 描述                           | 备注                                                |

|----------------------|------------------------------|---------------------------------------------------|

| LT <sup>®</sup> 1019 | 精准带隙基准                       | 0.05% 最大初始准确度, 5ppm/°C 最大漂移                       |

| LTC1196              | 8 位、1Msps ADC                | 3V 至 5V, SO-8 封装                                  |

| LTC1405              | 具并行输出的 12 位、5Msps 采样 ADC     | 与 LTC1420 引脚兼容                                    |

| LTC1406              | 8 位、20Msps ADC               | 高至 70MHz 输入频率的欠采样能力                               |

| LTC1411              | 14 位、2.5Msps ADC             | 无流水过程延迟、5V、80dB SINAD                             |

| LTC1410              | 12 位、1.25Msps ADC            | ±5V、71dB SINAD                                    |

| LTC1412              | 具并行输出的 12 位、3Msps、采样 ADC     | ±5V、无流水过程延迟, 在奈奎斯特频率 (Nyquist) 条件下 SINAD = 72dB   |

| LTC1414              | 14 位、2.2Msps ADC             | ±5V、无流水过程延迟、80dB SINAD、95dB SFDR                  |

| LTC1415              | 具并行输出的单 5V、12 位、1.25Msps ADC | 55mW 功耗, 72dB SINAD                               |

| LTC1419              | 14 位、800ksps ADC             | ±5V、95dB SFDR、150mW                               |

| LTC1420              | 12 位、10Msps ADC              | 在奈奎斯特频率条件下 SINAD 为 71dB、SFDR 为 83dB               |

| LT1460               | 微功率精准系列基准                    | 0.075% 准确度, 10ppm/°C 漂移                           |

| LTC1604/LTC1608      | 16 位、333ksps/500ksps ADC     | 16 位、无漏失码、90dB SINAD、-100dB THD                   |

| LTC1668              | 16 位、50Msps DAC              | 在 1MHz f <sub>OUT</sub> 条件下 SFDR 为 87dB, 低功率, 低成本 |

| LTC1741              | 12 位、65Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |

| LTC1742              | 14 位、65Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |

| LTC1743              | 12 位、50Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |

| LTC1745              | 12 位、25Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |

| LTC1746              | 14 位、25Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |

| LTC1747              | 12 位、80Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |

| LTC1748              | 14 位、80Msps、低噪声 DAC          | 与 LTC1744 引脚兼容                                    |