### 概要

2个对称的 600MHz 高性能 Blackfin 内核

328K Bytes 片内存储器

每个 Blackfin 内核包括：

2 个 16 位 MAC, 2 个 40 位 ALU, 4 个 8 位视频 ALU, 以及 1 个 40 位移位器

RISC 式寄存器和指令模型, 编程简单, 编译环境友好

先进的调试、跟踪和性能监视

内核电压 0.8V-1.2V, 片内调压器可调

兼容 3.3V 及 2.5V I/O

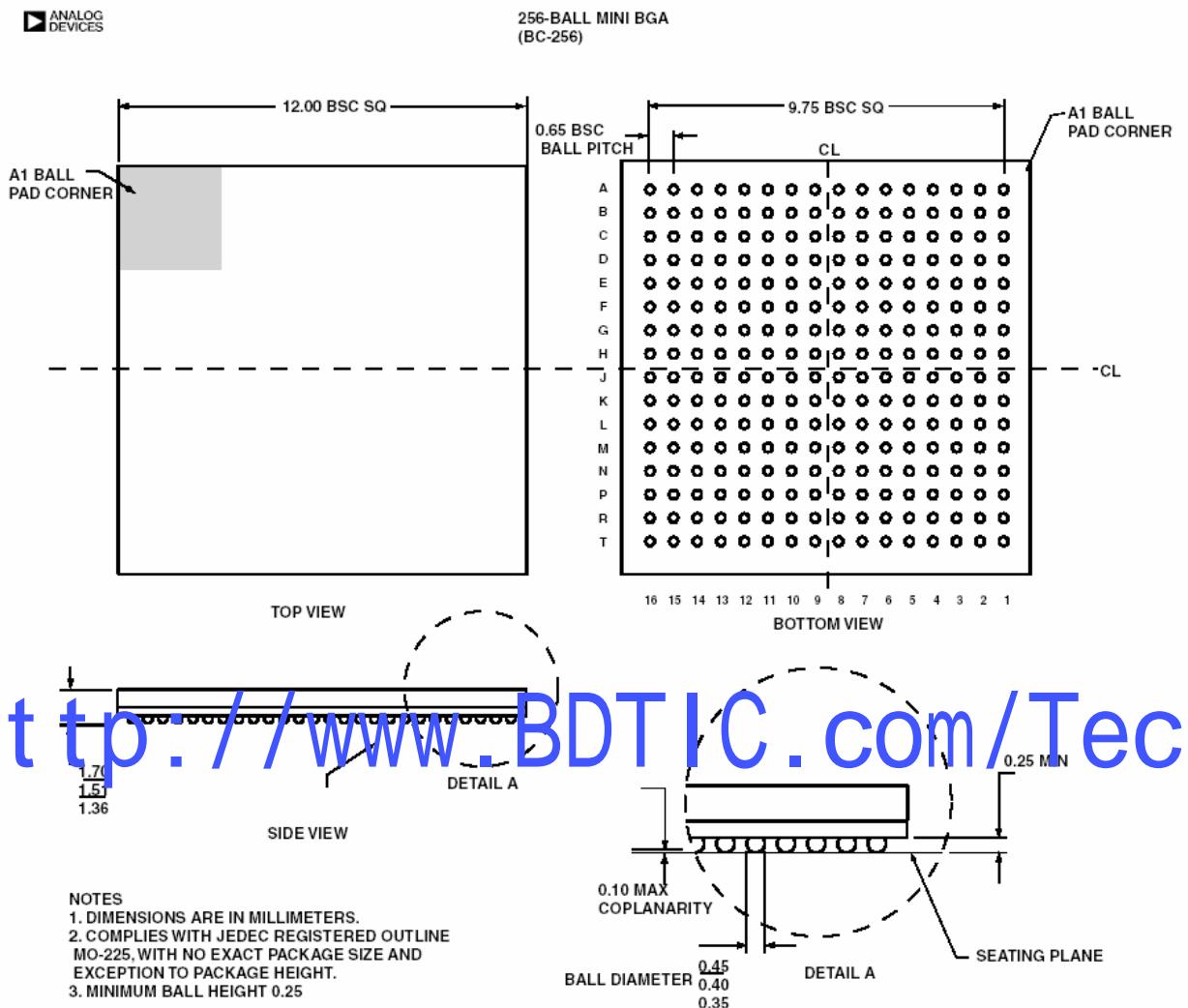

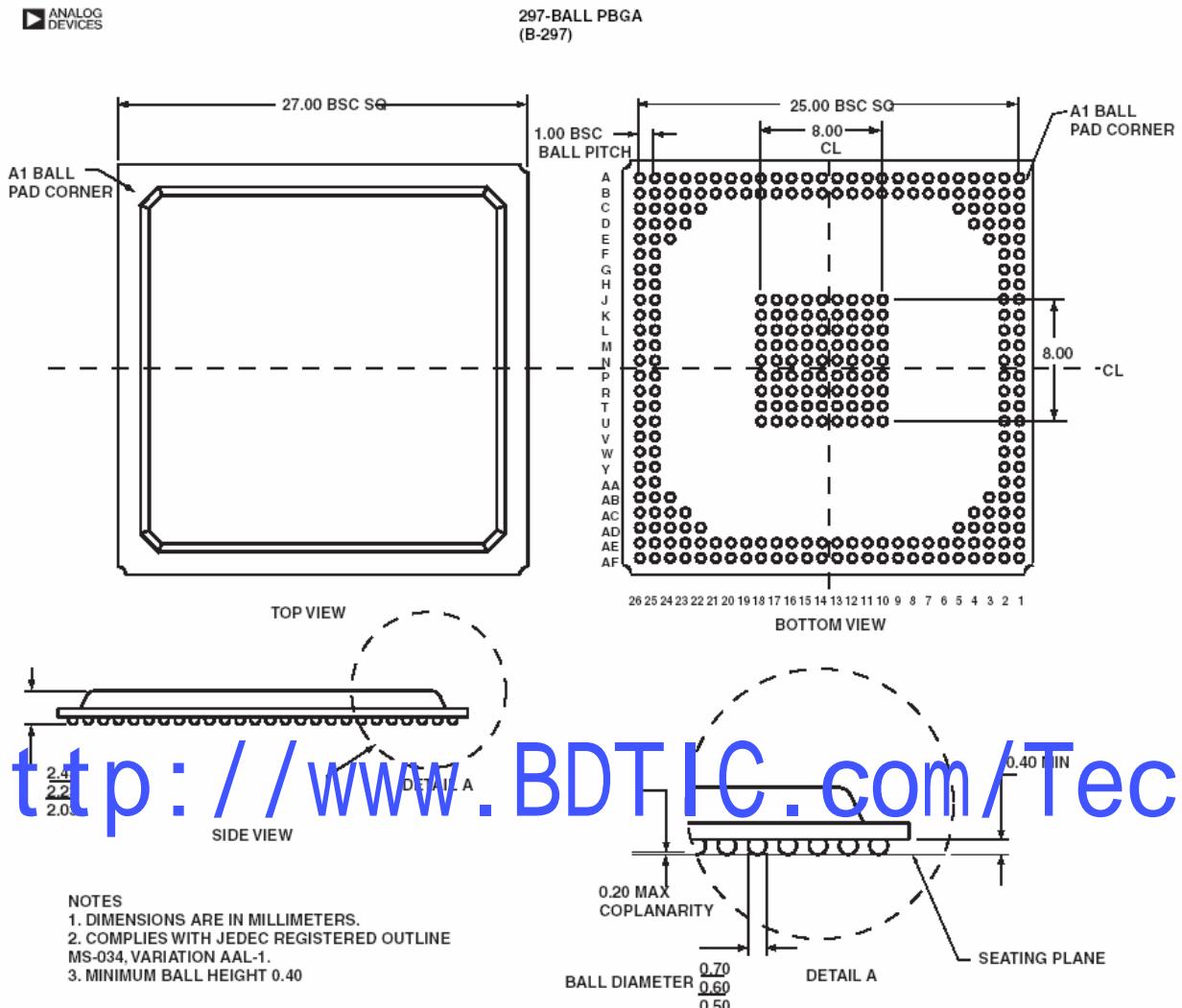

256 引脚 Mini-BGA 和 297 引脚 PBGA 两种封装

### 外设

两个并行输入/输出外围接口单元, 支持 ITU-R 656 视频数据格式, 可与 ADI 的模拟前端 ADC 无缝连接

2 个双通道全双工同步串行接口, 支持 8 个立体声 I<sup>2</sup>S 通道

2 个 16 通道 DMA 控制器和 1 个内部存储器 DMA 控制器

SPI 兼容端口

12 个通用 32-bit 定时/计数器, 支持 PWM

SPI 兼容端口

支持 IrDA 的 UART

2 个“看门狗”定时器

48 个可编程标志引脚

1x-63x 倍频的片内 PLL

## 目录

|                         |           |

|-------------------------|-----------|

| 概述.....                 | <b>3</b>  |

| 便携式低功耗结构 .....          | 3         |

| Blackfin处理器内核 .....     | 3         |

| 存储器结构.....              | 3         |

| 内部（片内）存储器.....          | 4         |

| 外部（片外）存储器.....          | 4         |

| I/O存储器空间 .....          | 5         |

| 引导.....                 | 5         |

| 事件处理.....               | 5         |

| 内核事件控制器(CEC) .....      | 6         |

| 系统中断控制器(SIC).....       | 6         |

| 事件控制.....               | 7         |

| DMA控制器.....             | 7         |

| “看门狗”定时器.....           | 7         |

| 串行口(SPORT).....         | 8         |

| 串行外设接口(SPI).....        | 8         |

| UART端口 .....            | 8         |

| 可编程标志 (PFX) .....       | 9         |

| 定时器.....                | 9         |

| 并行外设接口.....             | 9         |

| 通用模式描述.....             | 9         |

| 输入模式.....               | 9         |

| ITU-R656 模式描述 .....     | 9         |

| 有效视频模式.....             | 9         |

| 垂直消隐期模式.....            | 9         |

| 整场模式.....               | 9         |

| 动态功率管理.....             | 9         |

| 全速运行模式—最高性能 .....       | 10        |

| 活动运行模式—中等功率节省 .....     | 10        |

| 冬眠运行模式—最大静态功率节省 .....   | 10        |

| 休眠运行模式—高动态功率节省 .....    | 10        |

| 深度休眠运行模式—最大动态功率节省 ..... | 10        |

| 功率节省 .....              | 10        |

| 电压调节 .....              | 10        |

| 时钟信号 .....              | 11        |

| 引导模式 .....              | 11        |

| 指令集描述 .....             | 12        |

| 开发工具 .....              | 12        |

| 设计仿真器兼容的处理器板（目标） .....  | 13        |

| 附加信息 .....              | 13        |

| 引脚描述.....               | <b>14</b> |

| 技术规格.....               | <b>17</b> |

| 推荐工作条件 .....            | 17        |

|                                     |           |

|-------------------------------------|-----------|

| 电气特性 .....                          | 17        |

| 绝对最大额定值 .....                       | 17        |

| ESD 灵敏度 .....                       | 18        |

| 时序规格 .....                          | 18        |

| 时钟和复位时序 .....                       | 19        |

| 异步存储器读周期时序 .....                    | 20        |

| 异步存储器写周期时序 .....                    | 21        |

| SDRAM 接口时序 .....                    | 22        |

| 外部端口总线请求和许可周期时序 .....               | 23        |

| 并行外设接口时序 .....                      | 24        |

| 串行口: .....                          | 25        |

| 串行外设接口（SPI）—主时序 .....               | 28        |

| 串行外设接口（SPI）—从时序 .....               | 29        |

| 通用异步收发器（UART）端口—接收和发送时序 .....       | 30        |

| 定时器周期时序 .....                       | 31        |

| 可编程标志周期时序 .....                     | 32        |

| JTAG测试和仿真端口时序 .....                 | 33        |

| 功耗 .....                            | 34        |

| 输出驱动电流 .....                        | 34        |

| 测试条件 .....                          | 34        |

| 输出使能时间 .....                        | 34        |

| 输出禁止时间 .....                        | 34        |

| 系统保持时间计算举例 .....                    | 34        |

| 容性负载 .....                          | 35        |

| ADSP-BF561 256-BALL MBGA 引脚配置 ..... | <b>36</b> |

| ADSP-BF561 297-BALL PBGA 引脚配置 ..... | <b>38</b> |

| 外形尺寸 .....                          | <b>40</b> |

| 外形尺寸 .....                          | <b>41</b> |

| 订货指导 .....                          | <b>41</b> |

http://www.BDTIC.com/Tech

## 概述

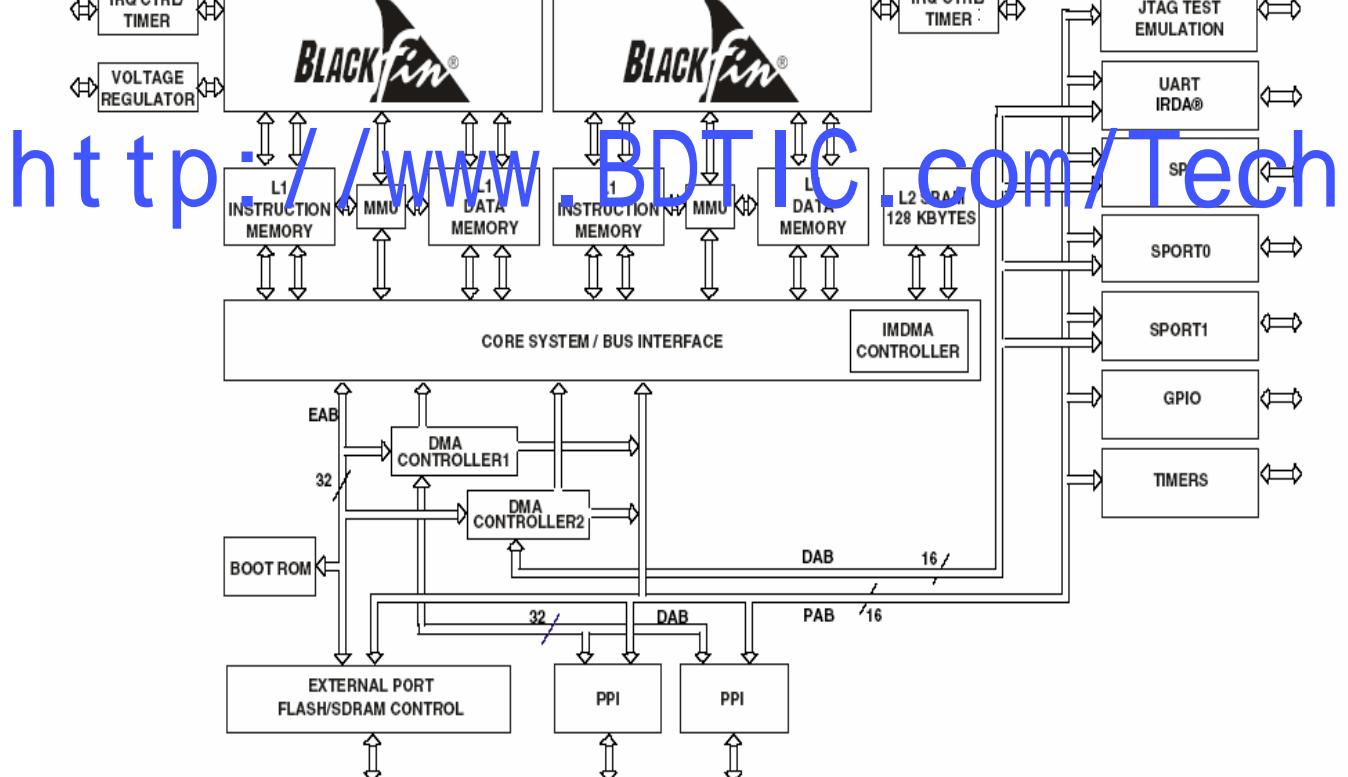

ADSP-BF561 处理器是 Blackfin 系列中的高性能产品，针对于多媒体和通信方面的各种应用。该器件的核心由两枚独立的 Blackfin 处理器组成。这些 Blackfin 处理器将艺术级的 dual-MAC 处理引擎，简洁的 RISC 式微处理器指令集的优点，以及单指令多数据(SIMD)多媒体能力结合起来，形成了一套独特的指令集结构。ADDP-BF561 集成了一套通用的数字图像处理外围设备，为数字图像处理和多媒体应用创建了一个完整的系统级片上解决方案。

ADSP-BF561 处理器具有 328Kbytes 的片上存储空间。每个 Blackfin 内核包括：

- 16K Bytes 指令 SRAM/Cache

- 16K Bytes 指令 SRAM

- 32K Bytes 数据 SRAM/Cache

- 32K Bytes 数据 SRAM

- 4K Bytes 存放中间结果的 SRAM

另外，片上存储外设包括：

- 128K Bytes 低延迟片内 SRAM

- 4 通道内部存储器 DMA 控制器

- 外部存储器控制器提供与 SDRAM,SRAM 和 Flash 的无缝连接。

## 便携式低功耗结构

Blackfin 处理器为嵌入式信号处理方面的应用提供了世界领先的电源管理和低功耗性能。Blackfin 处理器采用低功耗和低电压的设计方法，具有动态功率管理的特点，即通过改变工作电压和频率来大大降低总功耗。这个特点可使功耗呈指数级减少。对于便携式应用来说，这相当于延长了电池的寿命。

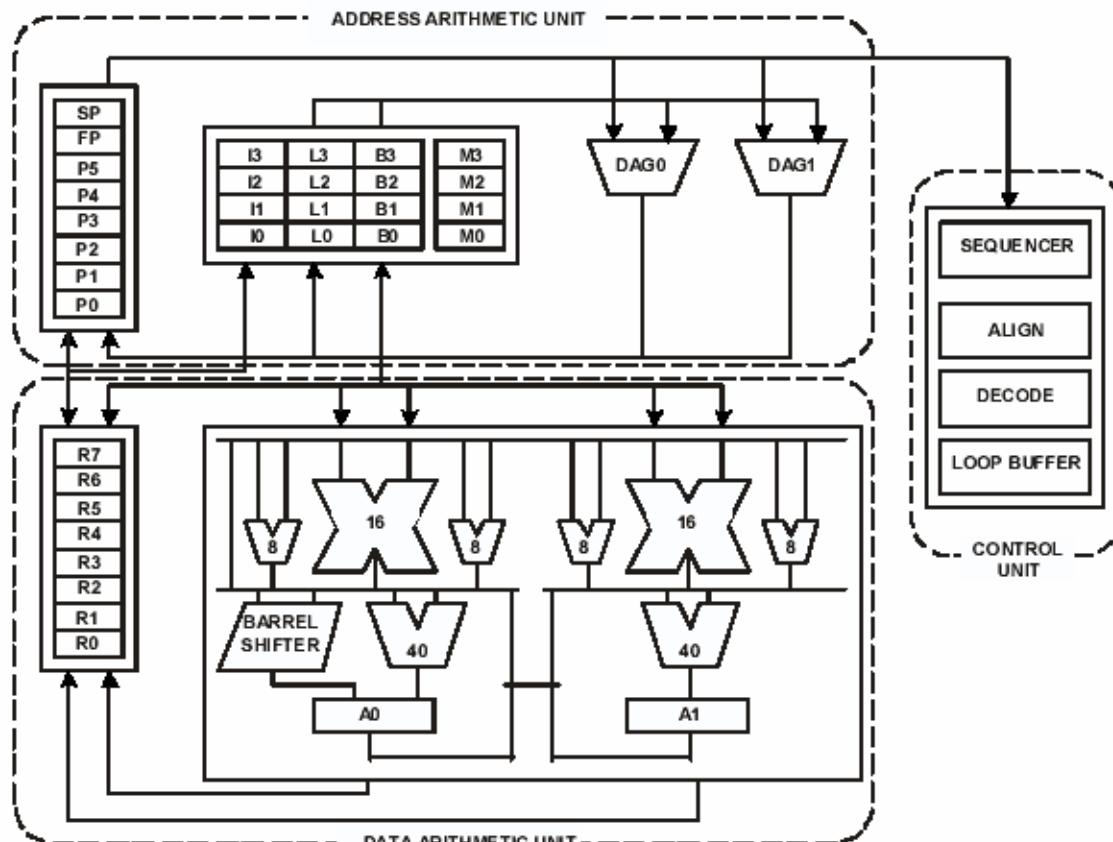

## Blackfin 处理器内核

如第 4 页的图 2 所示，每一个 Blackfin 内核包含 2 个乘/累加器(MAC)，2 个 40 位的 ALU，4 个视频 ALU 和 1 个 40 位移位器。运算单元处理来自寄存器组的 8 位、16 位或者 32 位数据。

每个 MAC 每周期可完成一个 16 位乘 16 位的乘法运算，并把结果累加到 40 位的累加器中，提供 8 位的精度扩展。ALU 单元执行标准的算术和逻辑运算，由于两个 ALU 具备对 16 或 32 位数据操作的能力，因此运算单元具备的灵活性可以满足各种应用中信号处理的要求。

每个 32 位的输入寄存器可以作为两个 16 位的寄存器，因此每个 ALU 可以完成非常灵活的单 16 位算术运算。通过把寄存器当作两个 16 位的操作数使用，双 16 位或单 32 位操作可以在一个周期中完成。更好地利用第二个 ALU，四个 16 位操作可以简单地完成，加速了每个周期的吞吐量。

强大的 40 位移位器功能丰富，可以对数据进行移位、循环移位、归一化、提取和存储等操作。运算单元所使用的数据来自具有 16 个 16 位操作数或 8 个 32 位操作数的寄存器组。

功能强大的程序控制器控制指令执行的顺序，包括指令对齐和译码。程序控制器支持条件跳转、子函数调用及零耗循环。循环缓冲区在本地储存指令，消除了循环代码访问指令存储器的时间。

两个数据地址产生器(DAG)为从存储器同时取回双操作数提供地址。两个数据地址产生器共用一个寄存器组，包括四套 32 位的索引、修改、长度和地址寄存器。8 个额外的 32 位寄存器为变量和堆栈位置的索引提供指针。

Blackfin 处理器采用改进的哈佛结构和分级的存储器结构。Level 1 (L1) 存储器一般以全速运行，没有或只有很少的延迟。Level 2 (L2) 是另一级存储器，分布在片内或片外，对它的访问会耗费多个处理器周期。在 L1 级，指令存储器只存放指令，2 个数据存储器存放数据，一个专用的临时数据存储器存放堆栈和局部变量信息。在 L2 级，采用统一的存储空间，可以存放指令和数据。

此外，L1 指令存储器的一半和 L1 数据存储器的一半可配置成静态 RAM (SRAM) 或 CACHE。存储器管理单元(MMU)提供存储器保护功能，对运行于内核上的独立的任务，可保护系统寄存器免于意外的存取。

这种体系结构提供了 3 种运行模式：用户模式、管理员模式和仿真模式。用户模式限制对某些系统资源的访问，因此提供了一个受保护的软件环境；而管理员模式对系统和内核资源的访问不受限制。

Blackfin 指令系统设计优化，16 位操作码组成了最常用的指令，这使得编译后的代码密度非常高。复杂 DSP 指令采用 32 位操作码，体现了多功能指令的全部特征。Blackfin 处理器支持有限的并行能力，即 1 个 32 位的指令可以和 2 个 16 位指令并行执行，使编程人员在单指令周期中使用尽可能多的内核资源。

Blackfin 汇编语言使用易于编程和可读性强的代数语法，而且在和 C/C++ 编译器的链接上进行了优化，给程序员提供了快速有效的软件环境。

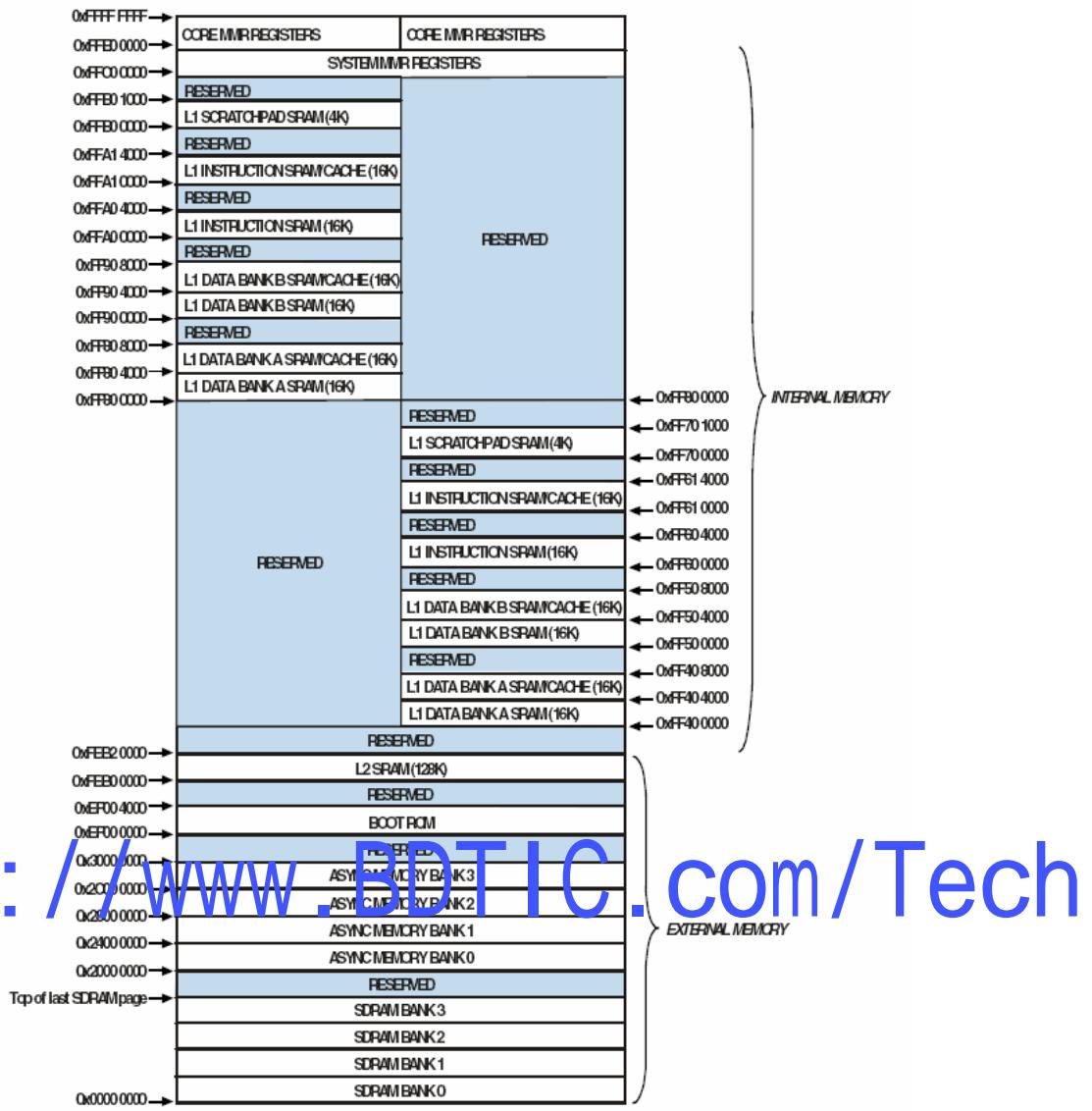

## 存储器结构

ADSP-BF561 把存储器视为一个统一的 4GBytes 的地址空间，使用 32 位地址。所有的资源，包括内部存储器、外部存储器和 I/O 控制寄存器，都占据公共地址空间中相应的部分，并且各自独立。此地址空间的各部分存储器按分级结构排列，以提供高性能价格比。一些非常快速、低延迟的存储器（如 CACHE 或 SRAM）的位置非常接近处理器，而更大的、低成本低性能的存储器远离处理器。参见图 3。

L1 存储器是内核中性能最高最重要的存储器。L2 存储器提供额外的存储能力，性能较低。片外存储系统通过外部总线接口单元(EBIU)进行访问，可以由 SDRAM、FLASH 和 SRAM 进行扩展，可以访问多达 768MBytes 的物理存储器。存储器的 DMA 控制器提供高带宽的数据传输能力，能够在内部 L1/L2 存储器和外部存储器空间之间完成代码或数据的块传输。

<http://www.BDTIC.com/Tech>

图 2. Blackfin DS32000 内核

### 内部（片内）存储器

ADSP-BF561 有 4 块片内存储器，提供到内核的高带宽的访问。

第 1 块是 Blackfin 内核的 L1 指令存储器，它由 16K Bytes 4 路组相联的 CACHE 和 16Kbytes 的 SRAM 组成。CACHE 存储器也可以配置成 SRAM。L1 指令存储器以处理器的最快速度访问。当被配置成 SRAM 时，存储器每个 16K Bank 被分成 4 个 4K 的 sub-bank，每个 sub-bank 可以被处理器和 DMA 独立地访问。

第 2 块片内存储器是 Blackfin 内核的 L1 数据存储器，由 4 个 16K Bytes 的 Bank 组成。L1 数据存储器的两个 Bank 可配置成 2 路组相联 CACHE 或一个 SRAM。另外两个 Bank 被配置成 SRAM，该存储器也以全速度访问。当被配置成 SRAM 时，存储器每个 16K Bank 被分成 4 个 4K 的 sub-bank，每个 sub-bank 可以被处理器和 DMA 独立地访问。

第 3 块是一个 4KBytes 的临时数据 SRAM，它和 L1 存储器有相同的运行速度，但是只能作为数据 SRAM（不能配置为 CACHE，也不能通过 DMA 访问）。

第 4 块片内存储系统是 L2 SRAM 存储器阵列，它提

供 128K Bytes 高速 SRAM，以内核速度的一半进行访问，比访问 L1 存储器 Bank 有稍多的延迟。L2 存储器是一个独立的指令和数据存储器，可以保存系统设计所要求的任意代码和数据的组合。两个 Blackfin 内核共享一个专用低延迟 64 位宽的通道端口，用于访问 L2 SRAM 存储器。

每个 Blackfin 内核处理器有其自己的内核存储器映射寄存器 (MMR)，但是它们共享相同的系统 MMR 寄存器和 128K Bytes 的 L2 SRAM 存储器。

### 外部（片外）存储器

ADSP-BF561 外部存储器通过外部总线接口单元 (EBIU) 进行访问。此接口可与多达 4 个 bank 的同步 DRAM (SDRAM)，或与多达 4 个异步存储设备（包括 FLASH、EPROM、ROM、SRAM 和存储器映射 I/O 设备等）无缝连接。

PC133 兼容的 SDRAM 控制器可通过编程与多达 4 个 Bank 的 SDRAM 接口，每个 Bank 容量为 16M Bytes 到 128 M Bytes，4 个 Bank 的总容量可达 512M Bytes。每一个 Bank 可独立编程，与其相邻的 Bank 连续排列而忽略 Bank 大小和位置方面的差异。这就允许内核将所有的 SDRAM 看作一个单独的、连续的物理地址空间，增加了对系统存储器配置和升级的灵活性。

图 3. ADSP-BF561 内部/外部存储器映射

异步存储器控制器也能够通过编程控制多达 4 个 bank，时序参数灵活的各种异步存储设备。无论使用设备的大小如何，每个 bank 的空间都占据 64MByte。这样，只有装满 4 个 64MByte 的存储器时地址空间才能连续。

I/O 存储器空间

Blackfin 处理器没有定义独立的 I/O 空间，所有的资源都被映射到统一的 32 位地址空间。片上 I/O 设备的控制寄存器被映射到靠近 4GByte 地址空间顶端的存储器映射寄存器(MMR)地址范围内。这个地址空间又被划分为两个部分，一部分包含设置所有内核功能的控制 MMR，另一部分包含用于设置和控制内核以外的片内外设的寄存器。内核 MMR 仅在管理员模式下可被内核访问，并且被看作是片内外设的保留空间。系统 MMR 仅在管理员模式下可被内核访问，至于对其他设备可见或是保留，取决于系统保护模型的要求。

ADSP-BF561 包括一个小的引导内核（kernel），用于配置相应的外设来引导。如果 ADSP-BF561 被配置为从引导 ROM 存储器引导，那么 DSP 从片内引导 ROM 开始执行。

事件处理

ADSP-BF561 的事件控制器处理到达处理器的所有同步和异步事件。事件处理支持嵌套和优先级。嵌套允许同时激活多个事件的服务程序。优先级保证高优先级事件的响应可以抢占较低优先级事件的响应。控制器支持 5 种不同类型的事件：

1. 仿真：仿真事件使处理器进入仿真模式，允许通过 JTAG 接口命令和控制处理器。

2. 复位：此事件使处理器复位。

3. 不可屏蔽中断(NMI)：NMI 事件可以由软件“看门狗”定时器或者处理器的 NMI 输入信号产生。NMI 事件经

常用作掉电指示，有序地进行系统关闭工作。

4. 异常：异常是与程序执行同步发生的事件，即异常会在指令执行完之前产生。例如数据对齐违规、未定义指令等情况都将导致异常。

5. 中断：中断是与程序执行异步发生的事件，由定时器、外设、输入引脚等引起，也可以由软件指令触发。

每个事件都有一个相应的保存返回地址的寄存器和一个相应的从事件返回指令。一个事件被触发后，处理器当前状态被保存在管理员堆栈内。

ADSP-BF561 事件控制器由两级组成，内核事件控制器(CEC)和系统中断控制器(SIC)。两者协同工作来确定优先级和控制所有系统事件。从概念上讲，来自外设的中断进入 SIC，然后被直接发送到 CEC 的通用中断中处理。

#### 内核事件控制器(CEC)

除专用中断和异常事件外，CEC 还支持 9 个通用中断(IVG15-7)。这些通用中断中，推荐将优先级最低的 2 个中断(IVG15-14)留作软件中断，剩下的 7 个优先级中断分别用于 ADSP-BF561 的外设。表 1 描述了 CEC 的事件、事件向量表(EVT)的名称及优先级。

表 1. 内核事件控制器(CEC)

| 优先级<br>(0 为最高) | 事件类     | EVT 入口 |

|----------------|---------|--------|

| 0              | 仿真/测试   | EVT    |

| 1              | 复位      | RST    |

| 2              | 不可屏蔽中断  | NMI    |

| 3              | 异常      | EVX    |

| 4              | 全局使能    | -      |

| 5              | 硬件错误    | IVHW   |

| 6              | 内核定时器   | IVTMR  |

| 7              | 通用中断 7  | IVG7   |

| 8              | 通用中断 8  | IVG8   |

| 9              | 通用中断 9  | IVG9   |

| 10             | 通用中断 10 | IVG10  |

| 11             | 通用中断 11 | IVG11  |

| 12             | 通用中断 12 | IVG12  |

| 13             | 通用中断 13 | IVG13  |

| 14             | 通用中断 14 | IVG14  |

| 15             | 通用中断 15 | IVG15  |

#### 系统中断控制器(SIC)

系统中断控制器为来自多个外设的中断源提供至 CEC 通用中断输入的映射和通道。尽管 ADSP-BF561 提供了默认的映射，用户仍可以通过改写中断设置寄存器(IAR)的值，来改变中断事件的映射和优先权。表 2 描述了 SIC 的中断源和至 CEC 的默认映射。

表 2. 系统中断控制器(SIC)

| 外设中断事件 | 通道 | 默认映射 |  |  |

|--------|----|------|--|--|

| PLL 唤醒 | 0  | IVG7 |  |  |

|               |    |       |

|---------------|----|-------|

| DMA1 错误       | 1  | IVG7  |

| DMA2 错误       | 2  | IVG7  |

| IMDMA 错误      | 3  | IVG7  |

| PPI1 错误       | 4  | IVG7  |

| PPI2 错误       | 5  | IVG7  |

| SPORT0 错误     | 6  | IVG7  |

| SPORT1 错误     | 7  | IVG7  |

| SPI 错误        | 8  | IVG7  |

| UART 错误       | 9  | IVG7  |

| 保留            | 10 | IVG7  |

| DMA1 0 中断     | 11 | IVG8  |

| DMA1 1 中断     | 12 | IVG8  |

| DMA1 2 中断     | 13 | IVG8  |

| DMA1 3 中断     | 14 | IVG8  |

| DMA1 4 中断     | 15 | IVG8  |

| DMA1 5 中断     | 16 | IVG8  |

| DMA1 6 中断     | 17 | IVG8  |

| DMA1 7 中断     | 18 | IVG8  |

| DMA1 8 中断     | 19 | IVG8  |

| DMA1 9 中断     | 20 | IVG8  |

| DMA1 10 中断    | 21 | IVG8  |

| DMA1 11 中断    | 22 | IVG8  |

| DMA2 0 中断     | 23 | IVG9  |

| DMA2 1 中断     | 24 | IVG9  |

| DMA2 2 中断     | 25 | IVG9  |

| DMA2 3 中断     | 26 | IVG9  |

| DMA2 4 中断     | 27 | IVG9  |

| DMA2 5 中断     | 28 | IVG9  |

| DMA2 6 中断     | 29 | IVG9  |

| DMA2 7 中断     | 30 | IVG9  |

| DMA2 8 中断     | 31 | IVG9  |

| DMA2 9 中断     | 32 | IVG9  |

| DMA2 10 中断    | 33 | IVG9  |

| DMA2 11 中断    | 34 | IVG9  |

| 定时器 0 中断      | 35 | IVG10 |

| 定时器 1 中断      | 36 | IVG10 |

| 定时器 2 中断      | 37 | IVG10 |

| 定时器 3 中断      | 38 | IVG10 |

| 定时器 4 中断      | 39 | IVG10 |

| 定时器 5 中断      | 40 | IVG10 |

| 定时器 6 中断      | 41 | IVG10 |

| 定时器 7 中断      | 42 | IVG10 |

| 定时器 8 中断      | 43 | IVG10 |

| 定时器 9 中断      | 44 | IVG10 |

| 定时器 10 中断     | 45 | IVG10 |

| 定时器 11 中断     | 46 | IVG10 |

| FIO0 中断 A     | 47 | IVG11 |

| FIO0 中断 B     | 48 | IVG11 |

| FIO1 中断 A     | 49 | IVG11 |

| FIO1 中断 B     | 50 | IVG11 |

| FIO2 中断 A     | 51 | IVG11 |

| FIO2 中断 B     | 52 | IVG11 |

| DMA1 写/读 0 中断 | 53 | IVG8  |

| DMA1 写/读 1 中断 | 54 | IVG8  |

|                |    |       |

|----------------|----|-------|

| DMA2 写/读 0 中断  | 55 | IVG9  |

| DMA2 写/读 1 中断  | 56 | IVG9  |

| IMDMA 写/读 0 中断 | 57 | IVG12 |

| IMDMA 写/读 1 中断 | 58 | IVG12 |

| “看门狗”定时器       | 59 | IVG13 |

| 保留             | 60 | IVG7  |

| 保留             | 61 | IVG7  |

| 增补 0           | 62 | IVG7  |

| 增补 1           | 63 | IVG7  |

### 事件控制

ADSP-BF561 为用户提供了非常灵活的机制来控制事件的处理。在 CEC 中，有 3 个寄存器用于调整和控制事件。如下所示，它们中的每个寄存器都是 16 位宽度，每一位代表一个特殊的事件类：

1. CEC 中断锁存寄存器(ILAT)--ILAT 寄存器用于指示事件何时被锁存。处理器锁存事件后相应的位置 1，事件被系统接受后该位清 0。该寄存器被控制器自动刷新，但仅当其相应的 IMASK 位被清除时可写。

2. CEC 中断屏蔽寄存器(IMASK)--IMASK 寄存器控制发生的事件是否被屏蔽。当 IMASK 寄存器的相应位置 1 时，事件不被屏蔽，发生后由系统处理。该位清 0 将屏蔽事件，即使该事件已被锁存在 ILAT 寄存器中，处理器也不会处理该事件。在管理员模式下，该寄存器可以被读写。(注：通用中断可以通过分别使用 STI 和 CLI 指令设置为全局使能和禁止。)

3. CEC 中断等待寄存器(IPEND)--IPEND 寄存器跟踪所有嵌套的事件。IPEND 寄存器中的相应位置 1 表示事件当前处于活动状态或嵌套在某一级。该寄存器被控制器自动刷新，但是在管理员模式下才能读取。

SIC 使用 6 个 32 位中断控制和状态寄存器，来进一步控制事件的处理。每个寄存器都包含表 2 所示的每个外设中断相对应的位。

1. SIC 中断屏蔽寄存器(SIC\_IMASK0, SIC\_IMASK1)--此寄存器控制每个外设中断事件是否被屏蔽。当寄存器的相应位置 1 时，事件不被屏蔽，发生后由系统处理。该位清 0 将屏蔽外设事件，使之不被处理。

2. SIC 中断状态寄存器(SIC\_ISTAT0, SIC\_ISTAT1)--由于多个外设可以映射到同一事件，该寄存器允许软件测定哪个外设事件源触发该中断。相应位置 1 表明外设发出了中断，为 0 则表明外设未发出中断。

3. SIC 中断唤醒使能寄存器(SIC\_IWR)--通过使能该寄存器中的相应位，当事件发生而处理器处于睡眠(掉电)模式时，可以设置一个外设唤醒处理器。(更多信息，见第 10 页动态功率管理。)

由于多个中断源可以映射到同一个通用中断，因此该中断输入上可能同时出现多个脉冲，这可以发生在对一个已检测到的中断处理之前或之中。IPEND 寄存器的内容由

SIC 监控，以检查中断是否得到确认。

当一个中断上升沿被检测到（检测需要 2 个处理器时钟周期），ILAT 寄存器的相应位被置 1。当 IPEND 寄存器的相应位被置 1 时，该位被清 0。IPEND 的这位表示该事件已进入处理器流水线。此时，CEC 将在下一个事件到来时识别其上升沿，并将这一事件排入队列。从通用中断的上升沿到 IPEND 寄存器的输出置 1，最小的延迟为 3 个处理器时钟周期；然而，由于内部的活动和处理器的模式不同，延迟可能更长。

### DMA 控制器

ADSP-BF561 有多个独立的 DMA 控制器，能够以最小的 DSP 内核开销完成数据自动传输。DMA 传输可以发生在 ADSP-BF561 的内部存储器和任一有 DMA 能力的外设之间。此外，DMA 传输也可以在任一有 DMA 能力的外设和已连接到外部存储器接口的外部设备之间完成（包括 SDRAM 控制器、异步存储器控制器）。有 DMA 传输能力的外设包括 SPORT、SPI 端口、UART 和 PPI 端口。每个独立的有 DMA 能力的外设至少有一个专用 DMA 通道。

ADSP-BF561 DMA 控制器能够支持一维（1D）或二维（2D）DMA 传输。DMA 传输的初始化可以由寄存器或名为描述子块的参数来实现。

二维 DMA 支持任意的行列数量，最大可达 64K 乘 64K 单位，支持任意数量的行列的步进，最大可达 +/-32K 单位而且，列步进的值可以小于一行步进的值，这就真正实现了行扫描的数据流。这个特性对于视频应用非常有用，可以在空闲时进行数据的隔行存储。

ADSP-BF561 DMA 控制器支持的典型 DMA 操作包括：

1. 单一的、传输完成时停止的线性缓冲区

2. 自动刷新循环缓冲区，当全部或部分缓冲区满时中断

3. 一维或二维 DMA，使用描述子链表

4. 二维 DMA，使用一个描述子阵列，仅指定公共页内的基 DMA 地址

除专用外设的 DMA 通道以外，在 ADSP-BF561 的不同存储器之间有 4 个存储器 DMA 通道。这使得任意的存储器（包括外部 SDRAM、ROM、SRAM 和 FLASH）之间的数据块传输成为可能，并使处理器干预降到最小。存储器 DMA 传输可以通过一套非常灵活的基于描述子的方法或标准的基于寄存器的自动缓冲机制来控制。

此外，ADSP-BF561 有一个 4 通道的内部存储器 DMA 控制器（IMDMA）。IMDMA 控制器允许数据在任意的内部 L1 和 L2 存储器间传送。

### “看门狗”定时器

每个 ADSP-BF561 内核包含一个 32 位定时器，可用于执行软件的“看门狗”功能。软件“看门狗”可以提高系统的可靠性，如果在软件复位前定时器溢出，软件“看门狗”通过产生一个硬件复位、不可屏蔽中断(NMI)或通用中

断来强迫处理器进入一个已知状态。程序员初始化定时器计数值，使能相应的中断，然后启动定时器。随后，软件必须在计数器从给定值计数到 0 前重新装载计数器。这样防止软件在正常情况下，由于外部噪声或软件错误使处理器运行在未知的状态。

复位后，软件可以通过查询定时器控制寄存器中相应状态位（该位只有在“看门狗”产生复位后才被置 1），来检测“看门狗”是否为硬件中断源。

定时器的时钟采用系统时钟(SCLK)，以最高频率  $f_{SCLK}$  运行。

#### 串行口(SPORT)

ADSP-BF561 提供 2 个双通道同步串行端口 (SPORT0 和 SPORT1) 来完成串行和多处理器的通信工作。SPORT 有以下特点：

1. 支持 I<sup>2</sup>S 功能。

2. 双向操作：每个 SPORT 都有 2 套独立的发送和接收引脚，支持 8 通道 I<sup>2</sup>S 立体声。

3. 缓冲的 (8-deep) 发送和接收端口：每个端口都有一个数据寄存器，用以同其它 DSP 部件间进行双向数据传输；多个移位寄存器用于数据寄存器内数据的移入和移出。

4. 时钟：每个发送或接收端口或者使用外部串行时钟，或者使用自己产生的时钟，频率范围为 ( $f_{SCLK}/131,070$ ) Hz 到 ( $f_{SCLK}/2$ ) Hz。

5. 字长：每个 SPORT 都支持 3 到 32 位长度的串行数据字，以最高有效位在前或最低有效位在前的格式传送。

6. 帧：每个发送和接收端口在无论每个数据字有无帧同步信号的情况下都能运行。帧同步信号能够从内部或者外部产生，可以高有效或低有效，要求 2 个脉冲宽度，可以前或后帧同步。

7. 硬件压扩：每个 SPORT 都能按照 ITU 推荐的 G.711 标准完成 A 律和 μ 律压扩。对 SPORT 的发送和/或接收通道都能进行压扩，而且没有额外的延迟。

8. 单时钟周期开销的 DMA 操作：每个 SPORT 都可以自动发送和接收多个缓冲区的数据信息。DSP 能够链接或串接 SPORT 和存储器之间的多个 DMA 传输。

9. 中断：完成数据传输或者通过 DMA 传输完单个或多个数据缓冲区之后，每个发送和接收端口都能产生一个中断。

10. 多通道能力：每个 SPORT 支持 1024 个通道窗中的 128 个通道，并兼容 H.100、H.110、MVIP-90 和 HMVIP 标准。

#### 串行外设接口(SPI)

ADSP-BF561 有 1 个 SPI 兼容的端口，能够使控制器

与多个 SPI 兼容的设备通信。

SPI 接口使用 3 个引脚传输数据：2 个数据引脚（主输出-从输入 MOSIx 和主输入-从输出 MISO）和 1 个时钟引脚（串行时钟 SCK）；1 个 SPI 片选输入引脚（SPISS）可使其它 SPI 设备选择 DSP；7 个 SPI 片选输出引脚（SPISEL7--1）使 DSP 能够选择其它 SPI 设备。SPI 片选引脚也可以被重新配置为可编程标志引脚。通过这些引脚，SPI 端口提供了全双工的同步串行接口，支持主从模式和多主环境。

每个 SPI 端口的波特率和时钟的相位/极性都是可编程的（见 SPI 时钟频率公式），而且都集成有一个 DMA 控制器，可配置为发送或接收数据流。SPI 的 DMA 控制器在任意给定时间，只能进行单向访问。

$$\text{SPI 时钟频率} = \frac{f_{SCLK}}{2 \times \text{SPIBAUD}}$$

在传输过程中，SPI 端口在 2 个串行数据线上通过移入和移出数据，同时完成发送和接收工作。串行时钟线使 2 条串行数据线上的数据移位和采样同步。

#### UART 端口

ADSP-BF561 提供 1 个全双工的通用异步接收/发送 (UART) 端口。它与 PC 标准的 UART 完全兼容。UART 端口为其它外设或主机提供一个简化的 UART 接口，支持全双工，有 DMA 能力的异步串行数据传输。每个 UART 端口支持 5 至 8 个数据位、1 或 2 个停止位以及无校验、奇校验、偶校验位。UART 端口支持以下 2 种模式的操作：

1. PIO (已编程 I/O)：处理器通过读/写 I/O 映射的 UATX 或 UARX 寄存器，发送或接收数据。在发送和接收时，数据都是双缓冲的。

2. DMA (直接存储器访问)：DMA 控制器传输发送和接收数据。这就减少了与存储器传输数据所需的中断的数量和频率。每个 UART 都有 2 个专用的 DMA 通道，一个用于发送，一个用于接收。这些 DMA 通道的默认优先级低于大多数 DMA 通道，因为其使用率相对较低。

UART 端口的波特率（见 UART 时钟频率公式）、串行数据格式、错误代码的产生和状态、及中断均可编程：

1. 支持位速率每秒从 ( $f_{SCLK}/1,048,576$ ) 到 ( $f_{SCLK}/16$ ) 位。

2. 支持每帧 7 至 12 位的数据格式。

3. 发送和接收操作都可被配置为对处理器产生可屏蔽中断。

$$\text{UART 时钟频率} = \frac{f_{SCLK}}{16 \times D}$$

这里 D=1 to 65536

与通用定时器联合使用可进行自动波特率检测。

UART的功能被进一步扩展，能支持红外数据协会(IrDA)的串行红外物理层连接规范(SIR)协议。

#### 可编程标志(PFx)

ADSP-BF561有48个双向的通用可编程I/O引脚(PF47-0)。可编程标志引脚有实现SPI端口操作的特殊功能。每一个可编程引脚都能通过操作下面的标志控制寄存器、标志状态寄存器和标志中断寄存器独立控制：

1. 标志方向控制寄存器—规定每个独立的PFx引脚的方向，用作输入或输出。

2. 标志控制和状态寄存器—不是强迫软件使用读-修改的处理来控制单个标志脚的设置，ADSP-BF561使用一种“写1设置”和“写1清除”的机制，能够在不影响其它标志的情况下，一个处理器周期内完成对这些标志进行任意组合地修改。2个控制寄存器用于此工作，一个用来设置标志，一个用来清除标志。通过软件读标志状态寄存器，可以查看标志的状态。

3. 标志中断屏蔽寄存器—中断屏蔽寄存器允许每个独立的PFx引脚为处理器提供中断。与用于设置和清除标志的标志控制寄存器类似，一个标志屏蔽寄存器通过设置相应的位来使能中断功能，另一个标志屏蔽寄存器通过清除相应的位来禁止中断功能。PFx引脚定义为输入时，能够设置为产生硬件中断；定义为输出时，能够设置为产生软件中断。

4. 标志中断敏感寄存器—标志中断敏感寄存器用于规定每个PFx引脚是电平还是边沿敏感，如果是边沿敏感，是仅上升沿敏感，还是信号的上升沿和下降沿都敏感。一个寄存器选择敏感类型，另一个寄存器选择边沿敏感的敏感边沿。

#### 定时器

ADSP-BF561有14通用个可编程定时器。12个通用定时器连有外部引脚，可以用作脉冲宽度调制器(PWM)或定时器输出，也可以用作定时器的输入锁定定时器或测量外部事件的脉冲宽度。定时器单元可以与UART联合使用，进行串行通道数据流的脉冲宽度的测量，提供自动的波特率检测功能。

定时器能够向处理器内核发出中断，为同步、处理器时钟、或外部信号的计数值提供周期性事件。除12个通用可编程定时器外，还提供了第13个定时器。这个额外的定时器由内部处理器时钟(CCLK)驱动，一般用作系统标记时钟，用以产生操作系统的周期性中断。

#### 并行外设接口

ADSP-BF561提供两个可直接与并行A/D和D/A转换器、符合ITU-601/656标准的视频编码和解码器以及其它通用外设连接的并行接口(PPI)。每个PPI包括一个专用时钟引脚，多达3个帧同步引脚和多达16个数据引脚。

在ITU-R 656模式下，PPI提供8或10位视频数据的

接收和解析。支持内嵌导言控制信号和同步信号的片内解码。

#### 通用模式描述

PPI的通用模式可应用于各种数据采集和数据传输的场合，该模式被分为4种主要的工作方式，每种每个PPI\_CLK时钟周期可传送高达16 bits的数据：

1. 内部产生帧同步信号的数据接收

2. 外部产生帧同步信号的数据接收

3. 内部产生帧同步信号的数据发送

4. 内部产生帧同步信号的数据发送

#### 输入模式

该模式适于ADC/DAC应用和带硬件握手的视频通讯。许多模式支持超过一个标准的帧同步信号。如果需要，可以在帧同步和接受/发送数据间加入可编程的延迟。

#### ITU-R656模式描述

该模式支持3种子模式：

- 1.有效视频模式

- 2.垂直消隐模式

- 3.整场模式

#### 有效视频模式

PPI不读取在有效视频结束(EAV)和有效视频启动(SAV)同步符号间的任何数据及垂直消隐间的数据。该模式下，控制字节序列不存入存储器，直接被PPI过滤。

#### 垂直消隐期模式

此模式下，PPI仅传输垂直消隐期间(VBI)的数据，以及行消隐信息和VBI行上的控制字序列。

#### 整场模式

整场模式下，PPI读入到来的全部数据流，包括有效视频、控制序列及水平和垂直消隐期间的辅助数据。

虽然不直接支持ITU-R656的输出，但可以通过在存储区中设定整帧结构(包括有效视频、消隐，和控制信息)，并用无帧同步模式将数据从PPI口送出来实现ITU-R656的输出功能。处理器的2D DMA模式简化了这种传送方法，它允许将静态帧缓冲器放在存储器中，而只更新整帧结构中的有效视频信息。

该模式适于ADC/DAC应用和带硬件握手的视频通讯。许多模式支持超过一个标准的帧同步信号。如果需要，可以在帧同步和接受/发送数据间加入可编程的延迟。

#### 动态功率管理

ADSP-BF561提供4种运行模式，每种模式有不同的性能/功耗特性。此外，动态功率管理有动态地改变处理器内核供电电压的控制功能，进一步降低功耗。控制每一个

ADSP-BF561 外设的时钟也能降低功耗。表 3 概要列出了每种模式下的功率设置。

### 全速运行模式—最高性能

在全速模式下，PLL 被使能，且不被旁路，因此提供最高运行频率。这是上电默认执行状态，此时可获得最高性能。处理器内核和所有使能的外设都以全速运行。

### 活动运行模式—中等功率节省

在此模式下，PLL 被使能，但被旁路。因为 PLL 被旁路，处理器内核时钟（CCLK）和系统时钟（SCLK）运行于输入时钟（CLKIN）频率下。在此模式下，CLKIN 到 CCLK 倍频可变，直到进入全速运行模式。通过适当地配置 L1 存储器，可以进行 DMA 访问。

在活动运行模式下，通过 PLL 控制寄存器（PLL\_CTL）禁止 PLL 是可能的。如果被禁止，在转换到全速或休眠模式前必须被使能。

表 3. 功率设置

| 模式   | PLL     | PLL 旁路 | 内核时钟（CCLK） | 系统时钟（SCLK） | 内核电源 |

|------|---------|--------|------------|------------|------|

| 全速   | 使能      | 否      | 使能         | 使能         | 开    |

| 活动   | 使能 / 禁用 | 是      | 使能         | 使能         | 开    |

| 休眠   | 使能      | -      | 禁用         | 使能         | 开    |

| 深度休眠 | 禁用      | -      | 禁用         | 禁用         | 开    |

| 冬眠   | 禁用      | -      | 禁用         | 禁用         | 关    |

### 冬眠运行模式-最大静态功率节省

冬眠模式通过关闭内核电压以及内核（CCLK）和所有同步外设（SCLK）的时钟来达到最大限度的静态功率节省。通过向 VR\_CTL 寄存器的 FREQ 位写 b#00，关闭内核电压调节器，从而关闭 CCLK 和 SCLK。并且，它使内部供电电压（V<sub>DDINT</sub>）输出为 0V，实现静态功耗最小。如果处理器的状态需要保存，内部存储的所有关键信息（存储器内容，寄存器内容等）必须在掉电前保存在非易失性存储器中。由于在该模式下，V<sub>DDEXT</sub> 仍正常工作，除非有其它特殊的情况，所有的外部引脚都处于三态。这将避免与处理器相连且未掉电的器件向处理器灌入不必要的电流。内部供电调节器可通过触发 RESET 引脚来唤醒。

### 休眠运行模式-高动态功率节省

休眠运行模式通过关闭处理器内核（CCLK）的时钟来降低功耗，然而 PLL 和系统时钟（SCLK）仍在运行。一般通过外部事件来唤醒处理器。此模式下唤醒的出现将会使处理器检查 PLL 控制寄存器（PLL\_CTL）中旁路位（BYPASS）的值。如果旁路位被关闭，处理器将切换到全速运行模式。如果旁路位使能，处理器将切换到活动运行模式。

休眠模式时，系统DMA不支持对L1存储器的访问。

### 深度休眠运行模式—最大动态功率节省

通过关闭处理器内核（CCLK）和所有同步外设（SCLK）的时钟，深度休眠运行模式获得最大的功率节省。异步外设不能访问内部资源或外部存储器。这种掉电模式只能通过复位中断（RESET）退出。如果 BYPASS 被禁用，处理器将转到全速模式；如果 BYPASS 被使能，处理器将转到活动模式。

### 功率节省

如表 4 所示，ADSP-BF561 支持 2 种不同的电源范围。使用多个电源范围在与工业标准和惯例兼容的同时，可获得最大的灵活性。通过将 ADSP-BF561 内部逻辑隔离为独立的电源，同其它 I/O 分离，处理器能够使用动态功率管理，而不影响其它 I/O 设备。对于各种电源范围，没有顺序上的要求。

表4. 电源范围

| 电源范围   | VDD范围              |

|--------|--------------------|

| 所有内部逻辑 | V <sub>DDINT</sub> |

| I/O    | V <sub>DDEXT</sub> |

处理器的功耗主要是处理器时钟和工作电压平方的函数。例如，降低 25% 的时钟频率就能降低 25% 的功耗，而降低 25% 的电压可以降低 40% 以上的功耗。此外，这些功率节省是加性的，如果时钟频率和电源都降低，功耗将会更显著地降低。

ADSP-BF561 动态功率管理允许处理器的输入电压（V<sub>DDINT</sub>）和时钟频率（f<sub>CCLK</sub>）动态可控

如上所述，功耗节省可用下面的模型：

功率节省因子

$$= \frac{f_{CCLKRED}}{f_{CCLKNOM}} \times \left( \frac{V_{DDINTRED}}{V_{DDINTNOM}} \right)^2 \times \left( \frac{T_{RED}}{T_{NOM}} \right)$$

公式中

f<sub>CCLKNOM</sub> 是标称内核时钟频率

f<sub>CCLKRED</sub> 是降低的内核时钟频率

V<sub>DDINTNOM</sub> 是标称内部供给电压

V<sub>DDINTRED</sub> 是降低的内部供给电压

T<sub>NOM</sub> 是运行在 f<sub>CCLKNOM</sub> 时的持续时间

T<sub>RED</sub> 是运行在 f<sub>CCLKRED</sub> 时的持续时间

功率节省因子的百分比为：

$$\% \text{ 功率节省} = (1 - \text{功率节省因子}) \times 100\%$$

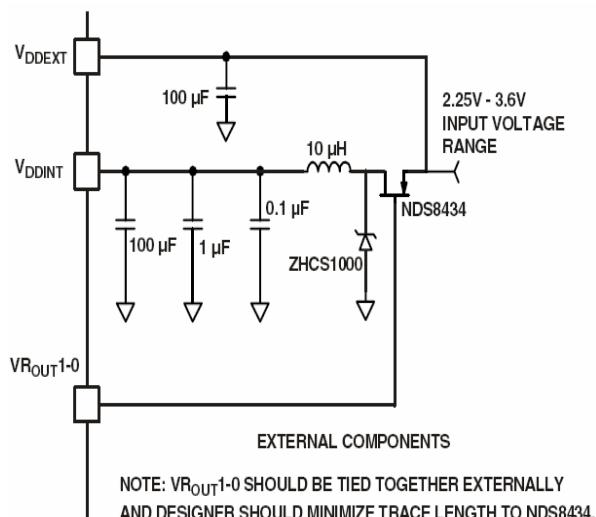

### 电压调节

ADSP-BF561 提供一个片内调压器，它可以从外部 2.25V 到 3.6V 的供电电压产生内部电压 0.85V(-5%/+10%) 到 1.2V (-5%/+10%)。完成电源管理典型的外部元件要求如图 4 所示。这个调压器控制内部逻辑电压，并且通过对

调压控制寄存器（VR\_CTL）编程，能够获得 50mV 增量的电压。为了减少待机功率损耗，内部调压器可进行编程，在保持 I/O( $V_{DDEXT}$ )供电的情况下去除处理器内核的供电。而在冬眠模式下， $V_{DDEXT}$  仍然可用，并且不需要外部的缓冲器。在这种掉电状态下，调压器可通过触发  $\overline{RESET}$  来激活，并初始化引导。调压器可由用户决定被禁止或旁路。

图 4. 电压调节电路

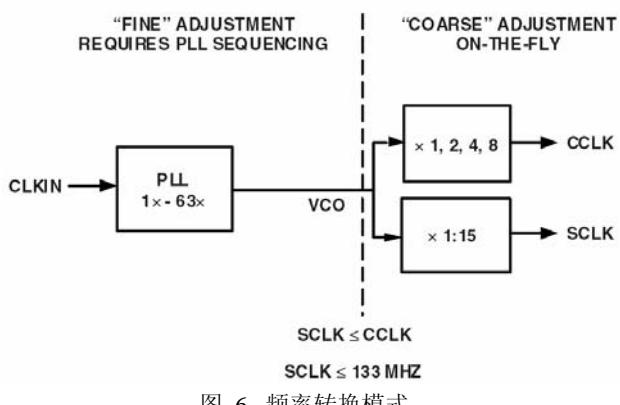

图 6. 频率转换模式

如图6所示，内核时钟（CCLK）和系统外设时钟（SCLK）可由输入时钟（CLKIN）信号获得。用户编程1x到63x的倍频因子，可使片上PLL倍频CLKIN信号。默认的倍数为10x，但可以通过软件指令改变。简单地写PLL\_DIV寄存器可以改变运行频率。

所有片上外设都以设定好的系统时钟（SCLK）速度运行。此系统时钟频率可通过PLL\_DIV寄存器的SSEL3-0位的值编程。SSEL的编程值规定了PLL输出（VCO）和系统时钟的分频比率。SCLK分频值为1到15，表5给出了典型的系统时钟比率。

| 信号名称    | 分频比率     | 频率比率示例 (MHz) |      |

|---------|----------|--------------|------|

|         |          | VCO          | SCLK |

| SSEL3-0 | VCO/SCLK |              |      |

| 0001    | 1:1      | 100          | 100  |

| 0110    | 6:1      | 300          | 50   |

| 1010    | 10:1     | 500          | 50   |

系统时钟最高频率是  $f_{SCLK}$ 。注意分频比率必须选择，使之能将系统时钟频率限制到最大值  $f_{SCLK}$ 。SSEL的值可以通过写PLL分频寄存器(PLL\_DIV)来动态改变，没有任何PLL锁定延时。

通过设置PLL\_DIV寄存器CSEL[1-0]位的值，也能动态地改变内核时钟（CCLK）频率。如表6所示，CCLK分频比率可以是1, 2, 4和8。可编程的内核时钟频率对快速的内核时钟频率修改非常有用。

表6. 内核时钟频率

| 信号名称      | 分频比率     | 频率比率示例 (MHz) |      |

|-----------|----------|--------------|------|

|           |          | VCO          | CCLK |

| CSEL[1-0] | VCO/SCLK |              |      |

| 00        | 1:1      | 500          | 500  |

| 01        | 2:1      | 500          | 250  |

| 10        | 4:1      | 200          | 50   |

| 11        | 8:1      | 200          | 25   |

### 引导模式

复位后，ADSP-BF561有三种机制（表7中列出）自动

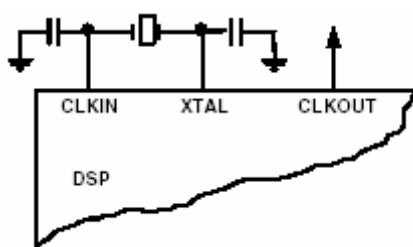

图 5. 外部晶体连接

载入内部L1指令存储器的程序。第四种模式从外部存储器执行，绕过引导程序。

**表7. 引导模式**

| BMODE1-0 | 说明                        |

|----------|---------------------------|

| 00       | 从外部16位存储器执行<br>(旁路引导ROM)  |

| 01       | 由8/16位Flash引导             |

| 10       | 保留                        |

| 11       | 由SPI0串行ROM引导<br>(16位地址范围) |

上电复位或软件初始化复位后，处理器采样复位配置寄存器的BMODE脚，执行以下引导模式：

1. 从外部16位存储器执行—从地址0x2000000开始执行，数据16位压缩，此模式跳过引导ROM。所有的配置参数都设置为适合最慢的设备（3个周期的保持时间，15个周期的R/W访问时间，4个周期的建立时间）

2. 从外部8位或16位外部Flash存储器引导—位于引导ROM存储空间的Flash引导程序通过异步存储器Bank0设置。所有的设置参数都适合最慢的设备。（3个周期的保持时间，15个周期的R/W访问时间，4个周期的建立时间）

3. 从SPI串行EEPROM引导（16位寻址）—SPI用PF2输出引脚选择一个SPI EEPROM设备，在地址0x0000开始发出连续读数据命令，并开始向L1指令存储器的起始部分送数。必须使用可16位寻址SPI兼容的EPROM。

对于每种引导模式，引导装载协议用于从外部存储器将程序和数据块传送到指定的存储器位置。多个存储区域通过引导序列来装载。所有的存储区域装载完毕后，内核A从L1指令SRAM的起始位置（0xFFA0 0000）开始执行。内核B仍然保持关闭状态。直到某个寄存器位被清零后，内核B从地址0xFF60 0000开始执行。

此外，应用程序可以设置复位配置寄存器第4位，在软件复位时跳过正常的引导序列。这样，处理器直接跳到L1指令存储空间的起始部分开始执行。

### 指令集描述

Blackfin DSP 系列汇编语言指令集使用易于编程和可读性强的代数语法。采用专门调整的灵活的高密度编码的指令，这些指令被编译后只占用非常小的存储空间。指令集还提供了体现 ADSP-BF561 全部特点的多功能指令，以使在一个指令中能够使用多个 DSP 内核资源。除许多微控制器上常见的功能外，指令集编译 C 和 C++ 源代码时效率非常高。此外，指令集还支持用户（算法/应用代码）和管理员（O/S 内核，设备驱动，调试器，ISRs）两种运行模式，允许对 DSP 内核资源的多级访问。

汇编语言采用了处理器独特的体系结构，具有以下优点：

1. 无缝集成DSP/CPU特征，对8位和16位操作进行了优

化。

2. 并发加载/存储的改进哈佛体系结构，每个周期支持2个16位MAC或4个8位ALU+2个加载/存储+2个指针更新。

3. 所有的寄存器、I/O、和存储器被映射成为统一4GB存储空间，提供了一个简化编程模式。

4. 微控制器特征，如任意位和位域操作，插入和提取；对8位、16位和32位数据类型上的整数操作；独立的用户和内核（kernel）栈指针。

5. 代码密度增强，包括混合的16和32位指令（无模式转换和代码分离）。常用指令以16位编码。

### 开发工具

ADI 公司提供一套完整的 ADSP-BF561 软硬件开发工具，包括仿真器和 Visual DSP++™ 开发环境。仿真器能够对 ADSP-BF561 实现全仿真，还支持对其它 ADI 的 JTAG DSPs 芯片的仿真。

利用 Visual DSP++ 项目管理环境，程序员可以开发和调试应用程序。这个环境包括一个基于代数语法的易于使用的汇编器，一个归档器（库和库建立工具），一个链接器，一个加载器，一个精确到时钟周期、指令级的模拟器，一个 C/C++ 编译器和一个包括 DSP 和数学函数的 C/C++ 运行库。这些工具的最重要特点是 C/C++ 代码的有效性。编译器能有效地将 C/C++ 代码转换为 Blackfin DSP 的汇编代码。Blackfin DSP 体系结构的特点也提高了 C/C++ 代码的编译效率。

Visual DSP++ 调试器有许多重要的特性。灵活的绘图功能使数据更加清楚，这种用图形表示的用户数据使编程者可以快速的确定算法的性能，算法越复杂，这种性能在设计者的计划中就越重要，它可以直接提高生产力。统计学的特性使编程者可以不用终止程序就能够得到处理器性能就象运行了中断一样。这种 Visual DSP++ 独有的特性使软件开发者不用中断程序的实时性就可以得到重要的代码执行情况，从而在本质上使开发者可以找到软件速度和效率的瓶颈，通过使用这个特性，编程者可以集中改正这些影响程序性能的地方。

用 Visual DSP++ 调试器调试 C/C++ 和汇编程序时，程序员能够：

1. 查看混合的C/C++和汇编代码（混合源代码和目标信息）

2. 插入断点

3. 根据寄存器、存储器和堆栈设置条件断点

4. 跟踪指令执行

5. 对执行的程序进行线性或统计性能分析

6. 对存储器进行Fill、Dump和绘图操作

7. 执行源程序级调试

## 8. 创建用户调试窗口

Visual DSP++ IDE 能够让程序员定义和管理 DSP 软件开发环境。它的对话框和属性页可以让程序员配置和管理所有的开发工具，包括 Visual DSP++ 编辑器里的语法高亮颜色。这些功能允许程序员：

1. 控制开发工具如何处理输入和产生输出

2. 维护与命令行操作一一对应的操作

Visual DSP++ 内核（VDK）提供进度和资源管理功能，能够根据存储器地址和 DSP 程序时序约束进行裁剪，能使工程师在开发新程序时提高编程效率，不用从头写起。 VDK 的特征包括线程，Critical 和 Unscheduled region，Semaphores，事件和设备标志。VDK 同时也支持优先级的、抢占的、协作和时间片的方法。此外，VDK 是可裁剪的。如果应用程序不使用某种功能，可以将支持此功能的代码从目标系统中清除。

因为 VDK 是一个库，开发者可以决定是否使用它。 VDK 已被集成到了 Visual DSP++ 开发环境中，也可以通过标准的命令行工具使用。当使用 VDK 调试一个程序时，开发环境帮助开发者解决许多易犯的错误同时帮助管理系统资源，自动配置许多 VDK 基础目标的阶段，并可视化系统状态。

VCSE 是 Analog Device 公司自己创造，使用并可以重复使用的软件组件（独立于子功能）。它用于快速并可靠的集合软件应用，使用者可以从网上下载使用这个组件。Visual DSP++ 里面也自带了新发布的组件。VCSE 支持 C/C++ 和汇编两种语言。

可以使用专家链接器（Expert Linker）对嵌入式系统中代码和数据位置的安排进行可视化的操作，查看存储器时使用了一种彩色的代码图形格式，可以通过鼠标的拖拽方便的将数据和代码移动到处理器或外部存储区，并可以检查实时堆栈和堆的使用情况。专家链接器与现存的链接文件（LDF）完全兼容，这样使开发者可以在文档形式和图形格式之间任意切换。

Analog Device 公司的仿真器使用 IEEE 1149.1 JTAG 测试访问端口在仿真时监视和控制目标板上的处理器。仿真器提供全速仿真，允许查看和修改存储器、寄存器和处理器堆栈。使用处理器 JTAG 接口可确保进行不干扰处理器运行的在电路仿真——仿真器不会影响目标系统的装载和定时。

除 Analog Device 公司提供软硬件开发工具外，第三方也提供了许多支持 Blackfin 处理器系列的工具。第三方软件工具包括 DSP 库、实时操作系统和方框图设计工具等。

## 设计仿真器兼容的处理器板（目标）

ADI 公司的仿真器是每个 DSP 开发者都需要的测试和调试软硬件系统的工具。ADSP-BF561 提供了一个 IEEE 1149.1 JTAG 测试访问端口（TAP）。通过此 TAP，仿真器能够访问处理器的内部，允许开发者装载代码，设置断点，观察变量和存储器，检查寄存器。在发送数据和命令时处

理器必须暂停，但当仿真器完成此次操作，处理器就可以全速运行，不影响系统的定时时序。

要使用这些仿真器，用户目标板上必须设计有 AD 的 JTAG DSP 接口和仿真插座。

有关目标板设计的细节问题，包括机械布局，单处理器连接、多处理器链、信号缓冲、信号终结和仿真器口逻辑，请参见 *EE-68:Analog Devices JTAG Emulation Technical Reference*。在 Analog Devices 官方网站上搜索“EE-68”即可查到。

## 附加信息

本数据手册在 ADSP-BF561 的结构和功能上作了概述。要了解 Blackfin 系列嵌入式处理器内核结构和指令集，请参见 ADSP-BF561 硬件参考手册和 Blackfin 系列指令集参考手册。

<http://www.BDTIC.com/Tech>

**引脚描述**

ADSP-BF561 的引脚定义列于表 8, 没有用的输入引脚应拉高到 V<sub>DDEXT</sub> 或者拉低到 GND。

**表 8. 引脚描述**

| 引脚                         | I/O | 信号 | 功能                             | 驱动类型 | 上拉下拉需求        |

|----------------------------|-----|----|--------------------------------|------|---------------|

| <u>存储器接口</u>               |     |    |                                |      |               |

| ADDR[25-2]                 | O   | 24 | 地址总线用于异步/同步访问                  | A    | 无             |

| DATA[31-0]                 | I/O | 32 | 数据总线用于异步/同步访问                  | A    | 无             |

| <u>ABE[3-0] /SDQM[3-0]</u> | O   | 4  | 字节使能<br>/异步/同步访问数据屏蔽           | A    | 无             |

| <u>BR</u>                  | I   | 1  | 总线请求                           |      | 无             |

| <u>BG</u>                  | O   | 1  | 总线允许                           | A    | 如果该功能不使用, 加上拉 |

| <u>BGH</u>                 | O   | 1  | 总线允许挂起                         | A    | 无             |

| <u>同步存储器控制</u>             |     |    |                                |      |               |

| <u>SRAS</u>                | O   | 1  | 行地址选通                          | A    | 无             |

| <u>SCAS</u>                | O   | 1  | 列地址选通                          | A    | 无             |

| <u>SWE</u>                 | O   | 1  | 写使能                            | A    | 无             |

| <u>SCKE</u>                | O   | 1  | 时钟使能                           | A    | 无             |

| <u>SCLK0/CLKOUT</u>        | O   | 1  | 时钟输出                           | B    | 无             |

| <u>SCLK1</u>               | O   | 1  | 时钟输出                           | B    | 无             |

| <u>SA10</u>                | O   | 1  | A10 引脚                         | A    | 无             |

| <u>AMS[3-0]</u>            | O   | 4  | Bank 选择                        | A    | 无             |

| <u>异步存储器控制</u>             |     |    |                                |      |               |

| <u>AMS[3-0]</u>            | O   | 4  | Bank 选择                        | A    | 无             |

| <u>ARDY</u>                | I   | 1  | 硬件准备好控制                        |      | 如果该功能不使用, 加上拉 |

| <u>AOE</u>                 | O   | 1  | 输出使能                           | A    | 无             |

| <u>AWE</u>                 | O   | 1  | 写使能                            | A    | 无             |

| <u>ARE</u>                 | O   | 1  | 读使能                            | A    | 无             |

| <u>并行设备接口</u>              |     |    |                                |      |               |

| PPI1D[15-8] /PF[47-40]     | I/O | 8  | PPI1 数据[15-8] / 可编程标志引脚[47-40] | C    | 软件配置, 无       |

| PPI1D[7-0]                 | I/O | 8  | PPI1 数据[7-0]                   | C    | 软件配置, 无       |

| PPI1CLK                    | I   | 1  | PPI1 时钟                        | C    | 软件配置, 无       |

| PPI1SYNC1 /TMR8            | I/O | 1  | PPI1 同步/定时器8                   | C    | 软件配置, 无       |

| PPI1SYNC2 /TMR9            | I/O | 1  | PPI1 同步/定时器9                   | C    | 软件配置, 无       |

| PPI1SYNC3                  | I/O | 1  | PPI1 同步                        | C    | 软件配置, 无       |

| PPI2D[15-8] /PF[39-32]     | I/O | 8  | PPI2 数据[15-8] / 可编程标志引脚[39-32] | C    | 软件配置, 无       |

| PPI2D[7-0]                 | I/O | 8  | PPI2 数据[7-0]                   | C    | 软件配置, 无       |

| PPI2CLK                    | I   | 1  | PPI2 时钟                        | C    | 软件配置, 无       |

| PPI2SYNC1 /TMR10           | I/O | 1  | PPI2 同步/定时器10                  | C    | 软件配置, 无       |

| PPI2SYNC2 /TMR11           | I/O | 1  | PPI2 同步/定时器11                  | C    | 软件配置, 无       |

| PPI2SYNC3                  | I/O | 1  | PPI2 同步                        | C    | 软件配置, 无       |

| <u>JTAG 端口</u>             |     |    |                                |      |               |

| EMU                        | O   | 1  | 仿真输出                           | C    | 无             |

|                    |       |   |                            |   |                  |

|--------------------|-------|---|----------------------------|---|------------------|

| TCK                | I     | 1 | JTAG 时钟                    |   | 内部下拉             |

| TDO                | O     | 1 | JTAG 串行数据输出                | C | 无                |

| TDI                | I     | 1 | JTAG 串行数据输入                |   | 内部下拉             |

| TMS                | I     | 1 | JTAG 模式选择                  |   | 内部下拉             |

| TRST               | I     | 1 | JTAG 复位                    |   | 如果不使用 JTAG, 外部下拉 |

| <i>UART 端口</i>     |       |   |                            |   |                  |

| RX /PF27           | I     | 1 | UART 接收/可编程标志引脚27          |   | 软件配置, 无          |

| TX /PF26           | O     | 1 | UATR 发送/可编程标志引脚26          | C | 软件配置, 无          |

| <i>SPI 端口</i>      | I/O/T |   |                            |   |                  |

| MOSI               | I/O   | 1 | 主输出从输入                     | C | 软件配置, 无          |

| MISO               | I/O   | 1 | 主输入从输出                     | C | 软件配置, 无          |

| SCK                | I/O   | 1 | SPI 时钟                     | D | 软件配置, 无          |

| <i>串行口</i>         |       |   |                            |   |                  |

| RSCLK0 /PF28       | I/O   | 1 | Sport0 接收串行时钟/可编程标志引脚28    | D | 软件配置, 无          |

| RFS0 /PF19         | I/O   | 1 | Sport0 接收帧同步/可编程标志引脚19     | C | 软件配置, 无          |

| DR0PRI             | I     | 1 | Sport0 接收主数据               |   | 软件配置, 无          |

| DR0SEC /PF20       | I     | 1 | Sport0 接收辅数据//可编程标志引脚20    |   | 软件配置, 无          |

| TSCLK0 /PF29       | I/O   | 1 | Sport0 发送串行时钟/可编程标志引脚29    | D | 软件配置, 无          |

| TFS0 /PF16         | I/O   | 1 | Sport0 发送帧同步/可编程标志引脚16     | C | 软件配置, 无          |

| DT0PRI /PF18       | O     | 1 | Sport0 发送主数据/可编程标志引脚18     | C | 软件配置, 无          |

| DT0SEC /PF17       | O     | 1 | Sport0 发送辅数据/可编程标志引脚17     | C | 软件配置, 无          |

| RSCLK1 /PF30       | I/O   | 1 | Sport1 接收串行数据/可编程标志引脚30    | D | 软件配置, 无          |

| RFS1 /PF24         | I/O   | 1 | Sport1 接收帧同步/可编程标志引脚24     | C | 软件配置, 无          |

| DR1PRI             | I     | 1 | Sport1 接收主数据               |   | 软件配置, 无          |

| DR1SEC /PF25       | I     | 1 | Sport1 接收辅数据/可编程标志引脚25     |   | 软件配置, 无          |

| TSCLK1 /PF31       | I/O   | 1 | Sport1 发送串行时钟/可编程标志引脚31    | D | 软件配置, 无          |

| TFS1 /PF21         | I/O   | 1 | Sport1 发送帧同步/可编程标志引脚21     | C | 软件配置, 无          |

| DT1PRI /PF23       | O     | 1 | Sport1 发送主数据/可编程标志引脚23     | C | 软件配置, 无          |

| DT1SEC /PF22       | O     | 1 | Sport1 发送辅数据/可编程标志引脚22     | C | 软件配置, 无          |

| <i>可编程标志 / 定时器</i> |       |   |                            |   |                  |

| PF0/SPISS/TMR0     | I/O   | 1 | 可编程标志引脚 0 / SPI 从选择输入/定时器0 | C | 软件配置, 无          |

| PF1 /SPISEL1       | I/O   | 1 | 可编程标志引脚 1 / SPI 从选择使       | C | 软件配置, 无          |

|                     |        |    |                                 |   |                  |

|---------------------|--------|----|---------------------------------|---|------------------|

| /TMR1               |        |    | 能 1 / 定时器 1                     |   |                  |

| PF2 /SPISEL2        | I/O    | 1  | 可编程标志引脚 2 / SPI 从选择使能 2 / 定时器 2 | C | 软件配置, 无          |

| /TMR2               |        |    |                                 |   |                  |

| PF3 /SPISEL3        | I/O    | 1  | 可编程标志引脚 3 / SPI 从选择使能 3 / 定时器 3 | C | 软件配置, 无          |

| /TMR3               |        |    |                                 |   |                  |

| PF4 /SPISEL4        | I/O    | 1  | 可编程标志引脚 4 / SPI 从选择使能 4 / 定时器 4 | C | 软件配置, 无          |

| /TMR4               |        |    |                                 |   |                  |

| PF5 /SPISEL5        | I/O    | 1  | 可编程标志引脚 5 / SPI 从选择使能 5 / 定时器 5 | C | 软件配置, 无          |

| /TMR5               |        |    |                                 |   |                  |

| PF6 /SPISEL6        | I/O    | 1  | 可编程标志引脚 6 / SPI 从选择使能 6 / 定时器 6 | C | 软件配置, 无          |

| /TMR6               |        |    |                                 |   |                  |

| PF7 /SPISEL7        | I/O    | 1  | 可编程标志引脚 7 / SPI 从选择使能 7 / 定时器 7 | C | 软件配置, 无          |

| /TMR7               |        |    |                                 |   |                  |

| PF8                 | I/O    | 1  | 可编程标志引脚 8                       | C | 软件配置, 无          |

| PF9                 | I/O    | 1  | 可编程标志引脚 9                       | C | 软件配置, 无          |

| PF10                | I/O    | 1  | 可编程标志引脚 10                      | C | 软件配置, 无          |

| PF11                | I/O    | 1  | 可编程标志引脚 11                      | C | 软件配置, 无          |

| PF12                | I/O    | 1  | 可编程标志引脚 12                      | C | 软件配置, 无          |

| PF13                | I/O    | 1  | 可编程标志引脚 13                      | C | 软件配置, 无          |

| PF14                | I/O    | 1  | 可编程标志引脚 14                      | C | 软件配置, 无          |

| PF15 /EXT CLK       | I/O    | 1  | 可编程标志引脚 15 / 外部计数器输入            | C | 软件配置, 无          |

| 时钟<br>CLKIN<br>XTAL | I<br>O | 1  | 时钟/晶体输入<br>晶体输出                 |   | 固定的电平值或时钟信号<br>无 |

| 模式控制                |        |    |                                 |   |                  |

| RESET               | I      | 1  | 复位                              |   | 核心电压开启后, 总是有效    |

| SLEEP               | O      | 1  | 睡眠                              | C | 无                |

| BMODE1-0            | I      | 2  | 引导模式绑定                          |   | 根据需要上拉或下拉        |

| BYPASS              | I      | 1  | 锁相环旁路控制                         |   | 根据需要上拉或下拉        |

| NMI0                | I      | 1  | 核 A 的不可屏蔽中断                     |   | 如果不使用该功能, 下拉     |

| NMI1                | I      | 1  | 核 B 的不可屏蔽中断                     |   | 如果不使用该功能, 下拉     |

| 电压调节                |        |    |                                 |   |                  |

| VROUT1-0            | O      | 2  | 外部 FET/BJT 驱动                   |   | N/A              |

| 电源                  |        |    |                                 |   |                  |

| VDDEXT              | P      | 23 | I/O 电源                          |   | N/A              |

| VDDINT              | P      | 14 | 内部电源                            |   | N/A              |

| GND                 | G      | 41 | 外部地                             |   | N/A              |

## 技术规格

#### 推荐工作条件

| 参数                   | 参数                                              | 最小   | 标称        | 最大  | 单位 |

|----------------------|-------------------------------------------------|------|-----------|-----|----|

| V <sub>DDINT</sub>   | 内部供电电压                                          | 0.8  | 1.2       | TBD | V  |

| V <sub>DDEXT</sub>   | 外部供电电压                                          | 2.25 | 2.5 或 3.3 | 3.6 | V  |

| V <sub>IH</sub>      | 高电平输入电压 <sup>1</sup> , @V <sub>DDEXT</sub> =max | 2.0  |           | 3.6 | V  |

| V <sub>IL</sub>      | 低电平输入电压 <sup>1</sup> , @V <sub>DDEXT</sub> =min | -0.3 |           | 0.6 | V  |

| T <sub>AMBIENT</sub> | 操作时周围环境温度                                       |      |           |     |    |

|                      | 工业                                              | -40  |           | 85  | °C |

|                      | 商用                                              | 0    |           | 70  | °C |

<sup>1</sup>ADSP-BF561 耐压为 3.3V（最大为 3.6V），由于  $V_{OH}$ （最大）大约等于  $V_{DDEXT}$ ，所以输出电压  $V_{OH}$  的值 取决于输入电压  $V_{DDEXT}$  的值。3.3V 的电压适用于双向引脚和输入引脚。

## 电气特性

| c                | 测试条件                      | 最小                                                                   | 最大  | 单位 |

|------------------|---------------------------|----------------------------------------------------------------------|-----|----|

| V <sub>OH</sub>  | 高电平输出电压 <sup>1</sup>      | @ V <sub>DDEXT</sub> = 3.0V,<br>I <sub>OH</sub> = -0.5 mA            | 2.4 | V  |

| V <sub>OL</sub>  | 低电平输出电压 <sup>1</sup>      | @ V <sub>DDEXT</sub> = 3.0V,<br>I <sub>OL</sub> = 2.0 mA             | 0.4 | V  |

| I <sub>IL</sub>  | 低电平输入电流 <sup>2</sup>      | @ V <sub>DDEXT</sub> = max,<br>V <sub>IN</sub> = 0 V                 | -10 | μA |

| I <sub>IH</sub>  | 高电平输入电流 <sup>3</sup>      | @ V <sub>DDEXT</sub> = max,<br>V <sub>IN</sub> = V <sub>DD</sub> max | 10  | μA |

| I <sub>IHP</sub> | JTAG <sup>4</sup> 高电平输入电流 | @ V <sub>DDEXT</sub> = max,<br>V <sub>IN</sub> = V <sub>DD</sub> max | 50  |    |

| I <sub>OZH</sub> | 三态漏电流 <sup>5</sup>        | @ V <sub>DDEXT</sub> = max<br>V <sub>IN</sub> = V <sub>DD</sub> max  | 10  | μA |

| I <sub>OZL</sub> | 三态漏电流 <sup>5</sup>        | @ V <sub>DDEXT</sub> = max<br>V <sub>IN</sub> = 0 V                  | -10 | μA |

| C <sub>IN</sub>  | 输入电容 <sup>6, 7</sup>      | f = 1 MHz,<br>T <sub>CASE</sub> = 25°C,<br>V <sub>IN</sub> = 2.5 V   | TBD | pF |

<sup>1</sup>适用于输出和双向引脚。

<sup>2</sup> 用于所有输入引脚

<sup>3</sup> 用于输入引脚（除 JTAG 输入）。

<sup>4</sup> 用于 JTAG 输入脚 (TCK, TDI, TMS, /TRST)

<sup>5</sup> 用于三态引脚。

<sup>6</sup> 所有信号引脚

<sup>6</sup> 保证但未测试

#### 绝对最大额定值

内核供电电压<sup>1</sup> ( $V_{DDINT}$ ) ... ... ... ... ... ... ... ... ... ... ... ... 0.3 V 到 +1.4 V

外部 (I/O) 供电电压<sup>1</sup> ( $V_{D.D.E.V.T.}$ ) ... ... -0.3V 到 +3.8V

外部 (I/O) 供电电压 (V<sub>D</sub>EXT) -0.5 V 到 +5.8 V

输入电压 <sup>1</sup> 0.5 V 到 3.6 V

输出电压  $^1$  摆动 0.5 V 到 5.0 V

输出电压 摆动 ... ... ... ... -0.5V 到 V<sub>DDEXT</sub>+0.5V

负载电容 1.2... ... ... ... 2.00nF

负载电容

由按时钟频率(GCL)决定

时钟频率(CCLK) 600MHz

ADSP-BF561SKBCZ600... 600MHz

ADSP-BF561SKBCZ500 500MHz

外设时钟频率 (SCLK) ..... 133 MHz

绝对温度范围 ..... -40 到 +85 °C

储存温度范围 -65°C 到 150°C

最高工作温度

管脚温度 (5 秒) ..... 185°C

<sup>1</sup>负荷超过上述值时芯片会受到永久性损坏。以上只是负荷额定值，芯片在超出

上述条件下的工作情况没有给出。在最大额定值条件下持续工作可能影响芯片的可靠性。

<sup>2</sup> 对于 SDRAM 控制操作,ADDR25-2,DATA15-0,/ABE1-0//SDQM3-0,CLKOUT,SCKE,,SA10,/SRAS,/SCAS,/SWE 和/SMS 的最大负载电容为 50 PF(3.3V)或 30PF(2.5V)

### ESD 灵敏度

#### 注意

ESD (静电放电) 灵敏器件。静电容易在人体或测试设备上积累高达 4000V 且放电不宜察觉。虽然 ADSP-BF561 有 ESD 保护电路, 但当芯片受到高能静电放电时可能会受到永久性破坏。因此, 建议采用适当的 ESD 保护措施, 以防止芯片性能降低和功能损失。

### 时序规格

表 9 到 12, 说明了 ADSP-BF561 处理器时钟的时序要求, 注意选择适当的 MSEL,SSEL 和 CSEL, 避免超出最大内核时钟, 系统时钟和压控振荡器(VCO)工作频率。表 12 说明了锁相环 (PLL) 的工作条件。

表 9. 内核和系统时钟要求——适用于 ADSP—BF561SKBCZ500

| 参数                | 描述                                                 | 最小值  | 最大值 | 单位 |

|-------------------|----------------------------------------------------|------|-----|----|

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.4\text{ V}\pm 50\text{mV}$ ) | na   |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.35\text{V}-5\%$ )            | na   |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.2\text{ V}-5\%$ )            | 2    |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.1\text{V}-5\%$ )             | 2.25 |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.0\text{V}-5\%$ )             | 2.7  |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=0.9\text{V}-5\%$ )             | 3.2  |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=0.8\text{V}$ )                 | 4    |     | ns |

表 10. 内核和系统时钟要求——适用于 ADSP—BF561SKBCZ600

| 参数                | 描述                                                 | 最小值  | 最大值 | 单位 |

|-------------------|----------------------------------------------------|------|-----|----|

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.4\text{ V}\pm 50\text{mV}$ ) | na   |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.35\text{V}-5\%$ )            | na   |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.2\text{ V}-5\%$ )            | 1.66 |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.1\text{V}-5\%$ )             | 2.25 |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.0\text{V}-5\%$ )             | 2.7  |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=0.9\text{V}-5\%$ )             | 3.2  |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=0.8\text{V}$ )                 | 4    |     | ns |

表 11. 内核和系统时钟要求——适用于 ADSP—BF561SBB600

| 参数                | 描述                                                 | 最小值  | 最大值 | 单位 |

|-------------------|----------------------------------------------------|------|-----|----|

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.4\text{ V}\pm 50\text{mV}$ ) | na   |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.35\text{V}-5\%$ )            | 1.66 |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.2\text{ V}-5\%$ )            | 2    |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.1\text{V}-5\%$ )             | 2.25 |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=1.0\text{V}-5\%$ )             | 2.7  |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=0.9\text{V}-5\%$ )             | 3.2  |     | ns |

| t <sub>CCLK</sub> | 内核指令周期 ( $V_{DDINT}=0.8\text{V}$ )                 | 4    |     | ns |

表 12. 锁相环工作条件

| 参数               | 描述      | 最小值 | 最大值      | 单位  |

|------------------|---------|-----|----------|-----|

| f <sub>VCO</sub> | 压控振荡器频率 | 50  | CCLK 最大值 | MHZ |

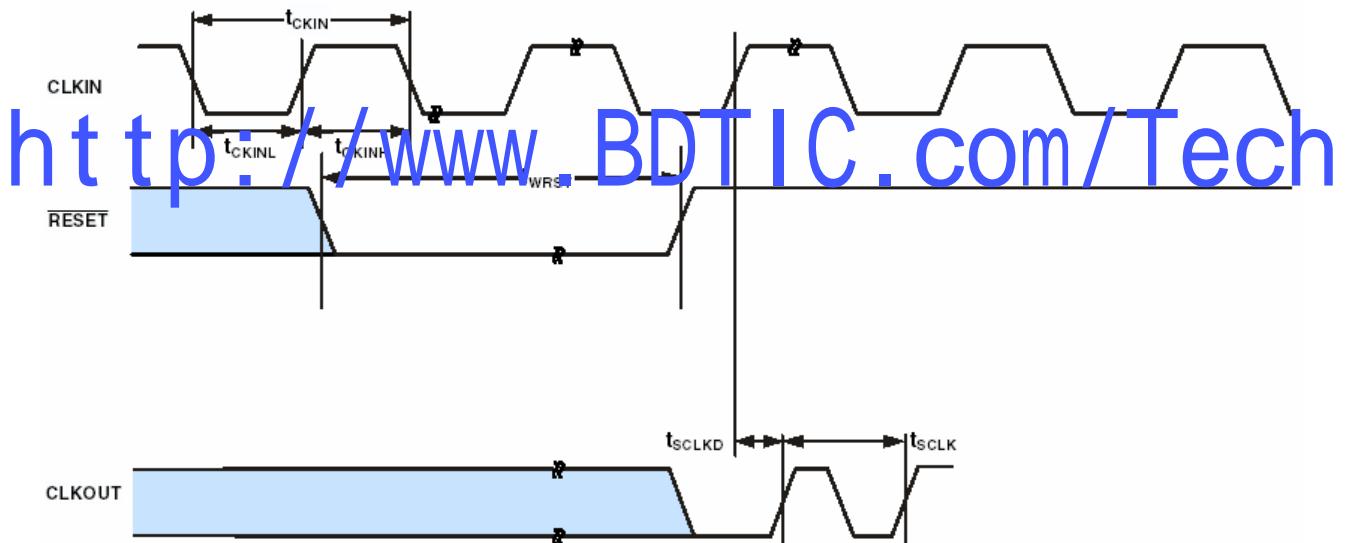

**时钟和复位时序**

表 13 和图 7 描述了时钟和复位操作。CLKIN 和时钟倍频器不能选择超过 600/133MHz 内核/外设时钟。

**表 13. 时钟和复位时序**

| 参数                 |                                                | 最小                  | 最大    | 单位 |

|--------------------|------------------------------------------------|---------------------|-------|----|

| <b>时序要求</b>        |                                                |                     |       |    |

| t <sub>CKIN</sub>  | CLKIN 周期                                       | 25.0                | 100.0 | ns |

| t <sub>CKINL</sub> | CLKIN 脉冲低电平 <sup>1</sup>                       | 10.0                |       | ns |

| t <sub>CKINH</sub> | CLKIN 脉冲高电平 <sup>1</sup>                       | 10.0                |       | ns |

| t <sub>WRST</sub>  | $\overline{\text{RESET}}$ 有效低电平脉宽 <sup>2</sup> | 11t <sub>CKIN</sub> |       | ns |

| <b>开关特性</b>        |                                                |                     |       |    |

| t <sub>SCLK</sub>  | CLKOUT 周期 <sup>3</sup>                         | 7.5 <sup>4</sup>    |       | ns |

<sup>1</sup>用于旁路模式和非旁路模式。

<sup>2</sup>用于上电顺序已完成情况。在上电时且当复位有效，处理器内部锁相环需要不超过 2000 个 CLKIN 周期，假定稳定的电源供给和 CLKIN（不包括外部时钟振荡器的启动时间）。

<sup>3</sup>t<sub>CKIN</sub> 和 t<sub>SCLK</sub> 之间有个比率，这个比率的控制是可编程的。更多的内容参见系统设计章节。

<sup>4</sup>t<sub>SCLK</sub> 总是比 t<sub>CCLK</sub> 要长

图 7. 时钟和复位时序

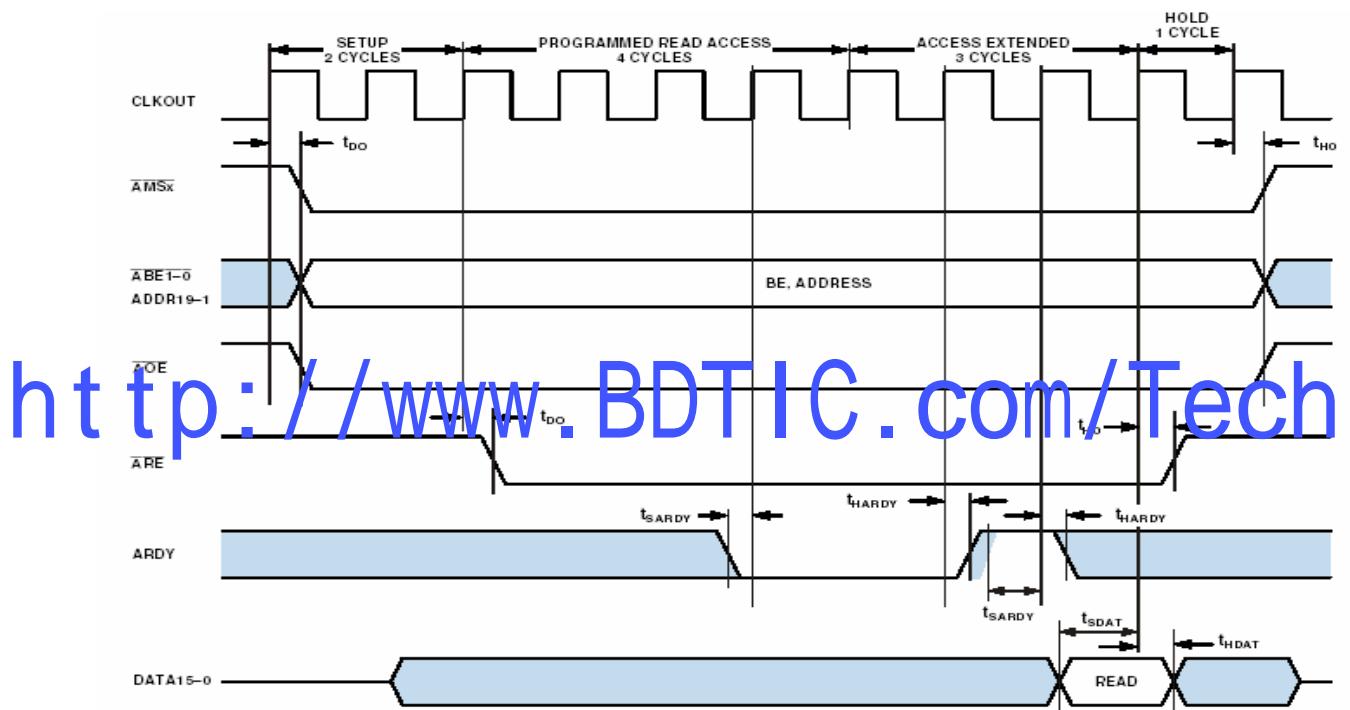

## 异步存储器读周期时序

表 14. 异步存储器读时序

| 参数          |                           | 最小  | 最大  | 单位 |

|-------------|---------------------------|-----|-----|----|

| 时序要求        |                           |     |     |    |

| $t_{SDAT}$  | CLKOUT 前 DATA15-0 建立      | 2.1 |     | ns |

| $t_{HDAT}$  | CLKOUT 后 DATA15-0 保持      | 0.8 |     | ns |

| $t_{SARDY}$ | CLKOUT 前 ARDY 建立          | 4.0 |     | ns |

| $t_{HARDY}$ | CLKOUT 后 ARDY 保持          | 0.0 |     | ns |

| 开关特性        |                           |     |     |    |

| $t_{DO}$    | CLKOUT 后输出延迟 <sup>1</sup> |     | 6.0 | ns |

| $t_{HO}$    | CLKOUT 后输出保持 <sup>1</sup> | 0.8 |     | ns |

<sup>1</sup> 输出引脚包括 AMS3-0, ABE1-0, ADDR25-2, AOE, ARE

图 8. 异步存储器读周期时序

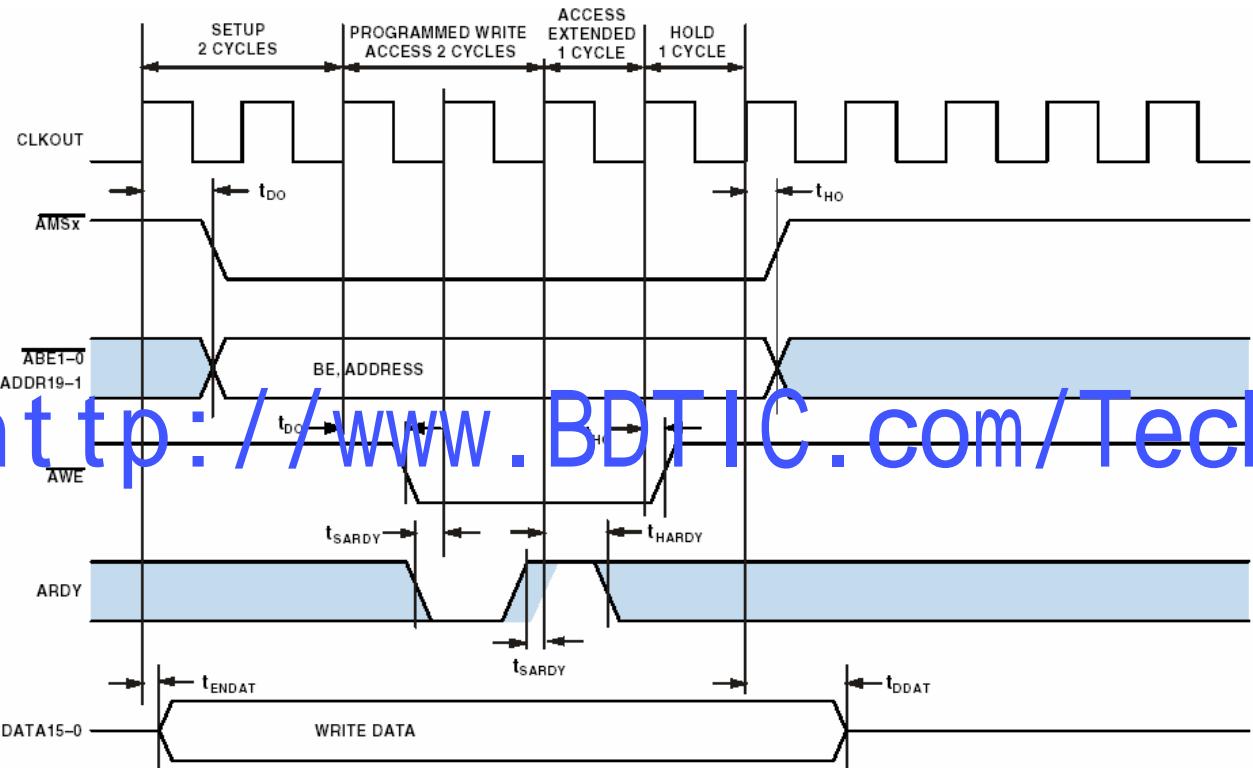

## 异步存储器写周期时序

表 15. 异步存储器写周期时序

| 参数          |                           | 最小  | 最大  | 单位 |

|-------------|---------------------------|-----|-----|----|

| 时序要求        |                           |     |     |    |

| $t_{SARDY}$ | CLKOUT 前 ARDY 建立          | 4.0 |     | ns |

| $t_{HARDY}$ | CLKOUT 后 ARDY 保持          | 0.0 |     | ns |

| 开关特性        |                           |     |     |    |

| $t_{DDAT}$  | CLKOUT 后 DATA15-0 禁止      |     | 6.0 | ns |

| $t_{ENDAT}$ | CLKOUT 后 DATA15-0 使能      | 1.0 |     | ns |

| $t_{DO}$    | CLKOUT 后输出延迟 <sup>1</sup> |     | 6.0 | ns |

| $t_{HO}$    | CLKOUT 后输出保持 <sup>1</sup> | 0.8 |     | ns |

<sup>1</sup> 输出引脚包括 AMS3-0, ABE1-0, ADDR19-1, DATA15-0, AOE, AWE。

图 9 异步存储器写周期时序

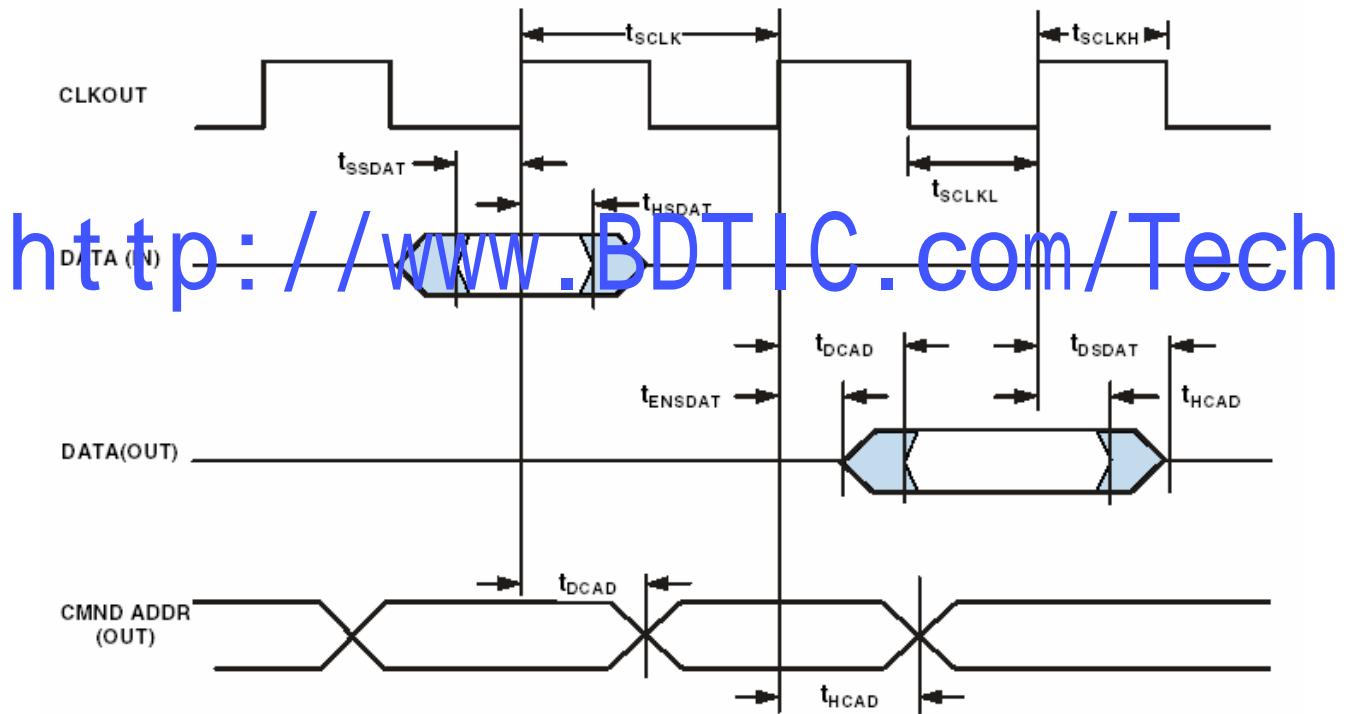

## SDRAM 接口时序

表 16. SDRAM 接口时序

| 参数                  |                                 | 最小  | 最大  | 单位 |

|---------------------|---------------------------------|-----|-----|----|

| <b>时序要求</b>         |                                 |     |     |    |

| t <sub>SSDAT</sub>  | CLKOUT 前 DATA 建立                | 2.1 |     | ns |

| t <sub>HSDAT</sub>  | CLKOUT 后 DATA 保持                | 0.8 |     | ns |

| <b>开关特性</b>         |                                 |     |     |    |

| t <sub>SCLK</sub>   | CLKOUT 周期                       | 7.5 |     | ns |

| t <sub>SCLKH</sub>  | CLKOUT 高电平宽度                    | 2.5 |     | ns |

| t <sub>SCLKL</sub>  | CLKOUT 低电平宽度                    | 2.5 |     | ns |

| t <sub>DCAD</sub>   | CLKOUT 后命令、地址和数据延迟 <sup>1</sup> |     | 6.0 | ns |

| t <sub>HCAD</sub>   | CLKOUT 后命令、地址和数据保持 <sup>1</sup> | 0.8 |     | ns |

| t <sub>DSDAT</sub>  | CLKOUT 后数据禁止                    |     | 6.0 | ns |

| t <sub>ENSDAT</sub> | CLKOUT 后数据使能                    | 1.0 |     | ns |

<sup>1</sup>命令引脚包括: SRAS, SCAS, SWE, SDQM, SMS3-0, SA10, SCKE。

图 10. SDRAM 接口时序

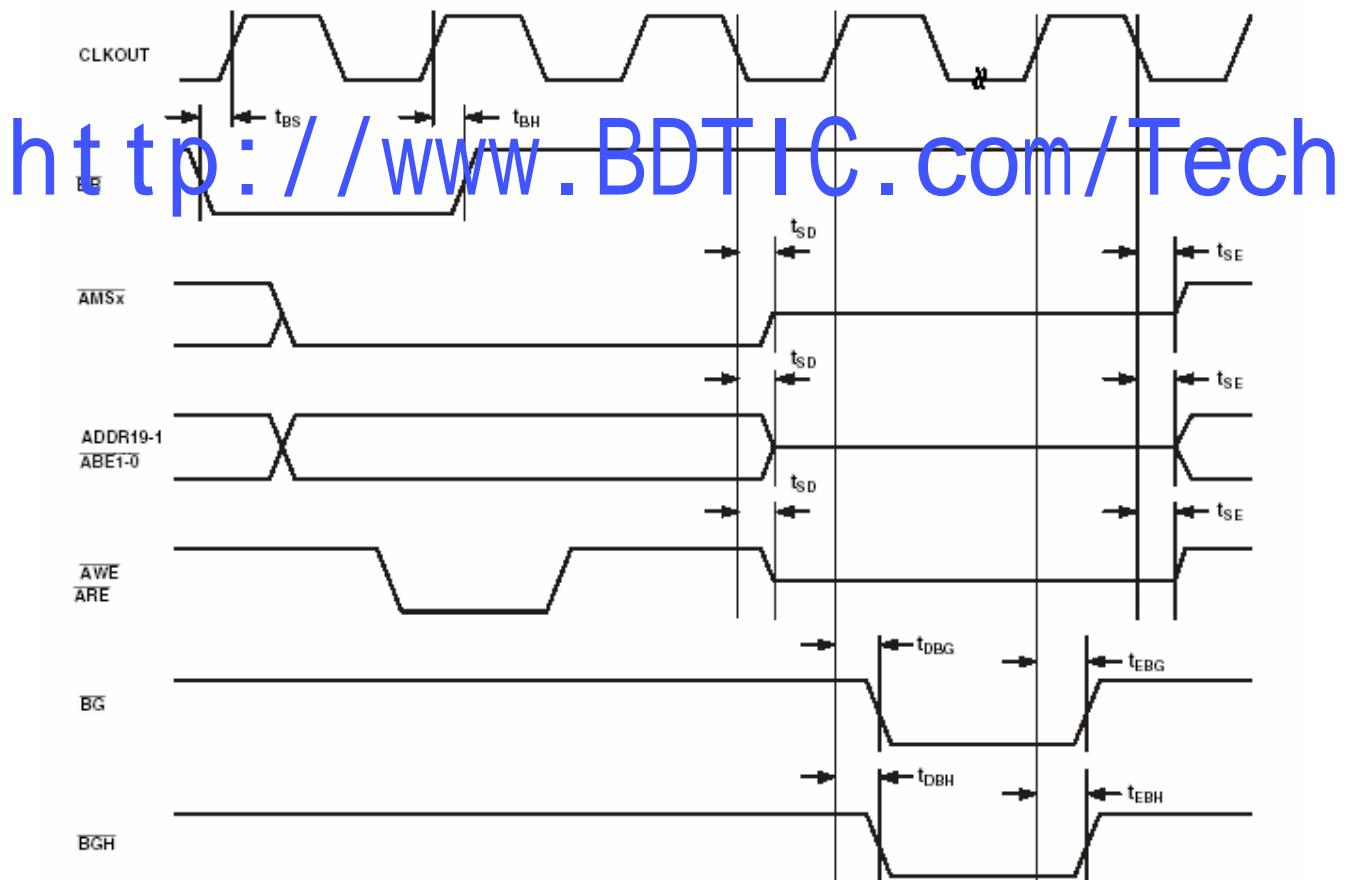

## 外部端口总线请求和许可周期时序

表 17 和图 11 描述了外部端口总线请求和总线许可操作。

表 17. 外部端口总线请求和许可周期时序

| 参数 <sup>1,2</sup> |                            | 最小  | 最大  | 单位 |

|-------------------|----------------------------|-----|-----|----|

| <b>时序要求</b>       |                            |     |     |    |

| t <sub>BS</sub>   | BR 使 CLKOUT 高建立            | 4.6 |     | ns |

| t <sub>BH</sub>   | CLKOUT 高到 BR 保持时间          | 0.0 |     | ns |

| <b>开关特性</b>       |                            |     |     |    |

| t <sub>SD</sub>   | CLKOUT 高到 xMS、地址和 RD/WR 禁止 |     | 4.5 | ns |

| t <sub>SE</sub>   | CLKOUT 低到 xMS、地址和 RD/WR 使能 |     | 4.5 | ns |

| t <sub>DBG</sub>  | CLKOUT 高到 BG 有效建立          |     | 3.6 | ns |

| t <sub>EBG</sub>  | CLKOUT 高到 BG 无效保持时间        |     | 3.6 | ns |

| t <sub>DBH</sub>  | CLKOUT 高到 BGH 有效建立         |     | 3.6 | ns |

| t <sub>EBH</sub>  | CLKOUT 高到 BGH 无效保持时间       |     | 3.6 | ns |

<sup>1</sup> 这是基于操作条件最坏情况的初步时序参数。

<sup>2</sup> 这些时序参数的焊盘负载是 20pF。

图 11. 外部端口总线请求和许可周期时序

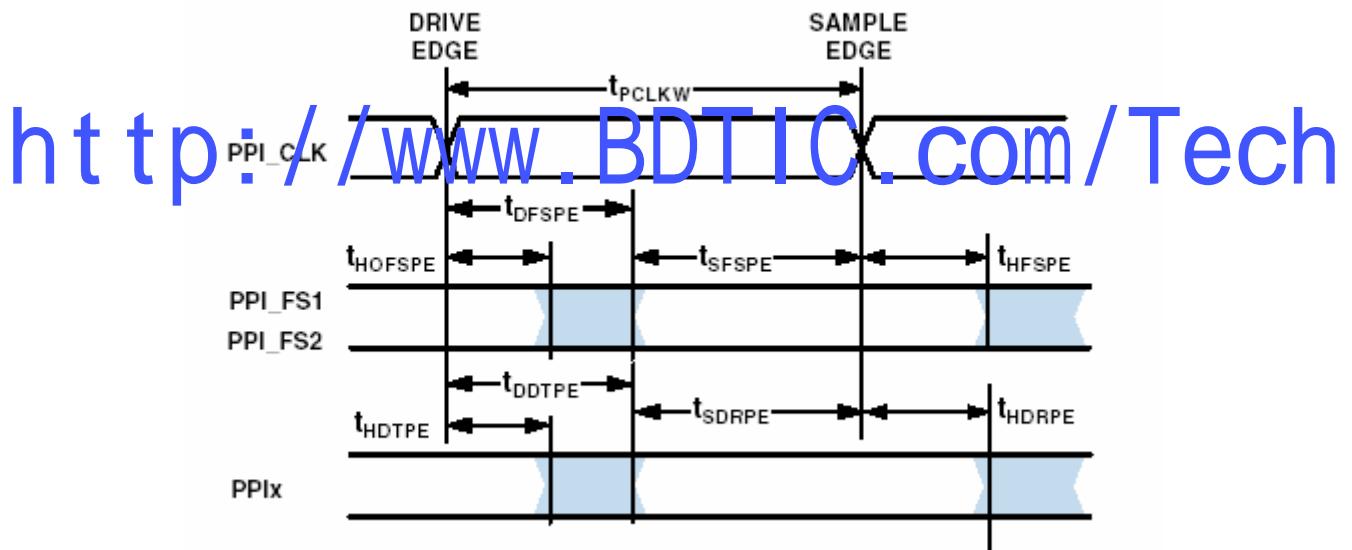

## 并行外设接口时序

表 18 和图 12 描述了并行外设的接口操作。

表 18. 并行外设接口时序

| 参数                      |                         | 最小   | 最大   | 单位 |

|-------------------------|-------------------------|------|------|----|

| <b>时序要求</b>             |                         |      |      |    |

| $t_{PCLKY}$             | PPI_CLK 宽度              | 6.0  |      | ns |

| $t_{PCLK}$              | PPI_CLK 周期 <sup>1</sup> | 15.0 |      | ns |

| $t_{SFSPE}$             | PPI_CLK 前的外部帧同步建立时间     | 3.0  |      | ns |

| $t_{HFSPE}$             | PPI_CLK 后的外部帧同步保持       | 3.0  |      | ns |

| $t_{SDPRE}$             | PPI_CLK 前接收数据建立         | TBD  |      | ns |

| $t_{SDRPE}$             | PPI_CLK 后接收数据保持         | TBD  |      | ns |

| <b>开关特性—GP 输入和帧捕获模式</b> |                         |      |      |    |

| $t_{DFSPE}$             | PPI_CLK 后的内部帧同步延时       |      | 10.0 | ns |

| $t_{HOSFPE}$            | PPI_CLK 后的内部帧同步保持       | 0.0  |      | ns |

| $t_{DDTPE}$             | PPI_CLK 后的传送数据延迟        |      | 10.0 | ns |

| $t_{HDTPE}$             | PPI_CLK 后的传送数据保持        | 0.0  |      | ns |

<sup>1</sup>PPI\_CLK 频率不能超过  $f_{SCLK}/2$ 。

图 12. PPI 时序

串行口:

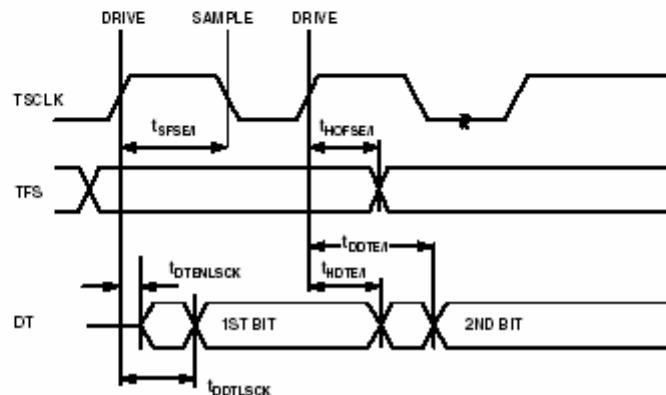

表 19 到 24 和图 13 到 15 描述了串口操作。

表 19. 串行口—外部时钟

| 参数          |                                     | 最小   | 最大 | 单位 |

|-------------|-------------------------------------|------|----|----|

| <b>时序要求</b> |                                     |      |    |    |

| $t_{SFSE}$  | TCLK/RCLK 前 TFS/RFS 建立 <sup>1</sup> | 3.0  |    | ns |

| $t_{HFSE}$  | TCLK/RCLK 后 TFS/RFS 保持 <sup>1</sup> | 3.0  |    | ns |

| $t_{SDRE}$  | RCLK 前接收数据建立 <sup>1</sup>           | 3.0  |    | ns |

| $t_{HDRE}$  | RCLK 后接收数据保持 <sup>1</sup>           | 3.0  |    | ns |

| $t_{SCLKW}$ | TCLK/RCLK 宽度                        | 4.5  |    | ns |

| $t_{SCLK}$  | TCLK/RCLK 周期                        | 15.0 |    | ns |

<sup>1</sup>以采样边沿为参考。

表 20. 串行口—内部时钟

| 参数          |                                     | 最小   | 最大 | 单位 |

|-------------|-------------------------------------|------|----|----|

| <b>时序要求</b> |                                     |      |    |    |

| $t_{FSI}$   | TCLK/RCLK 前 TFS/RFS 建立 <sup>1</sup> | TBD  |    | ns |

| $t_{HFSI}$  | TCLK/RCLK 后 TFS/RFS 保持 <sup>1</sup> | TBD  |    | ns |

| $t_{SDRI}$  | RCLK 前接受数据建立 <sup>1</sup>           | 6.0  |    | ns |

| $t_{HDRI}$  | RCLK 后接受数据保持 <sup>1</sup>           | 0.0  |    | ns |

| $t_{SCLKW}$ | TSCLK/RSCLK 宽度                      | 4.5  |    | ns |

| $t_{SCLKE}$ | TSCLK/RSCLK 周期                      | 15.0 |    | ns |

<sup>1</sup>以采样边沿为参考。

表 21. 串行口—外部时钟

参数

| 参数          |                                       | 最小  | 最大   | 单位 |

|-------------|---------------------------------------|-----|------|----|

| <b>开关特性</b> |                                       |     |      |    |

| $t_{DFSE}$  | TCLK 后 TFS 延迟（内部产生的 TFS） <sup>1</sup> |     | 10.0 | ns |

| $t_{HOFSE}$ | TCLK 后 TFS 保持（内部产生的 TFS） <sup>1</sup> | 0.0 |      | ns |

| $t_{DDTE}$  | TCLK 后发送数据延迟 <sup>1</sup>             |     | 10.0 | ns |

| $t_{HDTE}$  | TCLK 后发送数据保持 <sup>1</sup>             | 0.0 |      | ns |

<sup>1</sup>以驱动边沿为参考。

表 22. 串行口—内部时钟

| 参数          |                                       | 最小  | 最大  | 单位 |

|-------------|---------------------------------------|-----|-----|----|

| <b>开关特性</b> |                                       |     |     |    |

| $t_{DFS1}$  | TCLK 后 TFS 延迟（内部产生的 TFS） <sup>1</sup> |     | TBD | ns |

| $t_{HOFS1}$ | TCLK 后 TFS 保持（内部产生的 TFS） <sup>1</sup> | TBD |     | ns |

| $t_{DDTI}$  | TCLK 后发送数据延迟 <sup>1</sup>             |     | TBD | ns |

| $t_{HDTI}$  | TCLK 后发送数据保持 <sup>1</sup>             | TBD |     | ns |

| $t_{SCLKW}$ | TCLK/RCLK 宽度                          | 4.5 |     | ns |

<sup>1</sup>以驱动边沿为参考。

表 23. 串行口—使能和三态

| 参数          |                              | 最小  | 最大 | 单位 |

|-------------|------------------------------|-----|----|----|

| <b>开关特性</b> |                              |     |    |    |

| $t_{DTENE}$ | 外部 TCLK 的数据使能延迟 <sup>1</sup> | TBD |    | ns |

| $t_{DDTTE}$ | 外部 TCLK 的数据禁止延迟 <sup>1</sup> | TBD |    | ns |

| $t_{DTENI}$ | 内部 TCLK 的数据使能延迟              | TBD |    | ns |

| $t_{DDTTI}$ | 内部 TCLK 的数据禁止延迟 <sup>1</sup> | TBD |    | ns |

<sup>1</sup>以驱动边沿为参考。

图 13. 串行口

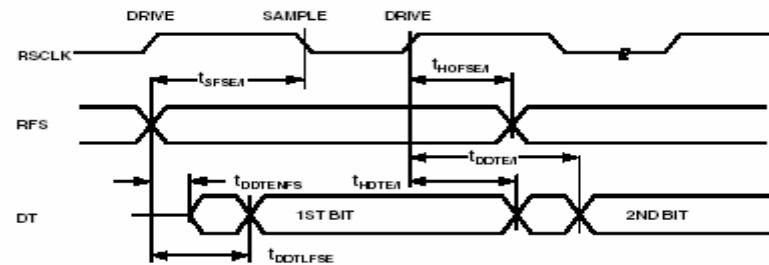

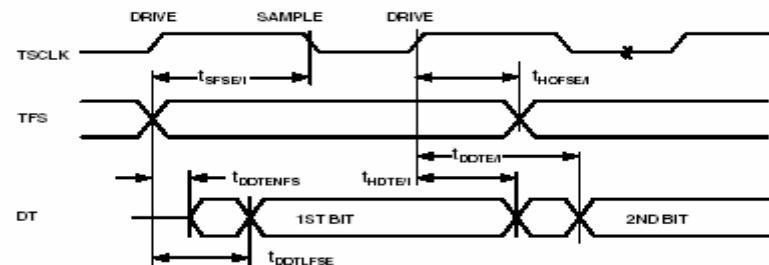

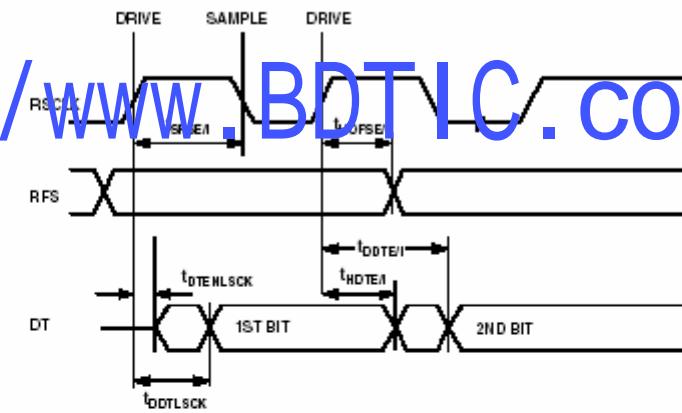

表 24. 外部迟后帧同步

| 参数          | 最小  | 最大  | 单位 |

|-------------|-----|-----|----|

| <b>开关特性</b> |     |     |    |

| t_DDTLFSE   |     | TBD | Ns |

| t_DTENLPS   | TBD |     | Ns |

<sup>1</sup> MCE=1, TFS 使能和 TFS 有效, 跟随 t\_DDTENFS 和 t\_DDTLFSE。.

<sup>2</sup> 如果外部 RFS/TFS 建立到 RCLK/TCLK > t\_SCLK / 2, 那么适用 t\_DDTLSCK 和 t\_DTENLSCK, 否则适用 t\_DDTLFSE 和 t\_DTENLPS。

EXTERNAL RFS WITH MCE = 1, MFD = 0

LATE EXTERNAL TFS

图 14. 外部迟后的帧同步（帧同步建立< $t_{sclk}/2$ ）

EXTERNAL RFS WITH MCE=1, MFD=0

LATE EXTERNAL TFS

图 15. 外部迟后的帧同步（帧同步建立> $t_{sclk}/2$ ）

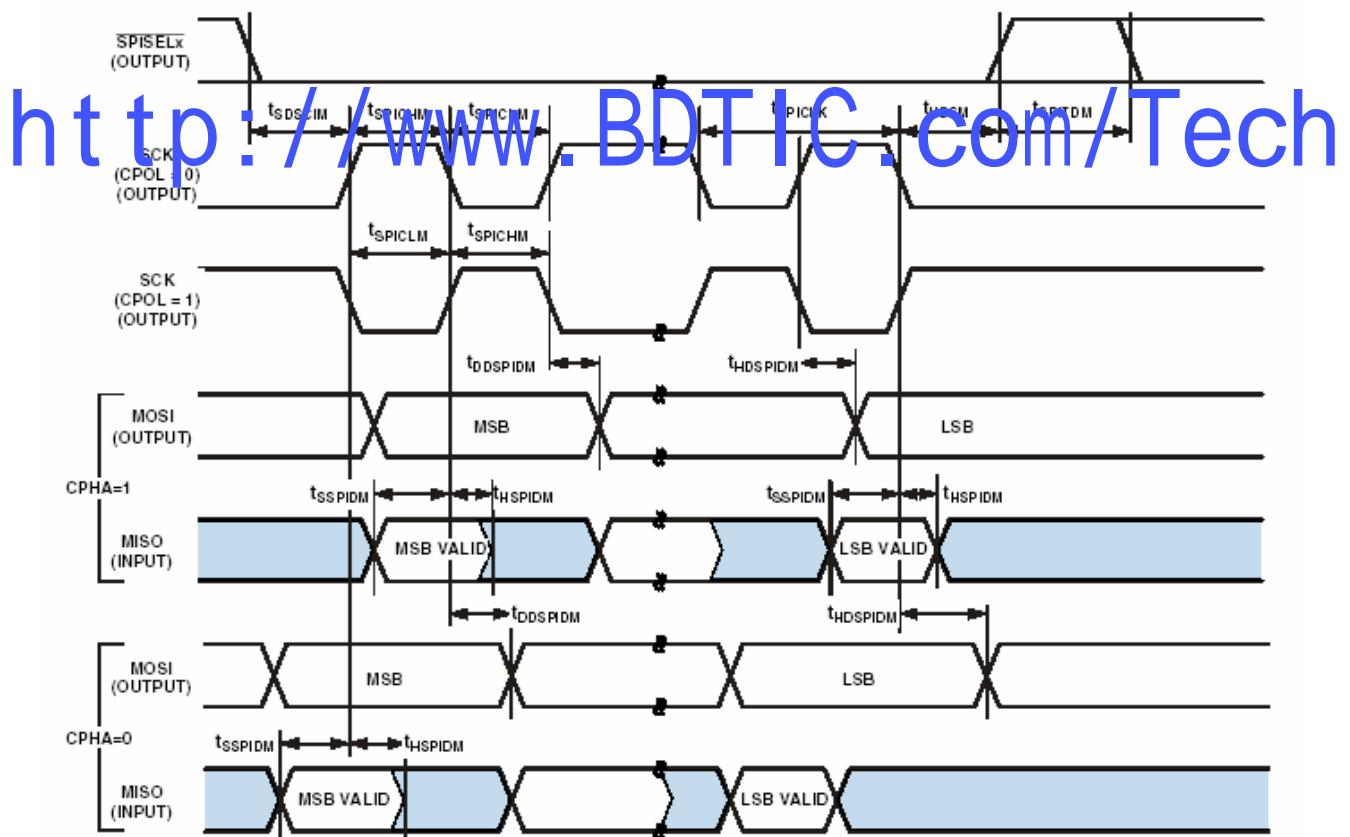

## 串行外设接口（SPI）—主时序

表 25 和图 16 描述 SPI 端口主操作。

表 25. 串行外设接口（SPI）—主时序

| 参数            |                                                       | 最小                | 最大  | 单位 |

|---------------|-------------------------------------------------------|-------------------|-----|----|

| 时序要求          |                                                       |                   |     |    |

| $t_{SSPIDM}$  | 数据输入有效到 SCK 边沿（数据输入建立）                                | TBD               |     | ns |

| $t_{HSPIDM}$  | SCK 采样边沿到数据输入无效                                       | TBD               |     | ns |

| 开关特性          |                                                       |                   |     |    |

| $t_{SDSCIM}$  | $\overline{\text{SPISELx}}$ 低到第一个 SCK 边沿 ( $x=0$ 或 1) | $2t_{SCLK} - 1.5$ |     | ns |

| $t_{SPICHM}$  | 串行时钟高电平时间                                             | $2t_{SCLK} - 1.5$ |     | ns |

| $t_{SPICLM}$  | 串行时钟低电平时间                                             | $2t_{SCLK} - 1.5$ |     | ns |

| $t_{SPICLK}$  | 串行时钟周期                                                | $4t_{SCLK} - 1.5$ |     | ns |

| $t_{HDSDM}$   | 最后 SCK 边沿到 $\overline{\text{SPISELx}}$ 高 ( $x=0$ 或 1) | $2t_{SCLK} - 1.5$ |     | ns |

| $t_{SPITDM}$  | 序列传输延迟                                                | $2t_{SCLK} - 1.5$ |     | ns |

| $t_{DDSPIDM}$ | SCK 边沿到数据输出有效（数据输出延迟）                                 | TBD               | TBD | ns |

| $t_{HDSPIDM}$ | SCK 边沿到数据输出无效（数据输出保持）                                 | TBD               | TBD | ns |

图 16. 串行外设接口（SPI）—主时序

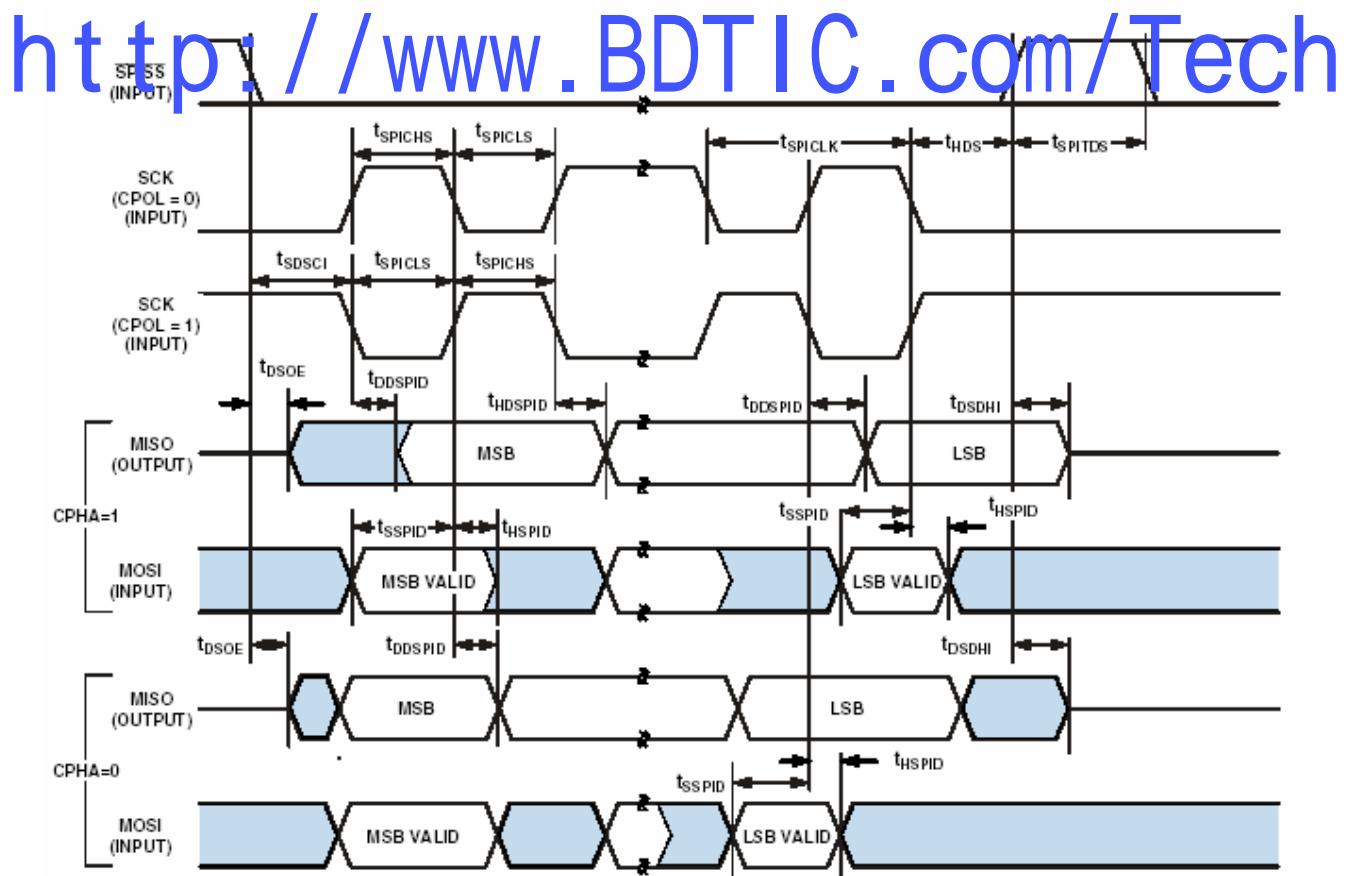

## 串行外设接口（SPI）—从时序

表 26 和图 17 描述了 SPI 端口从操作。

表 26. 串行外设接口（SPI）—从时序

| 参数           |                                    | 最小                | 最大 | 单位 |

|--------------|------------------------------------|-------------------|----|----|

| <b>时序要求</b>  |                                    |                   |    |    |

| $t_{SPICHS}$ | 串行时钟高电平时间                          | $2t_{SCLK} - 1.5$ |    | ns |

| $t_{SPICLS}$ | 串行时钟低电平时间                          | $2t_{SCLK} - 1.5$ |    | ns |

| $t_{SPICLK}$ | 串行时钟周期                             | $4t_{SCLK} - 1.5$ |    | ns |

| $t_{HDS}$    | 最后一个 SCK 边沿到 $\overline{SPISS}$ 无效 | $2t_{SCLK} - 1.5$ |    | ns |

| $t_{SPITDS}$ | 序列传输延迟                             | $2t_{SCLK} - 1.5$ |    | ns |

| $t_{SDSCI}$  | $\overline{SPISS}$ 有效到第一个 SCK 边沿   | $2t_{SCLK} - 1.5$ |    | ns |

| $t_{SSPID}$  | 数据输入有效到 SCK 边沿（数据输入建立）             | 1.6               |    | ns |

| $t_{HSPID}$  | SCK 采样边沿到数据输入无效                    | 1.6               |    | ns |

| <b>开关特性</b>  |                                    |                   |    |    |

| $t_{DSOE}$   | $\overline{SPISS}$ 有效到数据输出启动       | 0                 | 8  | ns |

| $t_{DSDHI}$  | $\overline{SPISS}$ 无效到数据高阻抗        | 0                 | 8  | ns |

| $t_{DDSPID}$ | SCK 边沿到数据输出有效（数据输出延时）              | 0                 | 10 | ns |

| $t_{HDSPID}$ | SCK 边沿到数据输出无效（数据输出保持）              | 0                 | 10 | ns |

图 17. 串行外设接口（SPI）—从时序

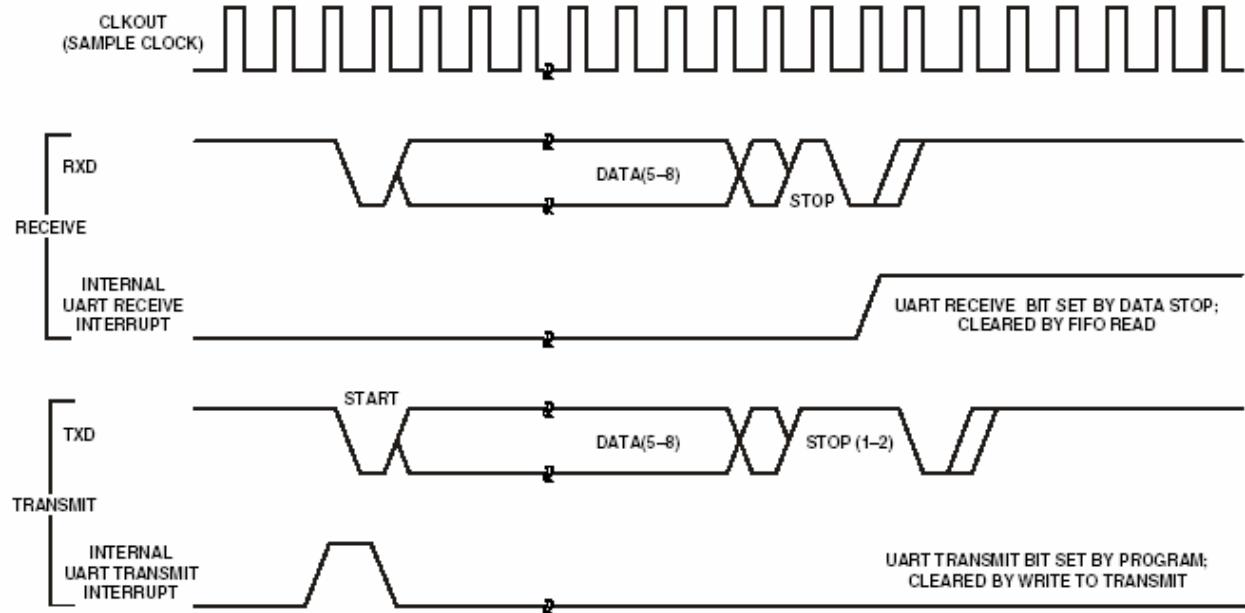

**通用异步收发器（UART）端口—接收和发送时序**

图 18 描述了 UART 端口接收和发送操作，最大波特率是 SCLK/16。如图 18 所示，在产生内部 UART 中断和外部数据操作之间有一些延迟。这些延迟同 UART 数据传输率相比可以忽略。

图 18. UART 端口—接收和发送时序

<http://www.BDTIC.com/Tech>

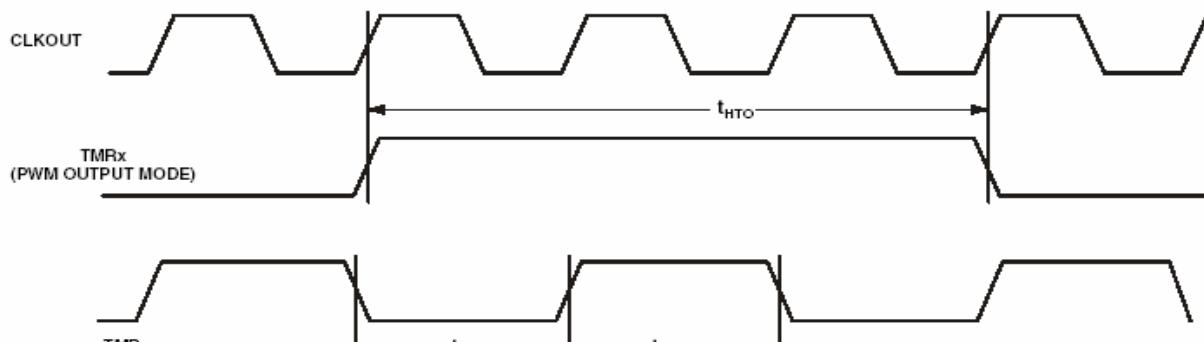

**定时器周期时序**

表 27 和图 19 描述了定时器计数满时的操作。在“宽度捕获模式”和“外部时钟模式”中输入信号是异步的，并且绝对最大输入频率为 66.5MHz。

**表 27. 定时器周期时序**

| 参数          | 最小                      | 最大                  | 单位      |

|-------------|-------------------------|---------------------|---------|

| <b>定时特性</b> |                         |                     |         |

| $t_{WL}$    | 定时器脉冲宽度输入低 <sup>1</sup> | 1                   | SCLK 周期 |

| $t_{WH}$    | 定时器脉冲宽度输入高 <sup>1</sup> | 1                   | SCLK 周期 |

| <b>开关特性</b> |                         |                     |         |

| $t_{HTO}$   | 定时器脉冲宽度输出 <sup>2</sup>  | 1<br>( $2^{32}-1$ ) | SCLK 周期 |

<sup>1</sup> 在宽度捕获和外部时钟模式中，最小脉冲宽度用于 TMRx 输入引脚。在 PWM 模式中，最小脉冲宽度也应用于 PF1 或 PPI\_CLK 输入引脚。

<sup>2</sup>  $t_{HTO}$  的最长时间是一个周期， $t_{HTO}$  的最大时间等于 ( $2^{32}-1$ ) 个周期。

图 19. 定时器 PWM\_OUT 周期时序

<http://www.BDTIC.com/Tech>

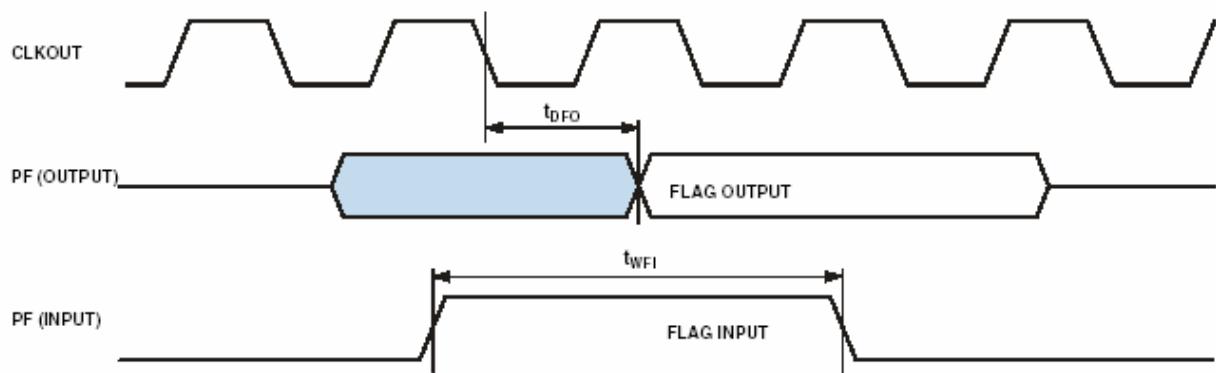

**可编程标志周期时序**

表 28 和图 20 描述了可编程标志的操作。

**表 28. 可编程标志周期时序**

| 参数                           | 最小           | 最大 | 单位 |

|------------------------------|--------------|----|----|

| 定时要求                         |              |    |    |

| $t_{WFI}$ 标志输入脉冲宽度           | $t_{SCLK}+1$ |    | ns |

| 开关特性                         |              |    |    |

| $T_{DFO}$ 标志输出相对于 CLKOUT 的延时 | TBD          |    | ns |

<http://www.BDTIC.com/Tech>

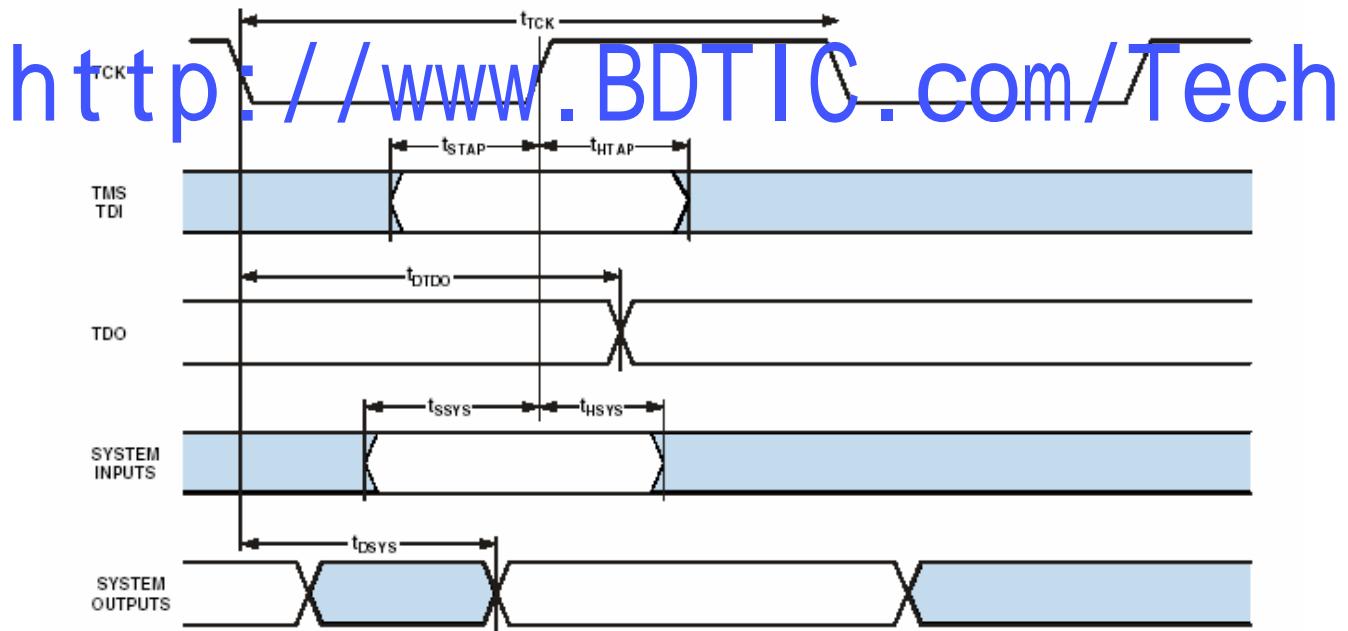

**JTAG 测试和仿真端口时序**

表 29 和图 21 描述 JTAG 端口的操作。

**表 29. JTAG 端口时序**

| 参数                 |                             | 最小 | 最大 | 单位         |

|--------------------|-----------------------------|----|----|------------|

| <b>时序参数</b>        |                             |    |    |            |

| t <sub>TCK</sub>   | TCK 周期                      | 20 |    | ns         |

| t <sub>STAP</sub>  | TCK 高电平前 TDI 和 TMS 建立       | 4  |    | ns         |

| t <sub>HTAP</sub>  | TCK 高电平后 TDI 和 TMS 保持       | 4  |    | ns         |

| t <sub>SSYS</sub>  | TCK 低电平前系统输入建立 <sup>1</sup> | 4  |    | ns         |

| t <sub>HSYS</sub>  | TCK 低电平后系统输入保持 <sup>1</sup> | 5  |    | ns         |

| t <sub>TRSTW</sub> | TRST 脉冲宽度 <sup>2</sup>      | 4  |    | TCK cycles |

| <b>开关特性</b>        |                             |    |    |            |

| t <sub>DTDO</sub>  | TCK 低电平 TDO 延迟              |    | 10 | ns         |

| t <sub>DSYS</sub>  | TCK 低电平后系统输出延迟 <sup>3</sup> | 0  | 12 | ns         |

<sup>1</sup>系统输入=DATA31-0, ARDY, TMR2-0, PF47-0, PPIx\_CLK, RSCLK0-1, RFS0-1, DR0PRI, DR0SEC, TSCLK0-1, TFS0-1, DR1PRI, DR1SEC, MOSI, MISO, SCK, RX, RESET, NMI, BMODE1-0, BR, PPIxD7-0。

<sup>2</sup>50 MHz max.

<sup>3</sup>System Outputs=DATA31-0, ADDR25-2, ABE3-0, AOE, ARE, AWE, AMS3-0, SRAS, SCAS, SWE, SCKE, CLKOUT, SA10, SMS3-0, PF47-0, RSCLK0-1, RFS0-1, TSCLK0-1, TFS0-1, DT0PRI, DT0SEC, DT1PRI, DT1SEC, MOSI, MISO, SCK, TX, BG, BGH, PPIxD7-0。

图 21. JTAG 端口时序

### 功率损耗

总的功率损耗分为两个部分：一部分是来自于内部电路( $P_{INT}$ )，另一部分是来自于外部输出驱动转换( $P_{EXT}$ )，表 30 说明了内部电路的功率损耗( $V_{DDINT}$ )，内部的功率损耗决定于所要执行的指令序列和数据操作。

表 30. 内部功率损耗

| 参数                   | 测试条件 <sup>1</sup>  |                     |                     |                     | U  |

|----------------------|--------------------|---------------------|---------------------|---------------------|----|

|                      | $f_{CCLK} = 50MHz$ | $f_{CCLK} = 400MHz$ | $f_{CCLK} = 600MHz$ | $f_{CCLK} = 600MHz$ |    |

| $I_{DDTPY}^2$        | TBD                | TBD                 | 520                 | TBD                 | mA |

| $I_{DDSLEEP}^3$      | TBD                | TBD                 | TBD                 | TBD                 | mA |

| $I_{DDDEEPSLEEP}_3$  | TBD                | TBD                 | 70                  | TBD                 | mA |

| $I_{DDHI-BERNATE}^4$ | TBD                | TBD                 | TBD                 | TBD                 | uA |

<sup>1</sup> IDD 数据是针对特定的处理器参数。所有数据都是在 25°C 测试得到的。

<sup>2</sup> 在中等程度的数据总线激活情况下，处理器执行 75% 的双乘运算和 25% 的加法运算。

<sup>3</sup> 关于 sleep 和 deepsleep 模式的区别，请参看 ADSP\_BF53x 的硬件手册。

<sup>4</sup> 是在关闭电压调节器，外部电压为 3.65V 条件下测试的。

外部损耗的部分主要是由于输出引脚的电平切换导致的，它的大小取决于以下几点：

- 每个周期需要切换的输出管脚的数目(O)

- 切换的最大频率(f)

- 负载电容(C)

- 电压摆动( $V_{DDEXT}$ )

外部消耗功率的计算：

$$P_{EXT} = O \times C \times V_{DD}^2 \times f$$

频率 f 是驱动负载先到高再回到低。比如说 DATA15-0 脚在 SDRAM 连续传输模式下，引脚电平高低变化的速率最快为  $1/23t_{SCLK}$ 。

在这样的条件下，加入一个标称的内部功率损耗值，我们就可以计算总的功率损耗的典型值：

$$P_{TOTAL} = P_{EXT} + (I_{DD} \times V_{DDINT})$$

注意由  $P_{EXT}$  导致的功率损耗最大的条件和由  $P_{INT}$  导致的功率损耗最大的条件是不一样的。 $P_{INT}$  最大的时候不可能所有的输出脚的电平都从 1 转换到 0。而且，一般的应用程序不会有 50% 或者 100% 的输出脚同时变换输出电平。

### 输出驱动电流

图 22 是 ADSP-BF561 输出驱动的典型电流-电压特性。这条曲线显示了当输出作为驱动电压应用时电流的驱动能

力。

图 22. ADSP-BF561 典型驱动

### 测试条件

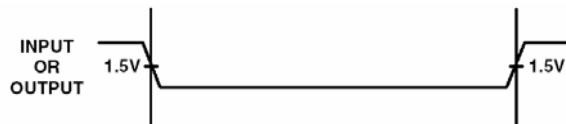

交流信号规格在时序规格中已经提到了，包括输出禁止时间，输出使能时间，还有容性负载。图 23 是 DSP 电压参考电平的时序规格。

图 23. 交流测试电压参考电平输出使能时间

当输出引脚从高阻状态变到驱动起始点时输出引脚被使能。输出使能时间  $t_{ENA}$  是指从参考信号到达高或低电平时刻到输出驱动时刻的间隔。如图 24 所示。时间  $t_{ENA\_MEASURED}$  是指参考信号到达 2.0V(输出高)或 1.0V(输出低)电平的间隔。时间  $t_{TRIP}$  是指从电平驱动时刻到参考信号电平到 2.0V(输出高)或到 1.0V(输出低)电平的间隔。

$$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$$

如果多个输出脚被使能(比如说数据总线)，测量值以第一个驱动的引脚为准。

### 输出禁止时间

输出禁止是当输出脚停止驱动，输出脚进入到高阻状态，而且从原来的驱动电平往相反的方向变化。总线电压衰弱  $\Delta V$  的时间是由容性负载  $C_L$  和输出负载电流  $I_L$  决定的。衰弱时间可以进行精确的计算：

$$t_{DECAY} = (C_L \Delta V) / I_L$$

输出禁止时间  $t_{DIS}$  是  $t_{DIS\_MEASURE}$  和  $t_{DECAY}$  的差值。 $t_{DIS\_MEASURE}$  是从参考电平变化到驱动电平衰弱  $\Delta V$  的时间间隔。 $t_{DECAY}$  是通过  $C_L$  和  $I_L$  来计算的， $\Delta V$  是 0.5V。

### 系统保持时间计算举例

为了计算特定系统的数据输出保持时间，首先利用给出的公式计算  $t_{DECAY}$ ， $\Delta V$  随着 ADSP-BF561 的输出电压

和输入电压门限所需的保持时间的不同而不同。 $\Delta v$  的典型值是 0.4V。 $C_L$  是数据总线的总电容(每根数据线),  $I_L$  是电流峰值和三态电流(每个数据线)的总和。保持时间是  $t_{DECAY}$  加上最小的禁止时间(例如: SDRAM 写周期的  $t_{DSDAT}$ )。

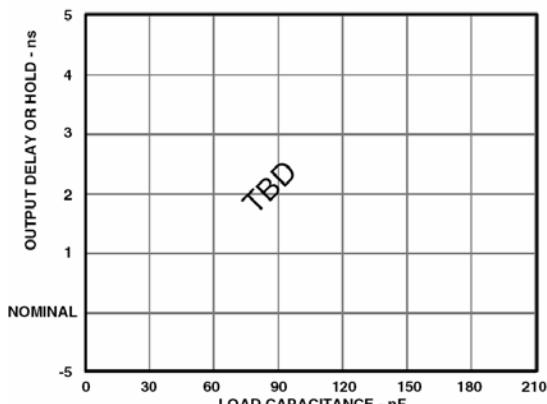

图 24. 输出最大延迟和保持时间 VS 负载电容

(在最大的外壳温度)

#### 容性负载

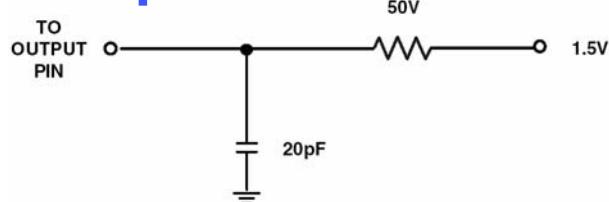

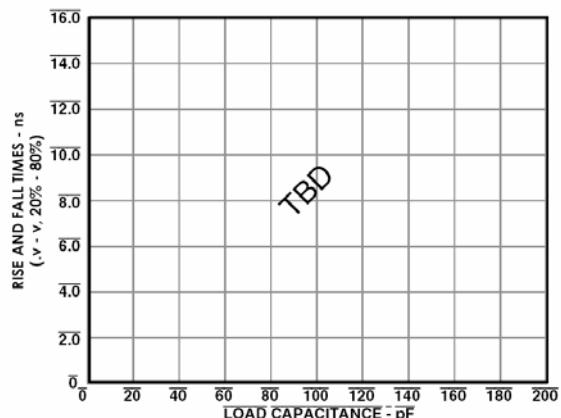

输出延迟和保持取决于标准电容负载, 所有引脚都是 30PF。图 24 是输出延迟和保持随着负载电容变化而变化的曲线。(注意, 这个图表不适用于输出禁止延迟)图 24, 图 26 和 27 可能不是线性输出

图 25. 交流测试的等效器件负载(包括所有的固件)

图 26. 典型输出上升下降时间

(10%-90% V<sub>DDEXT</sub> = Max)

图 27. 典型输出上升下降时间

(10%-90% V<sub>DDEXT</sub> = Min)

## ADSP-BF561 256-BALL MBGA 引脚配置

表 31. 256-lead MBGA 引脚分配（按球脚的名称列出）

| MBGA Pin No. | Pin Name          | MBGA Pin No. | Pin Name          | MBGA Pin No. | Pin Name       | MBGA Pin No. | Pin Name     |

|--------------|-------------------|--------------|-------------------|--------------|----------------|--------------|--------------|

| A01          | VDDEXT            | B01          | PPI2CLK           | C01          | PPI1SYNC2/TMR9 | D01          | PPI1D13/PF45 |

| A02          | ADDR24            | B02          | ADDR22            | C02          | PPI1CLK        | D02          | PPI1D15/PF47 |

| A03          | ADDR20            | B03          | ADDR18            | C03          | ADDR25         | D03          | PPI1SYNC3    |

| A04          | VDDEXT            | B04          | ADDR16            | C04          | ADDR19         | D04          | ADDR23       |

| A05          | ADDR14            | B05          | ADDR12            | C05          | GND            | D05          | GND          |

| A06          | ADDR10            | B06          | VDDEXT            | C06          | ADDR11         | D06          | GND          |

| A07          | <u>AMS3</u>       | B07          | <u>AMST</u>       | C07          | <u>AOE</u>     | D07          | ADDR09       |

| A08          | <u>AWE</u>        | B08          | <u>ARE</u>        | C08          | <u>AMSO</u>    | D08          | GND          |

| A09          | VDDEXT            | B09          | <u>SMST</u>       | C09          | <u>SMS2</u>    | D09          | ARDY         |

| A10          | <u>SMS3</u>       | B10          | SCKE              | C10          | <u>SRAS</u>    | D10          | <u>SCAS</u>  |

| A11          | SCLK0/CLKOUT      | B11          | VDDEXT            | C11          | GND            | D11          | SA10         |

| A12          | SCLK1             | B12          | <u>BR</u>         | C12          | <u>BGH</u>     | D12          | VDDEXT       |

| A13          | <u>BG</u>         | B13          | <u>ABET/SDQM1</u> | C13          | GND            | D13          | ADDR02       |

| A14          | <u>ABE2/SDQM2</u> | B14          | ADDR06            | C14          | ADDR07         | D14          | GND          |

| A15          | <u>ABE3/SDQM3</u> | B15          | ADDR04            | C15          | DATA1          | D15          | DATA5        |

| A16          | VDDEXT            | B16          | DATA0             | C16          | DATA3          | D16          | DATA6        |

| E01          | GND               | F01          | CLKIN             | G01          | XTAL           | H01          | GND          |

| E02          | PPI1D11/PF43      | F02          | VDDEXT            | G02          | GND            | H02          | GND          |

| E03          | PPI1D12/PF44      | F03          | <u>RESET</u>      | G03          | VDDEXT         | H03          | PPI1D9/PF41  |

| E04          | PPI1SYNC1/TMR8    | F04          | PPI1D10/PF42      | G04          | BYPASS         | H04          | PPI1D7       |

| E05          | ADDR15            | F05          | ADDR21            | G05          | PPI1D14/PF46   | H05          | PPI1D5       |

| E06          | ADDR13            | F06          | ADDR17            | G06          | GND            | H06          | VDDINT       |

| E07          | <u>AMS2</u>       | F07          | VDDINT            | G07          | GND            | H07          | VDDINT       |

| E08          | VDDINT            | F08          | GND               | G08          | GND            | H08          | GND          |

| E09          | <u>SMS0</u>       | F09          | VDDINT            | G09          | VDDINT         | H09          | GND          |

| E10          | <u>SWE</u>        | F10          | GND               | G10          | ADDR05         | H10          | GND          |

| E11          | <u>ABE0/SDQMO</u> | F11          | ADDR08            | G11          | ADDR03         | H11          | VDDINT       |

| E12          | DATA2             | F12          | DATA10            | G12          | DATA15         | H12          | DATA16       |

| E13          | GND               | F13          | DATA8             | G13          | DATA14         | H13          | DATA18       |

| E14          | DATA4             | F14          | DATA12            | G14          | GND            | H14          | DATA20       |

| E15          | DATA7             | F15          | DATA9             | G15          | DATA13         | H15          | DATA17       |

| E16          | VDDEXT            | F16          | DATA11            | G16          | VDDEXT         | H16          | DATA19       |

http://www.BDTIC.com/Tech

表 31. 256-lead MBGA 引脚分配（按球脚的名称列出）(续表)

| MBGA Pin No. | Pin Name         |

|--------------|------------------|--------------|------------------|--------------|------------------|--------------|------------------|

| J01          | VROUT0           | K01          | PPI1D6           | L01          | PPI1D0           | M01          | PPI2D15/PF39     |

| J02          | VROUT1           | K02          | PPI1D4           | L02          | PPI2SYNC2/TMR11  | M02          | PPI2D13/PF37     |

| J03          | PPI1D2           | K03          | PPI1D8/PF40      | L03          | GND              | M03          | PPI2D9/PF33      |

| J04          | PPI1D3           | K04          | PPI2SYNC1/TMR10  | L04          | PPI2SYNC3        | M04          | GND              |

| J05          | PPI1D1           | K05          | PPI2D14/PF38     | L05          | VDDEXT           | M05          | NC               |

| J06          | VDDEXT           | K06          | VDDEXT           | L06          | PPI2D11/PF35     | M06          | PF3/SPISEL3/TMR3 |

| J07          | GND              | K07          | GND              | L07          | GND              | M07          | PF7/SPISEL7/TMR7 |

| J08          | VDDINT           | K08          | VDDINT           | L08          | VDDINT           | M08          | VDDINT           |

| J09          | VDDINT           | K09          | GND              | L09          | GND              | M09          | GND              |

| J10          | VDDINT           | K10          | GND              | L10          | VDDEXT           | M10          | BMODE0           |

| J11          | GND              | K11          | VDDINT           | L11          | GND              | M11          | SCK              |

| J12          | DATA30           | K12          | DATA28           | L12          | DR0PRI           | M12          | DR1PRI           |

| J13          | DATA22           | K13          | DATA26           | L13          | TFS0/PF16        | M13          | NC               |

| J14          | GND              | K14          | DATA24           | L14          | GND              | M14          | VDDEXT           |

| J15          | DATA21           | K15          | DATA25           | L15          | DATA27           | M15          | DATA31           |

| J16          | DATA23           | K16          | VDDEXT           | L16          | DATA29           | M16          | DT0PRI/PF18      |

| N01          | PPI2D12/PF36     | P01          | PPI2D8/PF32      | R01          | PPI2D7           | T01          | VDDEXT           |

| N02          | PPI2D10/PF34     | P02          | GND              | R02          | PPI2D6           | T02          | PPI2D4           |

| N03          | PPI2D3           | P03          | PPI2D5           | R03          | PPI2D2           | T03          | VDDEXT           |

| N04          | PPI2D1           | P04          | PF0/SPISEL1/TMR0 | R04          | PPI2D0           | T04          | PF2/SPISEL2/TMR2 |

| N05          | PF1/SPISEL1/TMR1 | P05          | GND              | R05          | PF4/SPISEL4/TMR4 | T05          | PF6/SPISEL6/TMR6 |

| N06          | PF9              | P06          | PF5/SPISEL5/TMR5 | R06          | PF8              | T06          | VDDEXT           |

| N07          | GND              | P07          | PF11             | R07          | PF10             | T07          | PF12             |

| N08          | PF13             | P08          | PF15/EXTCLR      | R08          | PF14             | T08          | VDDEXT           |

| N09          | TDO              | P09          | GND              | R09          | NMI1             | T09          | TCK              |

| N10          | BMODE1           | P10          | TRST             | R10          | TDI              | T10          | TMS              |

| N11          | MOSI             | P11          | NMIO             | R11          | BR               | T11          | SLEEP            |

| N12          | GND              | P12          | GND              | R12          | MISO             | T12          | VDDEXT           |

| N13          | RFS1/PF24        | P13          | RSCLK1/PF30      | R13          | TX/PF26          | T13          | RX/PF27          |

| N14          | GND              | P14          | TFS1/PF21        | R14          | TSCLK1/PF31      | T14          | DR1SEC/PF25      |

| N15          | DT0SEC/PF17      | P15          | RSCLK0/PF28      | R15          | DT1PRI/PF23      | T15          | DT1SEC/PF22      |

| N16          | TSCLK0/PF29      | P16          | DR0SEC/PF20      | R16          | RFS0/PF19        | T16          | VDDEXT           |

http://www.BDTIC.com/Tech

## ADSP-BF561 297-BALL PBGA 引脚配置

表 32. 297-lead PBGA 引脚分配（按球脚的名称列出）

| MBGA Pin No. | Pin Name     | MBGA Pin No. | Pin Name         | MBGA Pin No. | Pin Name         | MBGA Pin No. | Pin Name    |

|--------------|--------------|--------------|------------------|--------------|------------------|--------------|-------------|

| A01          | GND          | AB03         | GND              | AE11         | PF12             | AF17         | SLEEP       |

| A02          | ADDR25       | AB24         | GND              | AE12         | PF14             | AF18         | NMI0        |

| A03          | ADDR23       | AB25         | TFS0/PF16        | AE13         | NC               | AF19         | SCK         |

| A04          | ADDR21       | AB26         | DR0PRI           | AE14         | TDO              | AF20         | TX/PF26     |

| A05          | ADDR19       | AC01         | PPI2D9/PF33      | AE15         | TRST             | AF21         | RSCLK1/PF30 |

| A06          | ADDR17       | AC02         | PPI2D8/PF32      | AE16         | EMU              | AF22         | DR1PRI      |

| A07          | ADDR15       | AC03         | GND              | AE17         | BMODE1           | AF23         | TSCLK1/PF31 |

| A08          | ADDR13       | AC04         | GND              | AE18         | BMODE0           | AF24         | DT1SEC/PF22 |

| A09          | ADDR11       | AC23         | GND              | AE19         | MISO             | AF25         | DT1PRI/PF23 |

| A10          | ADDR09       | AC24         | GND              | AE20         | MOSI             | AF26         | GND         |

| A11          | AMS3         | AC25         | DROSEC/PF20      | AE21         | RX/PF27          | B01          | PPI2CLK     |

| A12          | AMST         | AC26         | RFS0/PF19        | AE22         | RFS1/PF24        | B02          | GND         |

| A13          | AWE          | AD01         | PPI2D7           | AE23         | DR1SEC/PF25      | B03          | ADDR24      |

| A14          | ARE          | AD02         | PPI2D6           | AE24         | TFS1/PF21        | B04          | ADDR22      |

| A15          | SMS0         | AD03         | GND              | AE25         | GND              | B05          | ADDR20      |

| A16          | SMS2         | AD04         | GND              | AE26         | NC               | B06          | ADDR18      |

| A17          | SRAS         | AD05         | GND              | AF01         | GND              | B07          | ADDR16      |

| A18          | SCAS         | AD22         | GND              | AF02         | PPI2D4           | B08          | ADDR14      |

| A19          | SCLK0/CLKOUT | AD23         | GND              | AF03         | PPI2D2           | B09          | ADDR12      |

| A20          | SCLK1        | AD24         | GND              | AF04         | PPI2D0           | B10          | ADDR10      |