# NM7010B<sup>+</sup> Datasheet (Ver. 1.1)

©2007 WIZnet Co., Inc. All Rights Reserved.

For more information, visit our website at <a href="http://www.wiznet.co.kr">http://www.wiznet.co.kr</a>

## **Document History Information**

| Revision | Data          | Description                                 |

|----------|---------------|---------------------------------------------|

| Ver. 1.0 | OCTOBER, 2006 | Release with NM7010B <sup>+</sup> Launching |

| Ver. 1.1 | June 29, 2007 | Add SPI signal Pin description(A14-A11)     |

### **WIZnet's Online Technical Support**

If you have something to ask about WIZnet Products, Write down your question on Q&A Board in WIZnet website (<a href="www.wiznet.co.kr">www.wiznet.co.kr</a>). WIZnet Engineer will give an answer as soon as possible.

#### NM7010B<sup>+</sup> Datasheet

#### <CONTENTS>

- 1.Introduction

- 1-1. Introduction

- 1-2. Block Diagram

- 2. Pin Assignments & Descriptions

- 2-1 Pin Assignments

- 2-2. Power & Ground

- 2-3 MCU Interfaces

- 2-4 Network Status & LEDs

- 2-5 Miscellaneous Signals

- 3. Timing Diagram

- 4. Dimensions

- 5. Connector Specification

#### 1. Introduction

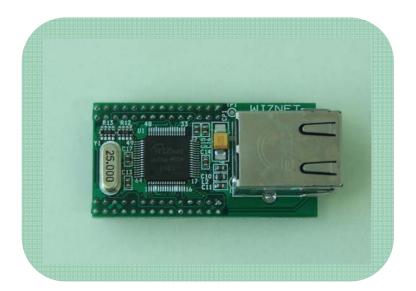

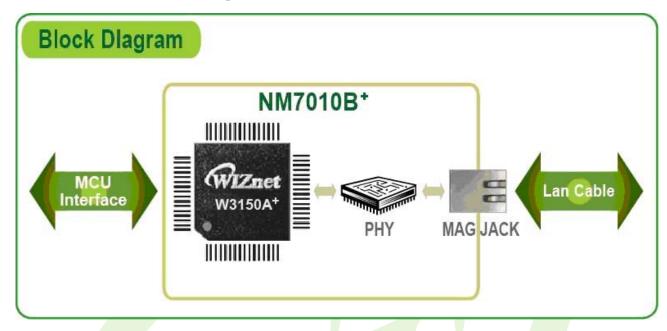

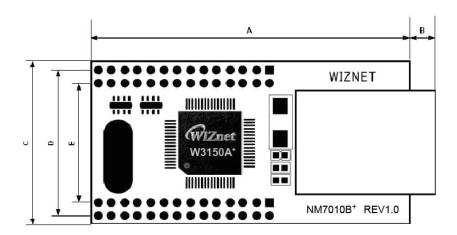

NM7010B<sup>+</sup> is the network module that includes W3150A<sup>+</sup> (TCP/IP hardwired chip), Ethernet PHY (RTL8201CP), MAG-JACK (RJ45 with X'FMR) with other glue logics. It can be used as a component and no effort is required to interface W3150A<sup>+</sup> and PHY chip. The NM7010B<sup>+</sup> is an ideal option for users who want to develop their Internet enabling systems rapidly.

NM7010B<sup>+</sup> consists of W3150A<sup>+</sup>, Ethernet PHY and MAG-JACK.

- TCP/IP, MAC protocol layer: W3150A<sup>+</sup>

- Physical layer: Ethernet PHY

- Connector: MAG-JACK

#### 1.1. Features

- Supports 10/100 Base TX

- Supports half/full duplex operation

- Supports auto-negotiation and auto crossover detection

- IEEE 802.3/802.3u Complaints

- Operates 3.3V with 5V I/O signal tolerance

- Supports network status indicator LEDs

- Includes Hardware Internet protocols: TCP, IP Ver.4, UDP, ICMP, ARP, PPPoE, IGMP

- Includes Hardware Ethernet protocols: DLC, MAC

- Supports 4 independent connections simultaneously

- Supports MCU bus Interface and SPI Interface

- Supports Direct/Indirect mode bus access

- Supports Socket API for easy application programming

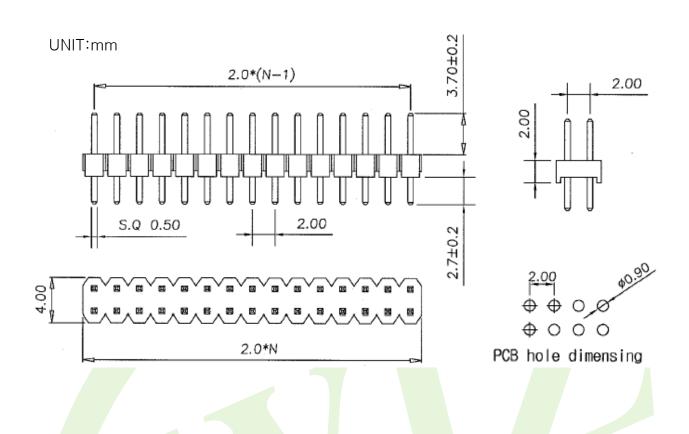

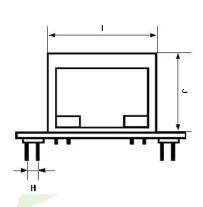

- Interfaces with Two 2.0mm pitch 2 \* 14 header pin

#### 1.2. Block Diagram

# 2. Pin Assignments & descriptions

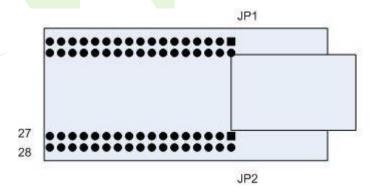

## 2.1. Pin Assignments

|     |    | JP | 1   |       |        |    | JP2 | -  |          |

|-----|----|----|-----|-------|--------|----|-----|----|----------|

| VCC | 1  |    | • 2 | лит   | GND    | 1  |     | 2  | /RESET   |

| MR  | 3  | •  | • 4 | /RD   | NC     | 3  |     | 4  | GND      |

| /CS | 5  | •  | •   | NC NC | NC     | 5  |     | 6  | L_COL    |

| A14 | 7  | •  | •   | GND   | GND    | 7  |     | 8  | L_100ACT |

| A12 | 9  | •  | •   | 0 A13 | SPI_EN | 9  |     | 10 | L_10ACT  |

| A10 | 11 | •  | •   | 2 A11 | L_DUPX | 11 |     | 12 | L_LINK   |

| GND | 13 | •  | •   | 4 A9  | GND    | 13 |     | 14 | GND      |

| A8. | 15 | •  | •   | 6 A7  | D1     | 15 |     | 16 | D0       |

| A6  | 17 | •  | •   | 8 A5  | D3     | 17 |     | 18 | D2       |

| A4  | 19 | •  | • 2 | 20 A3 | D5     | 19 |     | 20 | D4       |

| A2  | 21 | •  | •   | 2 A1  | D7     | 21 |     | 22 | D6       |

| A0  | 23 | •  | • 2 | 4 GND | GND    | 23 |     | 24 | vcc      |

| NC  | 25 | •  | • 2 | 26 NC | NC     | 25 |     | 26 | NC       |

| NC  | 27 | •  | • 2 | 8 NC  | NC     | 27 |     | 28 | NC       |

I : Input O : Output I/O : Bi-directional Input and output P : Power

## 2.2. Power & Ground

| Symbol | Туре | Pin No.            | Description               |

|--------|------|--------------------|---------------------------|

| VCC    | Р    | JP1:1, JP2:24      | Power: 3.3 V power supply |

| GND    | Р    | JP1:8, JP1:13,     | Ground                    |

|        |      | JP1 : 24, JP2 : 1  |                           |

|        |      | JP2 : 4, JP2 : 7   |                           |

|        |      | JP2 : 13, JP2 : 14 |                           |

|        |      | JP2 : 23           |                           |

### 2.3. MCU Interfaces

| Symbol | Туре | Pin No.             | Description                                             |

|--------|------|---------------------|---------------------------------------------------------|

| A14    | ı    | JP1:7               | ADDRESS PIN OR SCLK(Serial Clock)                       |

|        |      |                     | This pin is used to select a register or memory.        |

|        |      |                     | When asserting SPI_EN pin high, this pin is used to     |

|        |      |                     | SPI Clock signal Pin.                                   |

| A13    | 1    | JP1 : 10            | ADDRESS PIN or /SS (Slave Select) *                     |

|        |      |                     | This pin is used to select a register or memory.        |

|        |      |                     | When asserting SPI_EN pin high, this pin is used to     |

|        |      |                     | SPI Slave Select signal Pin. In only SPI Mode, this pin |

|        |      |                     | is active low                                           |

| A12    | I    | JP1:9               | ADDRESS PIN or MOSI (Master Out Slave In) *             |

|        |      |                     | This pin is used to select a register or memory.        |

|        |      |                     | When asserting SPI_EN pin high, this pin is used to     |

|        |      |                     | SPI MOSI signal pin.                                    |

| A11    | I/O  | JP1 : 12            | ADDRESS PIN or MISO (Master In Slave Out) *             |

|        |      |                     | This pin is used to select a register or memory.        |

|        |      |                     | When asserting SPI_EN pin high, this pin is used to     |

|        |      |                     | SPI MISO signal pin.                                    |

| A10~A8 | 1    | JP1 : 11, JP1 : 14  | Address                                                 |

|        |      | JP1 : 15            | Used as Address[10-8] pin                               |

| A7~A0  | 1    | JP1 : 16 ~ JP1 : 23 | Address                                                 |

|        |      |                     | Used as Address[7-0] pin                                |

| D7~D0  | I/O  | JP2 : 21, JP2 : 22  | Data                                                    |

|        |      | JP2 : 19, JP2 : 20  | 8 bit-wide data bus                                     |

|        |      | JP2 : 17, JP2 : 18  |                                                         |

|        |      | JP2 : 15, JP2 : 16  |                                                         |

| /CS    | I    | JP1 : 5             | Module Select : Active low.                             |

|        |      |                     | /CS of W3150A <sup>+</sup>                              |

| /RD    | I    | JP1 : 4             | Read Enable : Active low.                               |

|        |      |                     | /RD of W3150A <sup>+</sup>                              |

| /WR    | I    | JP1 : 3             | Write Enable : Active low                               |

|        |      |                     | /WR of W3150A <sup>+</sup>                              |

| /INT | 0 | JP1 : 2 | Interrupt : Active low                                      |

|------|---|---------|-------------------------------------------------------------|

|      |   |         | After reception or transmission it indicates that the       |

|      |   |         | W3150A <sup>+</sup> requires MCU attention.                 |

|      |   |         | By writing values to the Interrupt Status Register of       |

|      |   |         | W3150A <sup>+</sup> the interrupt will be cleared.          |

|      |   |         | All interrupts can be masked by writing values to the       |

|      |   |         | IMR of W3150A <sup>+</sup> (Interrupt Mask Register).       |

|      |   |         | For more details refer to the W3150A <sup>+</sup> Datasheet |

#### 2.4. Network status & LEDs

You can observe the network status using MAC-JACK LEDs. LED interface can be extended to the LED of the main board.

| Symbol   | Туре | Pin No.  | Description                                           |

|----------|------|----------|-------------------------------------------------------|

| L_COL    | 0    | JP2 : 6  | Collision LED: Active low when collisions occur.      |

|          |      |          | Link 100/ACT LED: Active low when linked by 100       |

| L_100ACT | 0    | JP2 : 8  | Base TX, and blinking when transmitting or receiving  |

|          |      |          | data.                                                 |

| I 40ACT  | 0    | JP2 : 10 | Link 10/ACT LED: Active low when linked by 10 Base    |

| L_10ACT  | U    | JP2 . 10 | T, and blinking when transmitting or receiving data.  |

| I DUDY   | 0    | ID0 : 44 | Full Duplex LED : Active low when in full duplex      |

| L_DUPX   | 0    | JP2 : 11 | operation. Active high when in half duplex operation. |

| L_LINK   | 0    | JP2 : 12 | Link LED : Active low when linked                     |

# 2.5. Miscellaneous Signals

| Symbol  | Туре | Pin No.                      | Description                                              |

|---------|------|------------------------------|----------------------------------------------------------|

|         |      |                              | Reset : Active low                                       |

| /RESET  |      | JP2 : 2                      | Reset W3150A, RTL8201BL chip. For                        |

| 7.12021 | ·    | 012.2                        | complete reset function this pin must be                 |

|         |      |                              | asserted low for at least 10ms.                          |

|         |      |                              | SPI Enable                                               |

|         |      |                              | This pin selects Enable/disable W3150A+                  |

|         |      |                              | SPI Mode                                                 |

|         |      |                              | This pin is internally pulled low for previous           |

|         |      |                              | W3150A users. Even if there is no signal                 |

| SPI_EN  | 1    | JP2:9                        | connection to this pin, it asserts low                   |

|         |      |                              | internally. So change to new version                     |

|         |      |                              | W3150A <sup>+</sup> including SPI interface, there is no |

|         |      |                              | effort to change previous board design.                  |

|         |      |                              | Low = Disable W3150A <sup>+</sup> SPI Mode               |

|         |      |                              | High = Enable W3150A <sup>+</sup> SPI Mode               |

| NC      |      | JP1: 6, 25, 26, 27, 28       | Not Connect                                              |

| NC      | -    | JP2: 3, 5, 9, 25, 26, 27, 28 |                                                          |

# 3. Timing Diagrams

NM7010B<sup>+</sup> provides following interfaces of W3150A<sup>+</sup>

- -. Direct/Indirect mode bus access

- -. SPI access

Refer to W3150A<sup>+</sup> datasheet for timing of NM7010B<sup>+</sup>

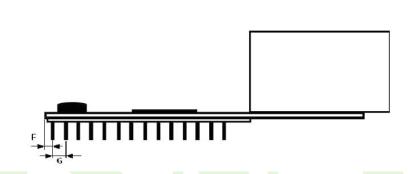

## 4. Dimensions

| 5 | Symbols | Dimensions (mm) |

|---|---------|-----------------|

|   | Α       | 48.0            |

|   | В       | 4.0             |

|   | С       | 25.0            |

|   | D       | 22.4            |

| Е |         | 18.4            |

| F |         | 1.0             |

| G |         | 2.0             |

| Н |         | 2.0             |

|   | 1       | 16.0            |

|   | J       | 13.4            |

# 5. Connector Specification