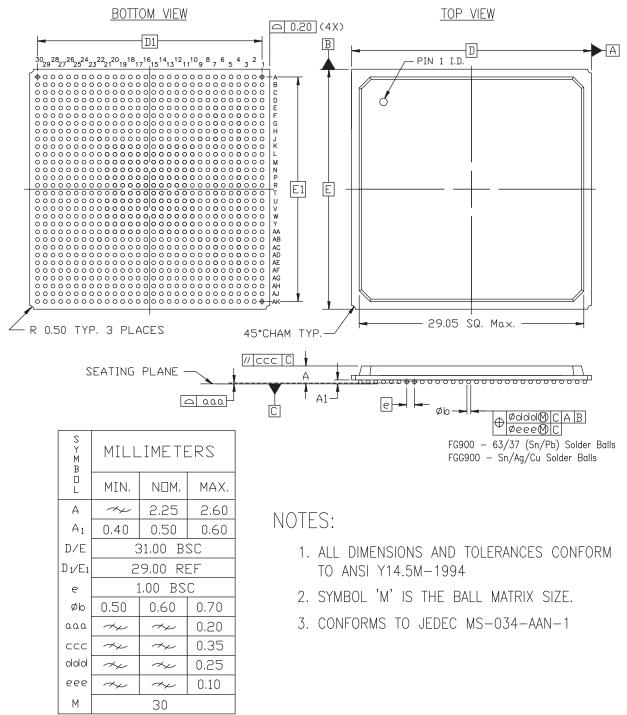

## Fine-Pitch BGA (FG900/FGG900) Package

PK038 (v1.4) November 12, 2009

PK038\_01\_110309

© 2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## Revision History

The following table shows the revision history for this document.

| Date     | Version | Description of Revisions                                                                                                                                      |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/12/09 | 1.3     | Removed note 3 regarding component land diameter. This dimension is specified in <u>UG112</u> , Device Package User Guide under Recommended PCB Design Rules. |

| 11/12/09 | 1.4     | Changed symbol ddd value from 0.30 to 0.25 to conform to JEDEC MS-034.                                                                                        |

## Notice of Disclaimer

Xilinx regards this materials data to be correct but makes no guarantee as to its accuracy or completeness, including, but not limited to, with respect to its compliance with applicable environmental laws and regulations. Xilinx subcontracts the production, test and assembly of hardware devices to independent third-party vendors and materials suppliers ("Contractors"). All data provided hereunder is based on information received from Contractors. Xilinx has not independently verified the accuracy or completeness of this information which is provided solely for your reference in connection with the use of Xilinx products.