EN051 (v1.3) June 8, 2007

**Errata Notification**

# Introduction

Although Xilinx has made every effort to ensure the highest possible quality, these Virtex<sup>™</sup>-5 engineering samples (ES) are subject to the limitations described in the following errata.

# **Devices**

These errata apply to the Virtex-5 devices, as shown in Table 1.

Table 1: Virtex-5 Devices Affected by These Errata

| Devices      | XC5VLX30TCES  | JTAG ID (Revision Code): 2, 3, 4, 5 |  |

|--------------|---------------|-------------------------------------|--|

|              | XC5VLX50TCES  | JTAG ID (Revision Code): 2, 3, 4, 5 |  |

|              | XC5VLX110TCES | JTAG ID (Revision Code): 2, 4       |  |

|              | XC5VLX330TCES | JTAG ID (Revision Code): 0, 1       |  |

| Packages     | All           |                                     |  |

| Speed Grades | -1, -2        |                                     |  |

# **Hardware Errata Details**

This section provides a detailed description of each hardware issue known at the release time of this document.

#### **Block RAM**

# Block RAM Synchronous FIFO Mode - LX30T, LX50T, and LX110T

$F_{MAX\ FIFO}$  is 400 MHz when using the attribute EN\_SYN = TRUE.

#### Block RAM ECC Scrub Mode

ECC Scrub mode (EN\_ECC\_SCRUB = TRUE) is not supported and will not be supported in production devices.

#### **OSERDES**

Optional inversion for the divided clock (CLKDIV) in the OSERDES is not supported.

### Configuration

When reconfiguring with a different bitstream on an already configured device, in rare cases a static LUT input can be inverted. For more information see answer record 24582.

# Integrated Endpoint Block for PCI Express

#### 6-Pin Reset Mode - LX30T and LX50T

The CRMMACRSTN and CRMLINKRSTN pins are not supported. The RESETMODE attribute must be set to FALSE which selects the 4-pin reset scheme described in <u>UG197</u>: *PCI Express Endpoint Block User Guide*.

Users of the LogiCORE Endpoint Block Plus for PCI Express<sup>™</sup> (v1.2.1 or later with EA patch) are not affected by this errata. The LogiCORE<sup>™</sup> Endpoint Block for PCI Express<sup>™</sup> (v1.1 or later) implements this workaround for LX50T devices by always setting RESETMODE to FALSE.

© 2006–2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. PowerPC is a trademark of IBM Inc. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

# Unsupported Status Output Pins - LX30T and LX50T

The following status output pins are unsupported. They are used to indicate register values set by the Root Complex in the Configuration Space. For specific pin descriptions, refer to UG197: PCI Express Endpoint Block User Guide.

- IOSPACEENABLE

- MEMSPACEENABLE

- · BUSMASTERENABLE

- · PARITYERRORRESPONSE

- · SERRENABLE

- · INTERRUPTDISABLE

- URREPORTINGENABLE

- MAXPAYLOADSIZE[2:0]

- MAXREADREQUESTSIZE[2:0]

#### Workaround

The register values can be read through the Management interface. Users of the LogiCORE Endpoint Block Plus for PCI Express (v1.2.1 or later with EA patch) are not affected by this errata. The information present in these signals is made available at the interface. The LogiCORE Endpoint Block for PCI Express (v1.1 or later) does not incorporate this workaround.

# Management Interface - LX30T and LX50T

The Management read enable input pin MGMTRDEN must be tied High when the Management interface is used.

#### Workaround

Tie MGMTRDEN High. The LogiCORE Endpoint Block for PCI Express (v1.3 or later) implements this workaround. Users of the LogiCORE Endpoint Block Plus for PCI Express (v1.2.1 or later with EA patch) are not affected by this errata.

# Configuration Space

Some configuration space register bits are incorrectly set, however, the functionality is not affected.

- The following bits are incorrectly set to 1 LX30T, LX50T, and LX110T

- · The Data Link Layer Link Active Reporting Capable bit [20] of the Link Capabilities register

- · The Data Link Layer Link Active bit [13] of the Link Status Register

- For all devices listed in Table 1 LX30T, LX50T, LX110T, and LX330T

- · The Version field of the Power Management capability is incorrectly set to 010b

### Error Reporting

Error Signaling Message Transaction Layer Packets are incorrectly sent for Ignored Messages, Unsupported Requests, and Poisoned TLPs.

# Transaction Layer Interface

Gaps in user request receive data destination (LLKRXDSTREQN) cannot be longer than four cycles, unless the gaps are between packets.

#### Workaround

Prevent gaps in LLKRXDSTREQN of longer than four cycles. Users of the LogiCORE Endpoint Block Plus for PCI Express (v1.2.1 or later with EA patch) are not affected by this errata. Users of the LogiCORE Endpoint Block for PCI Express (v1.1 or later) must implement this work around.

LLKRXDSTREQN must be deasserted in the same cycle that LLKRXSRCLASTREQN is asserted.

#### Workaround

Deassert LLKRXDSTREQN in the same cycle that LLKRXSRCLASTREQN is asserted. The LogiCORE Endpoint Block Plus for PCI Express (v1.2.1 or later with EA patch) implements this workaround. This workaround is not incorporated in the LogiCORE Endpoint Block for PCI Express (v1.1 or later).

# Transaction Ordering

The transaction ordering implemented by the Virtex-5 Integrated Endpoint block for PCI Express designs has the following differences from the PCI Express base specification, revision 1.1, Table 2-23.

- Completion packets can be blocked by non-posted packet requests.

#### Workaround

A user application waiting for a completion packet must drain the non-posted queue to ensure that the completion packet already in the Rx buffer can be drained. In addition, if a far-end device is waiting for a completion packet, the far-end device must free up non-posted flow control credits before the Integrated Endpoint block will transmit a completion packet waiting in its Tx buffer. This workaround is not incorporated in the LogiCORE Endpoint Block Plus for PCI Express (v1.2.1 or later with EA patch) or the LogiCORE Endpoint Block for PCI Express (v1.1 or later).

- Packets without flow control credits can sometimes be transmitted, when a link partner does not advertise infinite completion flow control credits and the endpoint is in an 8-lane configuration, causing flow control protocol errors.

#### Workaround

The user application must put posted packets in the transmit queue only if sufficient credits are available.

Posted packets waiting for flow control credits in the transmit buffer can sometimes be passed by completion or non-posted packets. For example, a memory read packet could pass a memory write packet with overlapping addresses, resulting in incorrect data being read. After this violation occurs, transmission of completion packets and/or non-posted packets could be halted if the posted packet buffer becomes empty. Transmission of completion packets and/or non-posted packets in the buffer will resume once a new posted packet is transmitted

#### Workaround

The user application must put posted packets in the transmit queue only if sufficient credits are available.

#### GTP Transceivers

# AC JTAG

AC JTAG mode is not supported and will not be supported in production devices.

#### GTP CRC Block - LX30T and LX50T

The initial state for the cyclic-redundancy-check (CRC) block, CRC64 and CRC32, cannot be changed from its default value of 32 'hfffffff.

# GTP CRC Parallel Interface Timing

For proper timing, the parallel CRCIN interface must be clocked off of an inverted CRCCLK and sourced from a register clocked on the noninverted CRCCLK in the CLB fabric. The CRC CORE Generator™ Wizard generates wrapper files that include this circuitry. See Answer Record #24879 for more details.

### GTP Transmit Interface Timing

For proper timing, the transmit interface must be clocked off of an inverted TXUSRCLK2 and sourced from a register clocked on the noninverted TXUSRCLK2 in the CLB fabric. The GTP CORE Generator Wizard generates wrapper files that include this circuitry.

# RX Buffer Bypass (RX Low Latency Mode)

The receiver buffer bypass mode is only supported for 10-bit internal data paths with a receiver PLL divider of 1. Receiver PLL divider settings of 2 or 4 are not currently supported.

# Reference Clock Input Resistance

The differential input resistance  $R_{IN}$  of the RocketIO GTP reference clock ranges from 160 $\Omega$  to 180 $\Omega$ . The higher resistance should not affect the performance of the GTP transceiver.

# **Operational Guidelines**

# **Design Software Requirements**

The devices covered by these errata, unless otherwise specified, require the following Xilinx development software installations.

- Speed specification v1.48 (or later) and Xilinx software ISE 8.2i SP3 (or later) is required when designing for the devices covered by this errata.

- The stepping should be set to ES in the constraint file (UCF file):

CONFIG STEPPING = "ES";

A summary list of ISE software known issues pertaining to the Virtex-5 features is available at: http://www.xilinx.com/xlnx/xil\_ans\_display.jsp?iCountryID=1&iLanguageID=1&getPagePath=23625

#### **Notes and Recommendations**

### **ESD Protection**

For LX30T, LX50T, and LX110T:

- The V<sub>BATT</sub> pin ESD protection meets HBM 500V.

- The MGTREFCLKN, MGTREFCLKP, and MGTVREF pins ESD protection meet HBM 250V and 100V CDM. Added care is recommended during handling.

#### For LX330T:

- The MGTREFCLKN, MGTREFCLKP, and MGTVREF pins ESD protection meet HBM 1000V and 150V CDM. Added care is recommended during handling.

# Power Supply Requirements - LX30T, LX50T, and LX110T

During power-up and configuration, the V<sub>CCINT</sub> supply requires a maximum current I<sub>CCINT</sub> as shown in Table 2.

Table 2: V<sub>CCINT</sub> Power Supply Maximum Current Requirements

| Device        | V <sub>CCINT</sub> | I <sub>CCINT</sub> |

|---------------|--------------------|--------------------|

| XC5VLX30TCES  | 1.05V              | 2.5A               |

| XC5VLX50TCES  | 1.05V              | 2.75A              |

| XC5VLX110TCES | 1.05V              | 4.00A              |

# **Traceability**

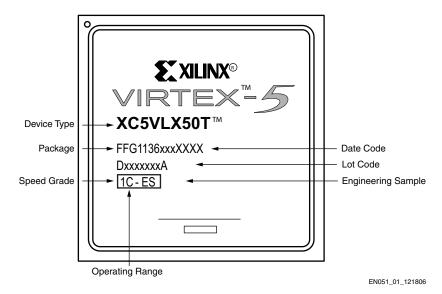

The XC5VLX50TCES is marked as shown in Figure 1. The other devices listed in Table 1 are marked similarly.

Figure 1: Example XC5VLX50TCES Package Marking

# **Additional Questions or Clarifications**

All other device functionality and timing meet the current data sheet specifications.

For additional questions regarding these errata, please contact your Xilinx Technical Support: <a href="http://www.xilinx.com/support/clearexpress/websupport.htm">http://www.xilinx.com/support/clearexpress/websupport.htm</a> or your Xilinx Sales Representative: <a href="http://www.xilinx.com/company/contact.htm">http://www.xilinx.com/company/contact.htm</a>.

# **Obtaining the Most Recent Errata Version**

If this document is printed or saved locally in electronic form, check for the most recent release, available to registered users on the Xilinx website at: http://www.xilinx.com/xlnx/xweb/xil\_publications\_index.jsp?category=Errata.

To receive an e-mail alert when this document changes, sign up at:

http://www.xilinx.com/xlnx/xil ans display.jsp?getPagePath=18815.

These errata apply to the following Virtex-5 documents:

Virtex-5 Overview (http://www.xilinx.com/bvdocs/publications/ds100.pdf)

Virtex-5 Data Sheet (http://www.xilinx.com/bvdocs/publications/ds202.pdf)

Virtex-5 User Guide (http://www.xilinx.com/bvdocs/userguides/ug190.pdf)

Virtex-5 XtremeDSP™ Design Considerations (http://www.xilinx.com/bvdocs/userguides/ug193.pdf)

Virtex-5 Configuration Guide (http://www.xilinx.com/bvdocs/userguides/ug191.pdf)

Virtex-5 Packaging and Pinout Specification (http://www.xilinx.com/bvdocs/userguides/ug195.pdf)

Virtex-5 RocketIO GTP Transceiver User Guide (http://www.xilinx.com/bvdocs/userguides/ug196.pdf)

Virtex-5 PCI Express Endpoint Block User Guide (http://www.xilinx.com/bvdocs/userguides/ug197.pdf)

Virtex-5 Embedded Tri-mode Ethernet MAC User Guide (http://www.xilinx.com/bvdocs/userguides/ug194.pdf)

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                          |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/17/06 | 1.0     | Initial Xilinx release.                                                                                                                                                                                              |

| 01/18/07 | 1.1     | Added XC5VLX330TCES devices and speed grade - 2 to Table 1 and sections of the document. Revised the Integrated Endpoint Block for PCI Express errata. Revised RX Buffer Bypass section on page 3. Updated Figure 1. |

| 04/09/07 | 1.2     | Added Configuration errata. Updated the GTP CRC Parallel Interface Timing section. Added device-specific information to ESD Protection and Power Supply Requirements - LX30T, LX50T, and LX110T sections.            |

| 06/08/07 | 1.3     | Added Block RAM ECC Scrub Mode, OSERDES, and AC JTAG errata. Updated LogiCORE Endpoint Block Plus for PCI Express revision information.                                                                              |