# FAQ: Implications of XCN07025

XTP027 (v1.0.1) June 15, 2009

### Q1. Why is Xilinx standardizing to 10-layer for Virtex-5 packages with more than 1000 pins?

A. With FPGA I/O interface performance, signal count, and density continuing to increase, signal integrity demands on FPGA packages (especially larger packages) have increased as well. Recognizing these increasing demands, Xilinx has decided to enhance our large (>1000 pins) Virtex®-5 packages with two additional layers to further improve I/O noise margin.

### Q2. What are the differences between the 8-layer and 10-layer packages?

A. The 10-layer package has one additional  $V_{CCO}$  layer and one additional GND layer. There has been no change to the signal routing,  $V_{CCINT}$  or  $V_{CCAUX}$  structures in the package. Due to the addition of two layers, the 10-layer substrate thickness is increased by 0.1mm. Both the 8-layer and 10-layer meet the maximum package outline height specification.

### Q3. What is the effect in performance, power, or thermal characteristics?

A. There is no negative impact to any of these characteristics.

# Q4. The migration from 8-layer to 10-layer packages must result in different package pin delay and skew figures. How is the package skew affected in the new packages?

A. There is no pin delay impact; consequently, there is no additional skew due to the package layer count change. The conversion from 8-layer to 10-layer did not involve any I/O signal routing changes, because the two added layers are power/ground plane layers. I/O signal routing lengths and pin delay remain the same as before.

#### Q5. Do you have the qualification data for the new package?

A. The qualification report (RPT091) for the new 10-layer flip-chip package substrate for Virtex-5 is available at: Qualification of 10-Layer Flip-Chip Package Substrate for Virtex-5 (RPT091)

# Q6. The LX220 and LX330 have packages with more than 1000 pins, but they are not listed in the PCNs. Are they not transitioning to 10-layer packages?

A. The LX220 and LX330 were qualified with both 8-layer and 10-layer packages before going into production. Those devices are shipping with either the 8-layer or 10-layer packages since their Production release in October 2007.

© Copyright 2007 - 2009 Xilinx, Inc. All Rights Reserved. XILINX, the Xilinx logo, the Brand Window and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

# Q7. Is there any associated or increased risk in continuing to use the 8-layer package in Production designs?

A. No. All Virtex-5 packages have been carefully designed to reduce cost and complexity for the user, while still delivering excellent electrical properties. For example, the 8-layer (and 10-layer) packages include a wideband decoupling network and group power pins in clusters to ease board-level power distribution. Previous device families (Virtex-4, Virtex-II Pro, etc.) required an extensive PCB decoupling network as package capacitors could only cover a limited frequency range. Virtex-5 is the first device family that contains a wideband decoupling network inside the package. Since only bulk low-frequency capacitors are required at the PCB level, there are fewer PCB decoupling capacitors, with little restriction on capacitor placement and performance. The Virtex-5 pin-out was carefully designed to cluster similar supply pins into consolidated groups. This makes it possible to reach the vias of all power pins of a given supply with only a small  $V_{\rm CC}$  planelet. The shapes of these planelets can fit into one another, which was not possible in older device families. What would have required 3  $V_{\rm CC}$  layers in another device can be done with only 1 or 2  $V_{\rm CC}$  layers in a Virtex-5 package.

### Q8. Do I have the option to order 8-layer packages only?

A. No. After April 30, 2008, Xilinx will ship either 8-layer or 10-layer packages. There will be no separate ordering code for 8-layer packages.

# Q9. Do I need to specifically order 10-layer packages alone?

A. No. Xilinx expects that the current packages would work well for most applications. The new 10-layer packages only benefit limited applications where extra noise margin is required. The qualification report on the new 10-layer package is available at: Qualification of 10-Layer Flip-Chip Package Substrate for Virtex-5 (RPT091).

# Q10. Has there been any 10-layer devices shipped with the standard ordering part number so far?

A. Except for the LX220 and LX330 devices, all orders for standard ordering parts are shipped using 8-layer packages until April 30, 2008. After April 30, 2008 (following the XCN07025 transition period), orders for standard ordering parts will be shipped with either 8-layer or 10-layer packages.

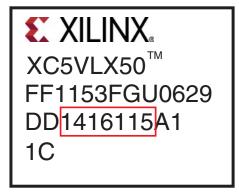

#### Q11. How do I know whether I have the new 10-layer package?

A. To trace the packages in your possession, please contact Xilinx Customer Service at <a href="mailto:csgroup@xilinx.com">csgroup@xilinx.com</a>, and provide the 7- digit Lot ID (see example top mark below). Xilinx Customer Service can identify if the order was shipped with 8-layer or 10-layer packages.

XTP027 01 061009

Q12. I would like to understand whether or not my existing application will benefit from moving to the 10-layer package. Whom should I contact for additional information regarding the 10-layer package construction?

A. For assistance in evaluating the effects of using the 10-layer package in your application, contact Xilinx Technical Support.

# **Revision History**

| Date     | Version | Revision                                                                                                                                                                                                                                           |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02/08/08 | 1.0     | Initial release.                                                                                                                                                                                                                                   |

| 06/15/09 | 1.0.1   | Minor edits to ensure these FAQs only apply to XCN07025. Corrected the image to include new logo and document date. Added the correct trademark symbol for Virtex-5 in the document. Revised links to RPT091 (links to secure URL) in the document |

## **Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED ON THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

XTP027 (v1.0.1) June 15, 2009