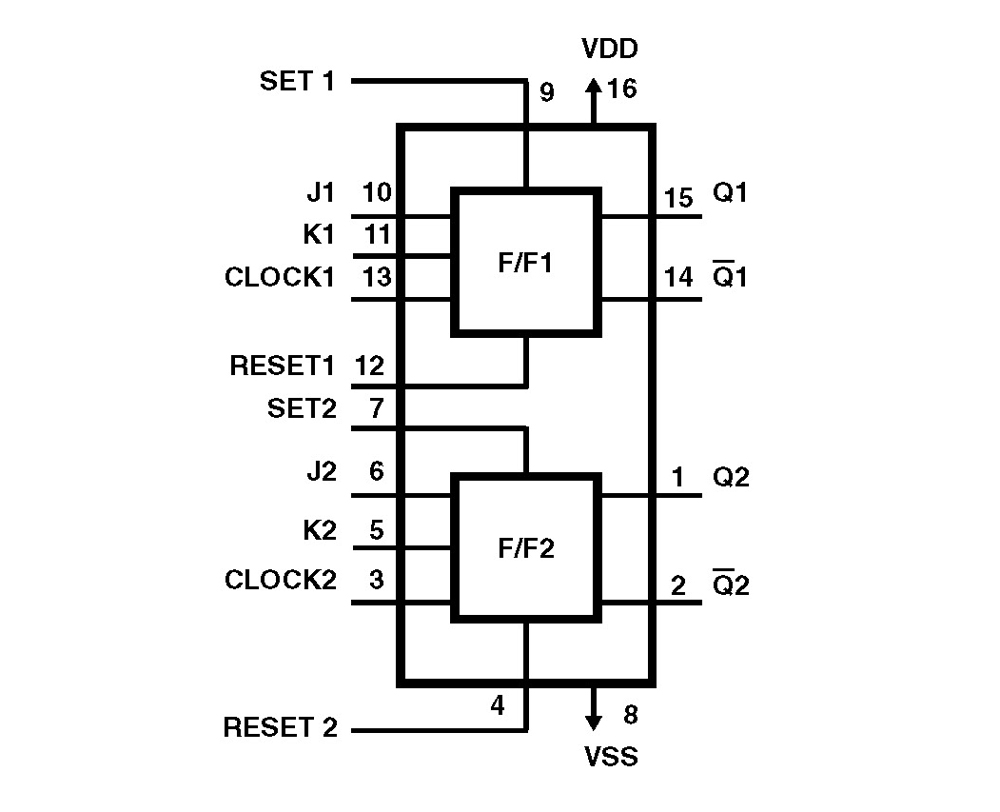

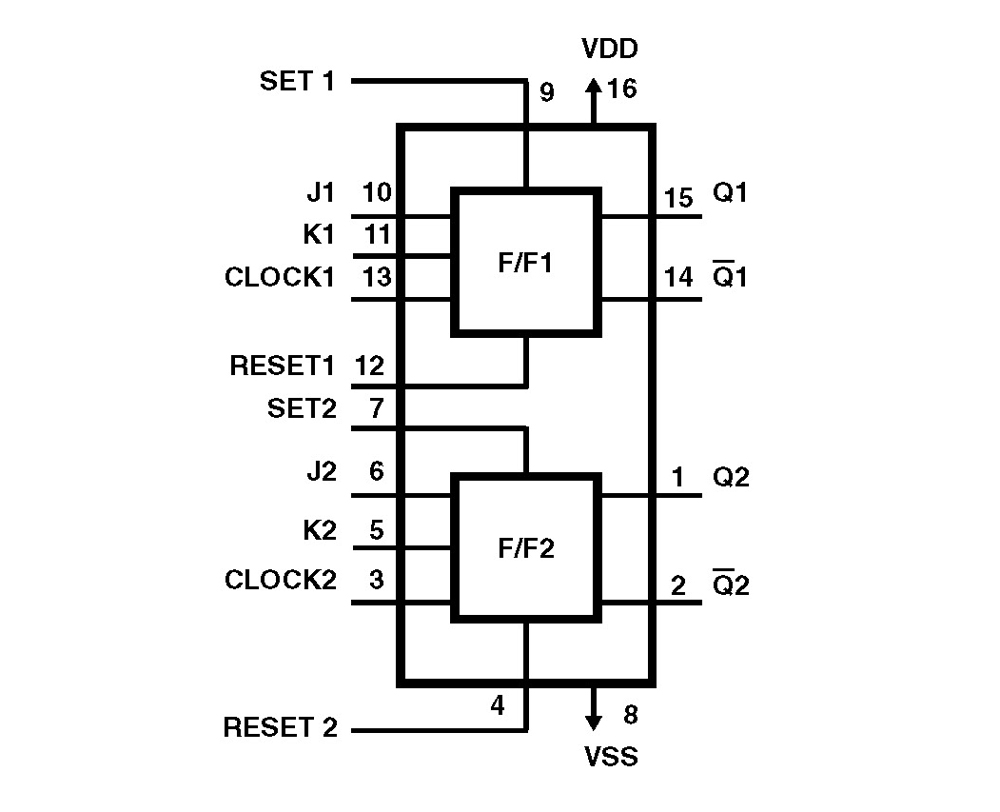

CD4027BMS is a single monolithic chip integrated circuit containing two identical complementary-symmetry J-K masterslave flip-flops. Each flip-flop has provisions for individual J, K, Set Reset, and Clock input signals. Buffered Q and Q signals are provided as outputs. This input-output arrangement provides for compatible operation with the Intersil CD4013B dual D type flip-flop.

The CD4027BMS is useful in performing control, register, and toggle functions. Logic levels present at the J and K inputs along with internal self-steering control the state of each flip- flop; changes in the flip-flop state are synchronous with the positive-going transition of the clock pulse. Set and reset functions are independent of the clock and are initiated when a high level signal is present at either the Set or Reset input.

The CD4027BMS is supplied in these 16-lead outline packages:

Ceramic Flatpack H6W

Key Features

- High Voltage Type (20V Rating)

- Set - Reset Capability

- Static Flip-Flop Operation - Retains State Indefinitely with Clock Level Either "High" or "Low"

- Medium Speed Operation - 16MHz (typ.) Clock Toggle Rate at 10V

- Standardized Symmetrical Output Characteristics

- 100% Tested For Quiescent Current at 20V

- Maximum Input Current of 1µA at 18V Over Full Package-Temperature Range;

- Noise Margin (Over Full Package Temperature Range):

- 1V at VDD = 5V

- 2V at VDD = 10V

- 2.5V at VDD = 15V

- 5V, 10V and 15V Parametric Ratings

- Meets All Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

Applications

- Registers, Counters, Control Circuits

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| CD4027BKMSR | 16 Ld CFP | 0.59 | 16 | N/A | NA | RoHS |

|

|