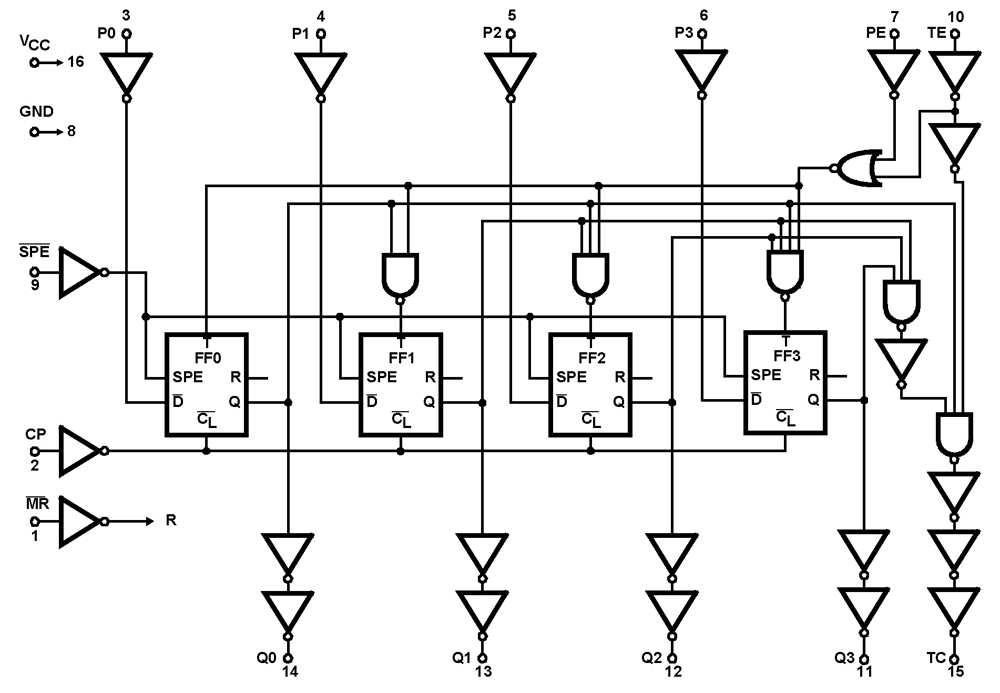

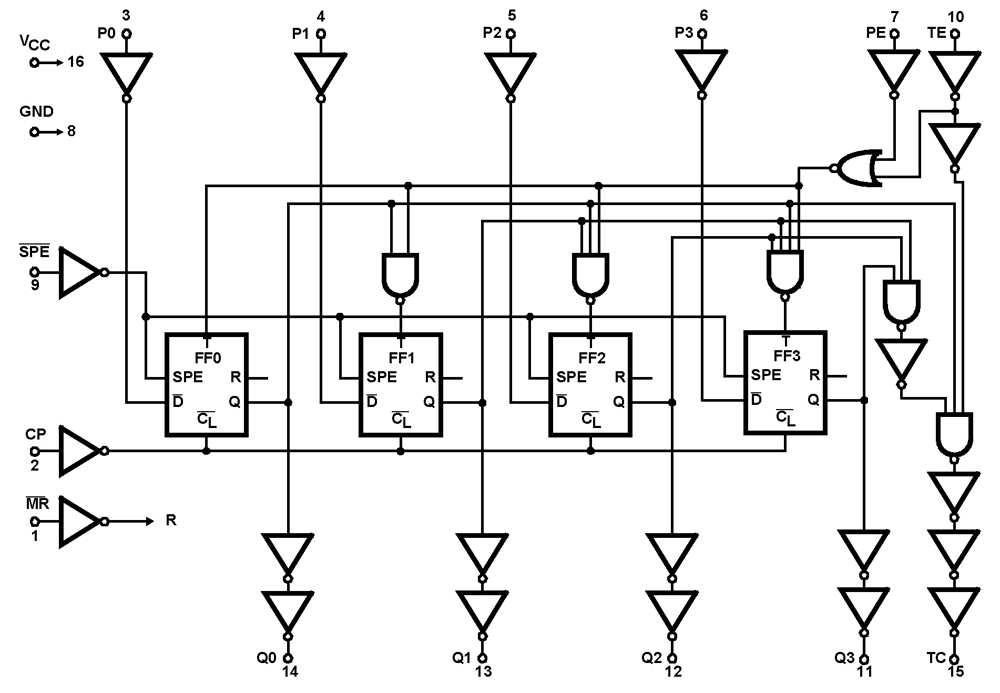

The Intersil HCS161MS is a Radiation Hardened 4-Input Binary; synchronous counter featuring asynchronous reset and lookahead carry logic. The HCS161 has an active-low master reset to zero, MR. A low level at the synchronous parallel enable, SPE, disables counting and allows data at the preset inputs (p0 - p3) to load the counter. The data is latched to the outputs on the positive edge of the clock input, CP. The HCS161MS has two count output, IC. The terminal count output indicates a maximum count for one clock pulse and is used to enable the next cascaded stage to count.

The HCS161MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened, high-speed, CMOS/SOS Logic Family.

The HCS161MS is supplied in a 16 lead Ceramic flatpack (K suffix) or a SBDIP Package (D suffix).

Key Features

- 3 Micron Radiation Hardened SOS CMOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/Bit-Day (Typ)

- Dose Rate Survivability: >1 x 1012 RAD (Si)/s

- Dose Rate Upset >1010 RAD (Si)/s 20ns Pulse

- Cosmic Ray Upset Immunity 2 x 10-9 Error/Bit Day (Typ)

- Latch-Up Free Under Any Conditions

- Military Temperature Range: -55oC to +125oC

- Significant Power Reduction Compared to LSTTL ICs

- DC Operating Voltage Range: 4.5V to 5.5V

- Input Logic Levels

- VIL = 0.3 VCC Max

- VIH = 0.7 VCC Min

- Input Current Levels Ii ≤ 5µA at VOL, VOH

Order Information| Part Number | Package Type | Weight(g) | Pins | MSL Rating | Peak Temp (°C) | RoHS Status |

|---|

|

| HCS161DMSR | 16 Ld SBDIP | 1.37 | 16 | N/A | NA | RoHS |

|

|

| HCS161HMSR | Not Applicable - Contact Us | | | N/A | | RoHS |

|

|

| HCS161KMSR | 16 Ld CFP | 0.59 | 16 | N/A | NA | RoHS |

|

|