HMC6001 Millimeterwave Receiver IC, 57 - 64 GHz

The HMC6001 is a complete mmWave superheterodyne receiver chip including LNA, image reject filter, RF to IF downconverter, IF filter, I/Q downconverter, and frequency synthesizer. The receiver operates from 57 to 64 GHz with up to 1.8 GHz of double sided modulation bandwidth. An integrated synthesizer provides tuning in 500 or 540 MHz step sizes depending on the choice of external reference clock. Support for a wide variety of modulation formats is provided through a universal analog baseband IQ interface. The receiver chip supports all single carrier WiGig modulations and optionally supports dedicated FSK/MSK modulation formats for lower cost and lower power serial data links without the need for high speed data converters. LNA and adjustable gain IF stages provide 6 dB typical noise figure with AGC support. Together with the HMC6000, a complete transmit/ receive chipset is provided for multi-Gbps operation in the unlicensed 60 GHz ISM band.

技术特性

- Support for IEEE Channel Plan

- Receiver Gain: 2 - 67 dB

- Noise Figure: 6.0 dB

- Integrated Image Reject Filter

- Integrated Frequency Synthesizer

- Programmable IF Gain Block

- Universal Analog I/Q Baseband

Interface

- Integrated AM and FM Demodulator

- Three-Wire Serial Digital Interface

- Die Size: 3.452 x 1.852 mm

应用领域 APPLICATION

- WiGig Single Carrier Modulations

- 60 GHz ISM Band Data Transmitter

- Multi-Gbps Data Communications

- High Definition Video Transmission

- RFID

|

技术指标

| Freq. (GHz) |

Function |

P1dB (dBm), NF (dB) |

Max Gain (dB) |

Gain Adjust (dB) |

Phase Noise @ 1 MHz Offset (dBc/Hz) |

Power Dissipation (W) |

Package |

| 57 - 64 |

60 GHz Integrated Receiver |

6 dB |

67 |

65 |

-86 |

0.61 |

Chip |

订购信息 Ordering Information

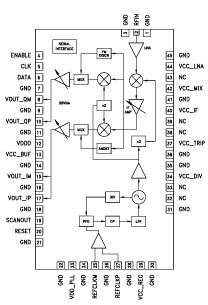

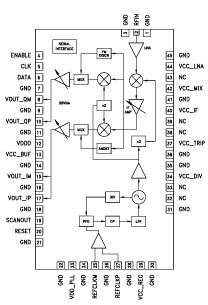

功能框图 Functional Block Diagram

|