HMC848LC5 45 Gbps 1:4 Demux SMT with Programmable Output Voltage

The HMC848LC5 is a 1:4 demultiplexer designed for data deserialization up to 45 Gbps. The device uses both rising and falling edges of the half-rate clock to sample the input data in sequence, D0-D3 and latches the data onto the differential outputs. A quarter-rate clock output generated on-chip can be used to clock the data into other devices. All clock and data inputs / outputs of the HMC848LC5 are CML and terminated on-chip with 50 Ohms to the VCC, and may be DC or AC coupled. The inputs and outputs of the HMC848LC5 may be operated either differentially or single-ended. The HMC848LC5 also features an output level control pin, VCTRL, which allows for loss compensation or signal level optimization. The HMC848LC5 operates from a single +3.3V supply and is available in ROHS compliant 5x5 mm SMT package.

技术特性

- Supports Data Rates up to 45 Gbps

- Half Rate Clock Input

- Quarter Rate Reference Clock Output

- Fast Rise and Fall Times: 25 / 21 ps

- Programmable Differential Output

Voltage Swing: 300 - 1000 mVp-p

- Single Supply: +3.3V

- 32 Lead 5x5mm SMT Package: 25mm²

订购信息 Ordering Information

应用领域 APPLICATION

- SONET OC-768

- RF ATE Applications

- Broadband Test & Measurement

- Serial Data Transmission

up to 45 Gbps

- High Speed ADC Interfacing

|

技术指标

Data/

Clock Rate (Gbps/GHz) |

Function |

Rise/Fall Time

(ps) |

Diff. Output Swing (Vp-p) |

DC Power Consumption (mW) |

DC Power Supply (Vdc) |

Package |

| 45 / 22.5 |

1:4 Demux w/ Adj. Vout |

25 / 21 |

0.3 - 1.0 |

1782 |

+3.3 |

LC5 |

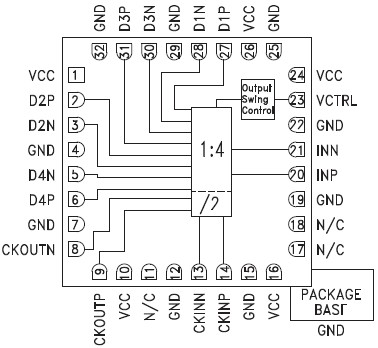

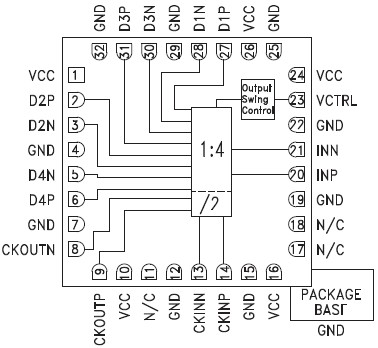

功能框图 Functional Block Diagram

|