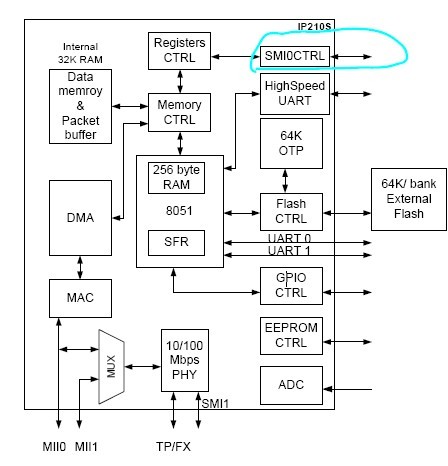

IP210S Serial to Ethernet Controller

The IP210S is a very cost effective and highly integrated SoC(System-on-Chip).The embedded Ethernet transceiver, 64k bytes OTP, 32K bytes SRAM, 8-channel 8-bit ADC, 10/100Mbps Ethernet MAC/PHY, offload engine and 8051 support IP210S can be applied for variety applications such as Serial-to-Ethernet convertor, network sensor, remote control/monitoring, automatic test equipment and consumer electronics. The IP210S can support program running with embedded 64KB OTP ROM or external Flash memory for more flexible application. Since device drivers, network protocol stack and Ethernet offload engine are embedded inside the SoC, this design provides a neat and cost-effective solution. In addition to TP cable connection, the IP210S also provides the fiber cable connection to meet the requirement of long distance communication

特性

- Embeds a 8051

- Includes 32KB SSRAM and 64KB OTP ROM

- Includes a 10/100 Ethernet MAC, Etherent PHY

- Includes a 4-channel DMA

- Includes a 8-bits 8-channel ADC(0V~2.5V)

- Supports CPU boot from bank0 0x0000 or 0xFFFD

- Includes external Flash I/F to extend code size by using external program memory ( Support 512KB and 2MB)

- Includes one MII/reverse MII or RMII

- Support two MII (MII0: MAC mode & PHY mode, MII1: PHY mode)

- Includes one SMI(MDC/MDIO)

- Provides I 2C for EEPROM access

- Includes 3 timers

- two 8-bit hardware auto load timers

- one 16-bit hardware auto load timer

- Includes 2 hardware WatchDog timer

- Includes a high speed (up to 921Kbps) UART (with MODEM control signals) and two simplified UART(Tx, Rx only)

- Supports fiber cable connection

- 0.25um CMOS technology

- 2.5V core and 3.3V IO power

- 128-pin PQFN package

IP210S 技术资料

- IP210S 数据手册下载.pdf

IP210S 功能原理图